# SEMICONDUCTOR BASICS

A qualitative, non-mathematical explanation of

how semiconductors work and how they are used

George Domingo

WILEY

# Table of Contents

[Cover](#)

[Acknowledgements](#)

[Introduction](#)

[1 The Bohr Atom](#)

[1.1 Sinusoidal Waves](#)

[1.2 The Case of the Missing Lines](#)

[1.3 The Strange Behavior of Spectra from Gases and Metals](#)

[1.4 The Classifications of Basic Elements](#)

[1.5 The Hydrogen Spectrum Lines](#)

[1.6 Light is a Particle](#)

[1.7 The Atom's Structure](#)

[1.8 The Bohr Atom](#)

[1.9 Summary and Conclusions](#)

[Appendix 1.1 Some Details of the Bohr Model](#)

[Appendix 1.2 Semiconductor Materials](#)

[Appendix 1.3 Calculating the Rydberg Constant](#)

[2 Energy Bands](#)

[2.1 Bringing Atoms Together](#)

[2.2 The Insulator](#)

[2.3 The Conductor](#)

[2.4 The Semiconductor](#)

[2.5 Digression: Water Analogy](#)

[2.6 The Mobility of Charges](#)

[2.7 Summary and Conclusions](#)

[Appendix 2.1 Energy Gap in Semiconductors](#)

[Appendix 2.2 Number of Electrons and the Fermi Function](#)

[3 Types of Semiconductors](#)

[3.1 Semiconductor Materials](#)

[3.2 Short Summary of Semiconductor Materials](#)

[3.3 Intrinsic Semiconductors](#)

[3.4 Doped Semiconductors: n-Type](#)

[3.5 Doped Semiconductors: p-Type](#)

[3.6 Additional Considerations](#)

[3.7 Summary and Conclusions](#)

[Appendix 3.1 The Fermi Levels in Doped Semiconductors](#)

[Appendix 3.2 Why All Donor Electrons go to the Conduction Band](#)

[4 Infrared Detectors](#)

[4.1 What is Infrared Radiation?](#)

[4.2 What Our Eyes Can See](#)

[4.3 Infrared Applications](#)

[4.4 Types of Infrared Radiation](#)

[4.5 Extrinsic Silicon Infrared Detectors](#)

[4.6 Intrinsic Infrared Detectors](#)

[4.7 Summary and Conclusions](#)

[Appendix 4.1 Light Diffraction](#)

[Appendix 4.2 Blackbody Radiation](#)

[5 The pn-Junction](#)

[5.1 The pn-Junction](#)

[5.2 The Semiconductor Diode](#)

[5.3 The Schottky Diode](#)

[5.4 The Zener or Tunnel Diode](#)

[5.5 Summary and Conclusions](#)

[Appendix 5.1 Fermi Levels of a pn-Junction](#)

[Appendix 5.2 Diffusion and Drift Currents](#)

[Appendix 5.3 The Thickness of the Transition Region](#)

[Appendix 5.4 Work Function and the Schottky Diode](#)

[6 Other Electrical Components](#)

[6.1 Voltage and Current](#)

[6.2 Resistance](#)

[6.3 The Capacitor](#)

[6.4 The Inductor](#)

[6.5 Sinusoidal Voltage](#)

[6.6 Inductor Applications](#)

[6.7 Summary and Conclusions](#)

[Appendix 6.1 Impedance and Phase Changes](#)

[7 Diode Applications](#)

[7.1 Solar Cells](#)

[7.2 Rectifiers](#)

[7.3 Current Protection Circuit](#)

[7.4 Clamping Circuit](#)

[7.5 Voltage Clipper](#)

[7.6 Half-wave Voltage Doubler](#)

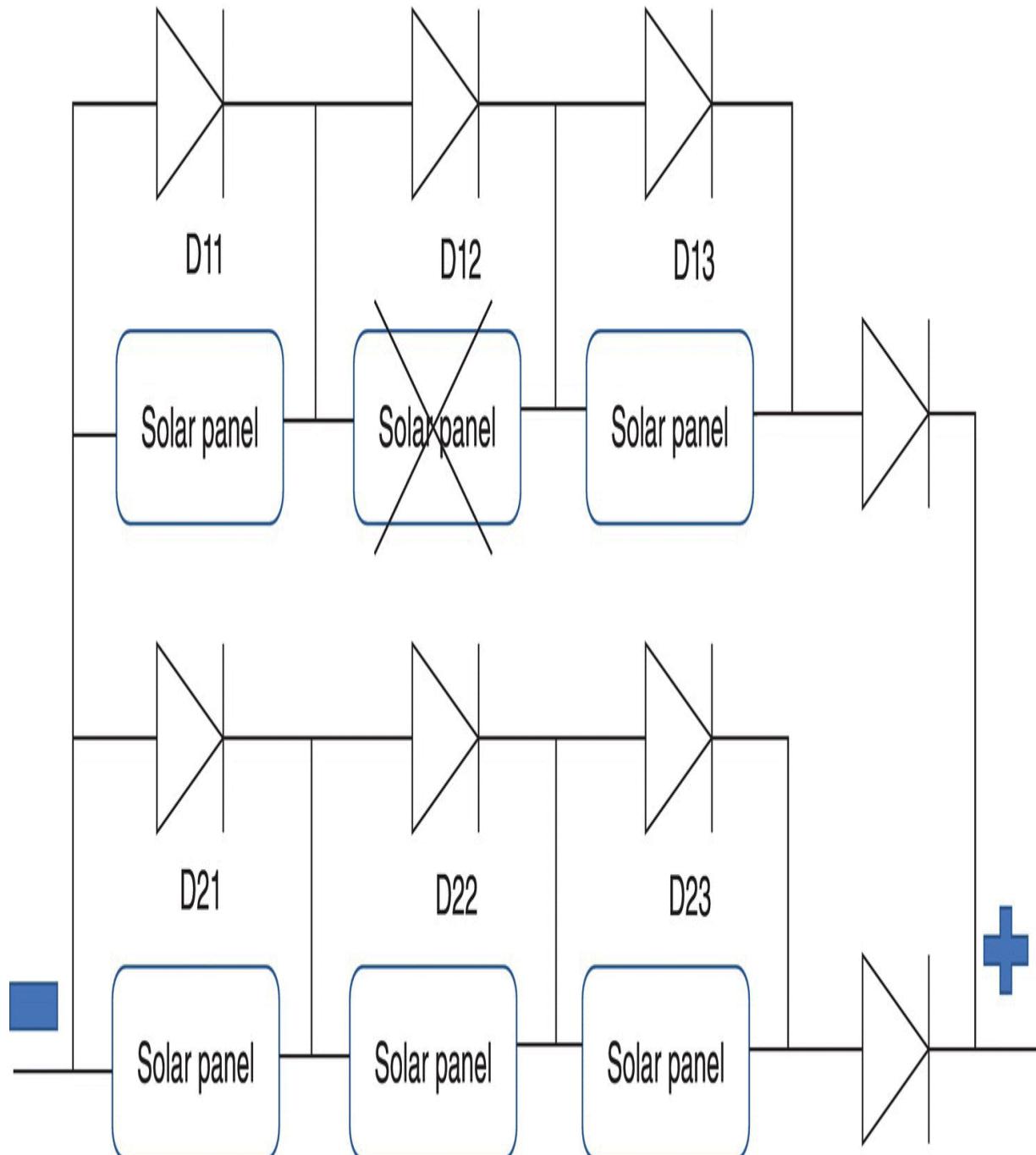

[7.7 Solar Cells Bypass Diodes](#)

[7.8 Applications of Schottky Diodes](#)

[7.9 Applications of Zener Diodes](#)

[7.10 Summary and Conclusions](#)

[Appendix 7.1 Calculation of the Current Through an RC Circuit](#)

[8 Transistors](#)

[8.1 The Concept of the Transistor](#)

[8.2 The Bipolar Junction Transistor](#)

[8.3 The Junction Field-effect Transistor](#)

[8.4 The Metal Oxide Semiconductor FET](#)

[8.5 Summary and Conclusions](#)

[Appendix 8.1 Punch Trough](#)

[9 Transistor Biasing Circuits](#)

[9.1 Introduction](#)

[9.2 Emitter Feedback Bias](#)

[9.3 Sinusoidal Operation of a Transistor with Emitter Bias](#)

[9.4 The Fixed Bias Circuit](#)

[9.5 The Collector Feedback Bias Circuit](#)

[9.6 Power Considerations](#)

[9.7 Multistage Transistor Amplifiers](#)

[9.8 Operational Amplifiers](#)

[9.9 The Ideal OpAmp](#)

[9.10 Summary and Conclusions](#)

[Appendix 9.1 Derivation of the Stability of the Collector Feedback Circuit](#)

[10 Integrated Circuit Fabrication](#)

[10.1 The Basic Material](#)

[10.2 The Boule](#)

[10.3 Wafers and Epitaxial Growth](#)

[10.4 Photolithography](#)

[10.5 The Fabrication of a pnp Transistor on a Silicon Wafer](#)

[10.6 A Digression on Doping](#)

[10.7 Resume the Transistor Processing](#)

[10.8 Fabrication of Other Components](#)

[10.9 Testing and Packaging](#)

[10.10 Clean Rooms](#)

[10.11 Additional Thoughts About Processing](#)

## 10.12 Summary and Conclusions

## Appendix 10.1 Miller Indices in the Diamond Structure

## 11 Logic Circuits

### 11.1 Boolean Algebra

### 11.2 Logic Symbols and Relay Circuits

### 11.3 The Electronics Inside the Symbols

### 11.4 The Inverter or NOT Circuit

### 11.5 The NOR Circuit

### 11.6 The NAND Circuit

### 11.7 The XNOR or Exclusive NOR

### 11.8 The Half Adder

### 11.9 The Full Adder

### 11.10 Adding More than Two Digital Numbers

### 11.11 The Subtractor

### 11.12 Digression: Flip-flops, Latches, and Shifters

### 11.13 Multiplication and Division of Binary Numbers

### 11.14 Additional Comments: Speed and Power

### 11.15 Summary and Conclusions

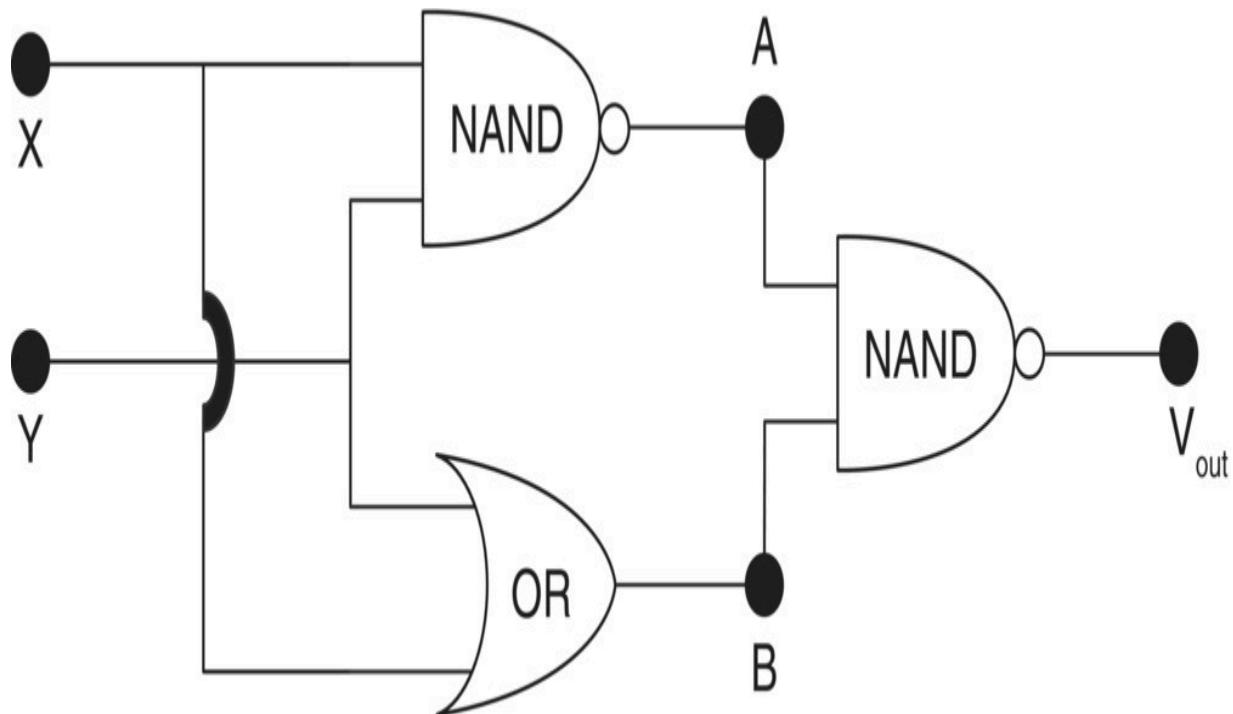

## Appendix 11.1 Algebraic Formulation of Logic Modules

## Appendix 11.2 Detailed Analysis of the Full Adder

## Appendix 11.3 Complementary Numbers

## Appendix 11.4 Dividing Digital Numbers

## Appendix 11.5 The Author's Symbolic Logic Machine Using Relays

## 12 VLSI Components

### 12.1 Multiplexers

### 12.2 Demultiplexers

### 12.3 Registers

### 12.4 Timing and Waveforms

[12.5 Memories](#)

[12.6 Gate Arrays](#)

[12.7 Summary and Conclusions](#)

[Appendix 12.1 A NAND implementation of a 2 to 1 MUX](#)

[13 Optoelectronics](#)

[13.1 Photoconductors](#)

[13.2 PIN Diodes](#)

[13.3 LASERs](#)

[13.4 Light-emitting Diodes](#)

[13.5 Summary and Conclusions](#)

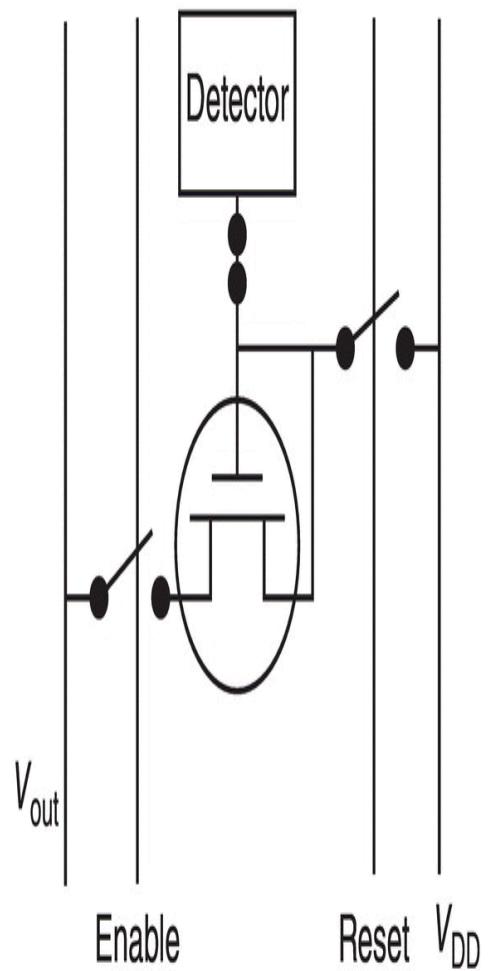

[Appendix 13.1 The Detector Readout](#)

[14 Microprocessors and Modern Electronics](#)

[14.1 The Computer](#)

[14.2 Microcontrollers](#)

[14.3 Liquid Crystal Displays](#)

[14.4 Summary and Conclusions](#)

[Appendix 14.1 Keyboard Codes](#)

[15 The Future](#)

[15.1 The Past](#)

[15.2 Problems with Silicon-based Technology](#)

[15.3 New Technologies](#)

[15.4 Silicon Technology Innovations](#)

[15.5 Summary and Conclusions](#)

[Epilogue](#)

[Appendix A: Useful Constants](#)

[A.1 Fundamental Physical Constants](#)

[A.2 Basic Units](#)

[A.3 Derived Units](#)

[Appendix B: Properties of Silicon](#)

[Appendix C: List of Acronyms](#)

[Additional Reading and Sources](#)

[Index](#)

[End User License Agreement](#)

## **List of Tables**

Chapter 3

[Table 3.1 The impurities allowed in an electronic grade silicon \(parts per bi...](#)

Chapter 4

[Table 4.1 Frequency, wavelength, and energy of photons in the four infrared r...](#)

Chapter 13

[Table 13.1 LED semiconductor materials used to obtain different colors](#)

Chapter 14

[Table 14.1 The ASCII code.](#)

## **List of Illustrations**

Chapter 1

[Figure 1.1 A sinusoidal wave is described in several ways: frequency, wavele...](#)

[Figure 1.2 William Wollaston \(left\) looked at the sun's light through a pris...](#)

[Figure 1.3 The sun's spectrum through a prism shows dark lines: wavelengths ...](#)

[Figure 1.4 The spectrum from any gas shows similar but different missing lin...](#)

[Figure 1.5 Dmitri Mendeleev and the periodic table with the elements known i...](#)

[Figure 1.6 The spectrum of the hydrogen atom on the left shows the absorptio...](#)

[Figure 1.7 Johann Balmer \(left\) found a mathematical relation for hydrogen's...](#)

[Figure 1.8 Around 1905, Albert Einstein came up with the concept that light ...](#)

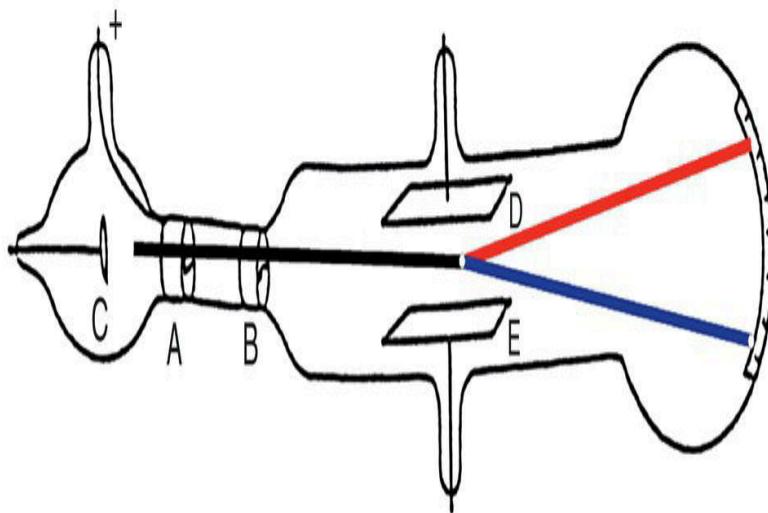

[Figure 1.9 Joseph John Thomson and his cathode ray tube.](#)

[Figure 1.10 Ernest Rutherford, with his experiment that bombarded alpha part...](#)

[Figure 1.11 Robert Millikan, with his oil-drop experiment, measured the elec...](#)

[Figure 1.12 Niels Bohr \(left\) postulated the planetary model of the atom. Wo...](#)

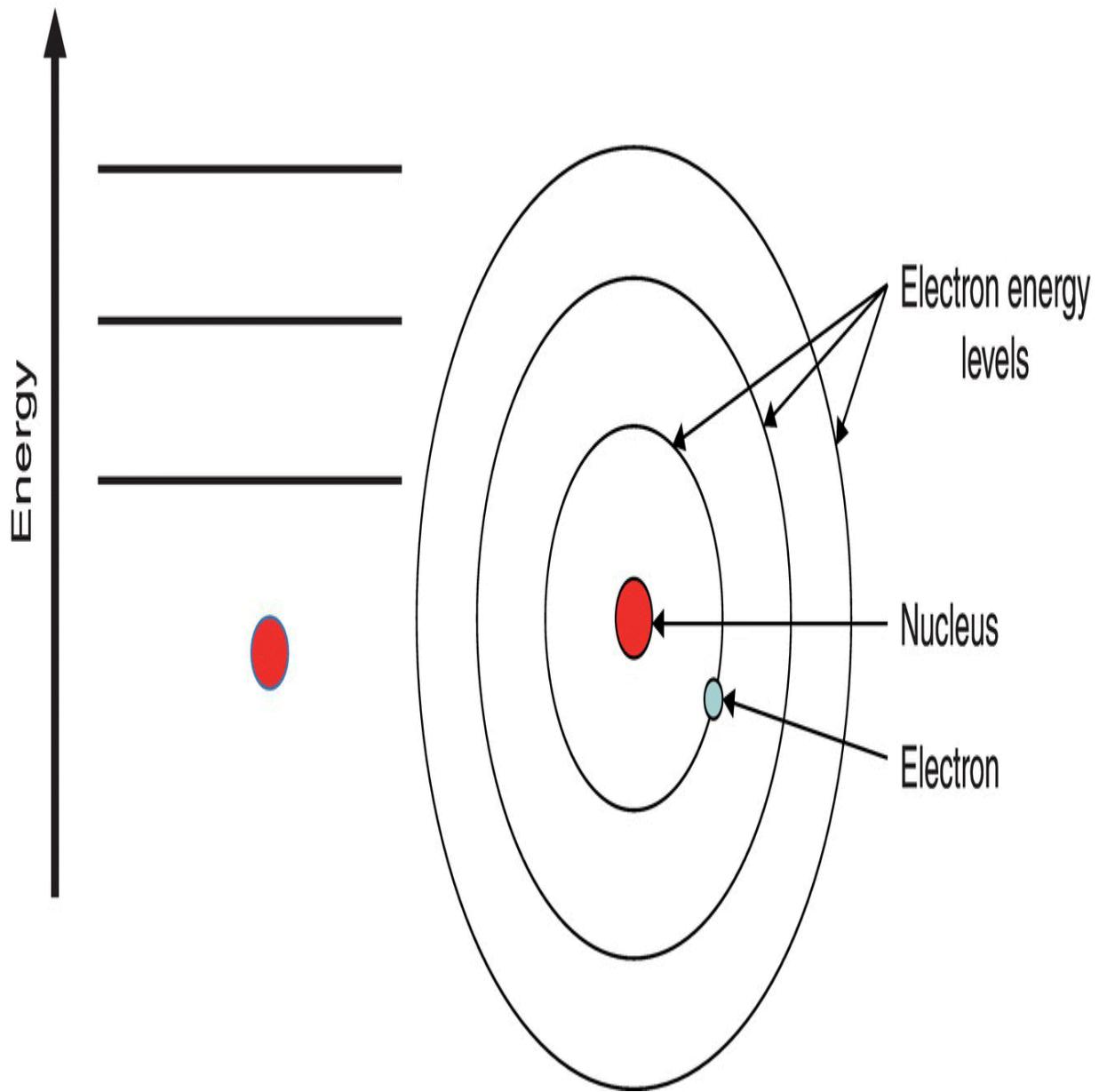

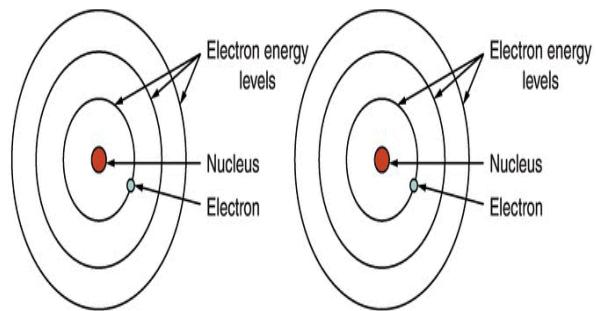

[Figure 1.13 The Bohr planetary model of an atom has discrete and stable orbi...](#)

[Figure 1.14 The observed energy lines of the hydrogen atom corresponding to ...](#)

[Figure 1.15 The scientific and experimental work that led to the Bohr planet...](#)

[Figure 1.16 Subshell electron capacity. Notice that the number of sites in e...](#)

[Figure 1.17 Portion of the periodic table emphasizing elements used in semic...](#)

Chapter 2

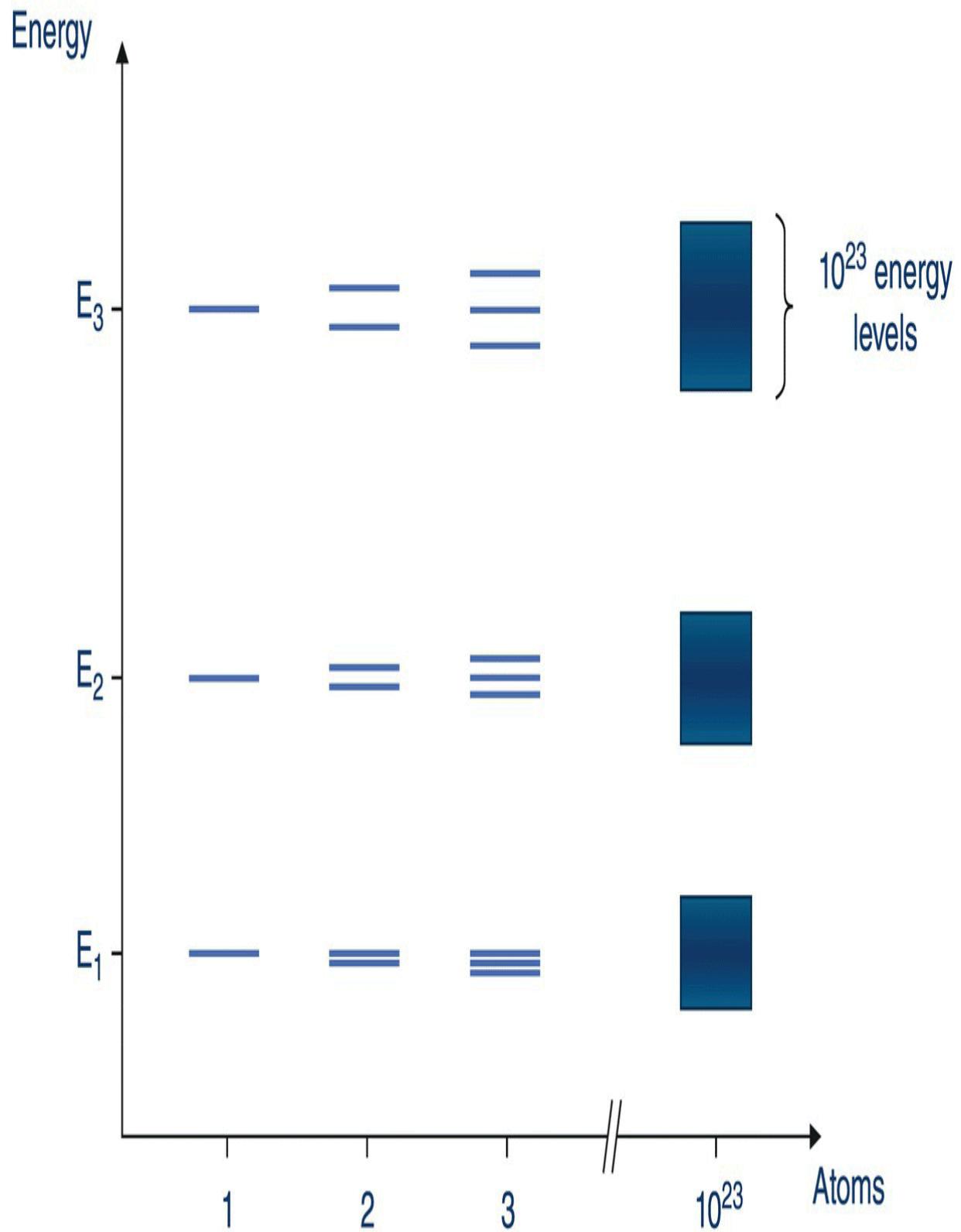

[Figure 2.1 Energy levels in a Bohr atom \(left\) corresponding to the Bohr ene...](#)

[Figure 2.2 When two hydrogen atoms are so close that they form a single syst...](#)

[Figure 2.3 From energy levels in a gas where the electrons in the atoms are ...](#)

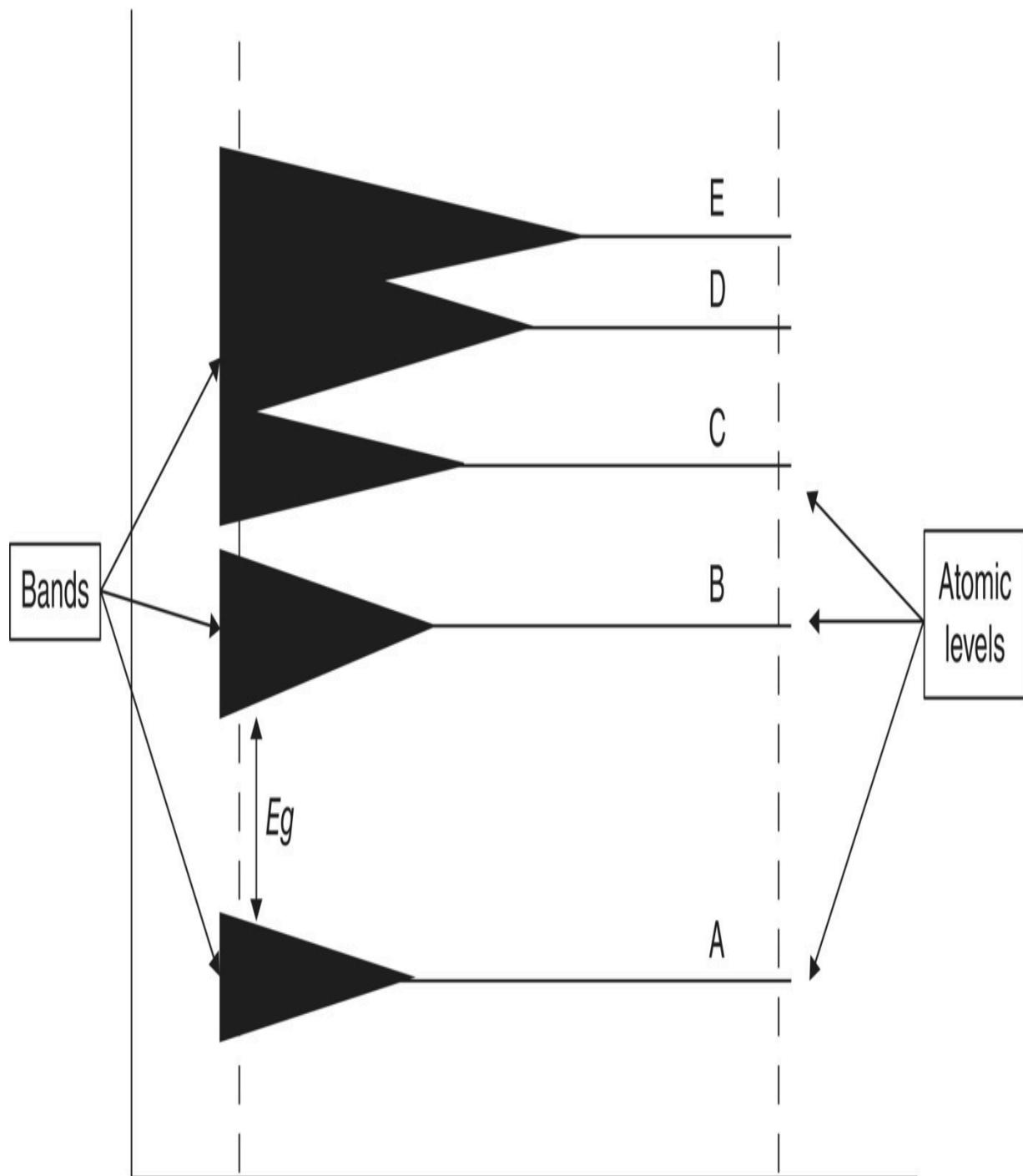

[Figure 2.4 Atomic levels split into bands as the interatomic distance betwee...](#)

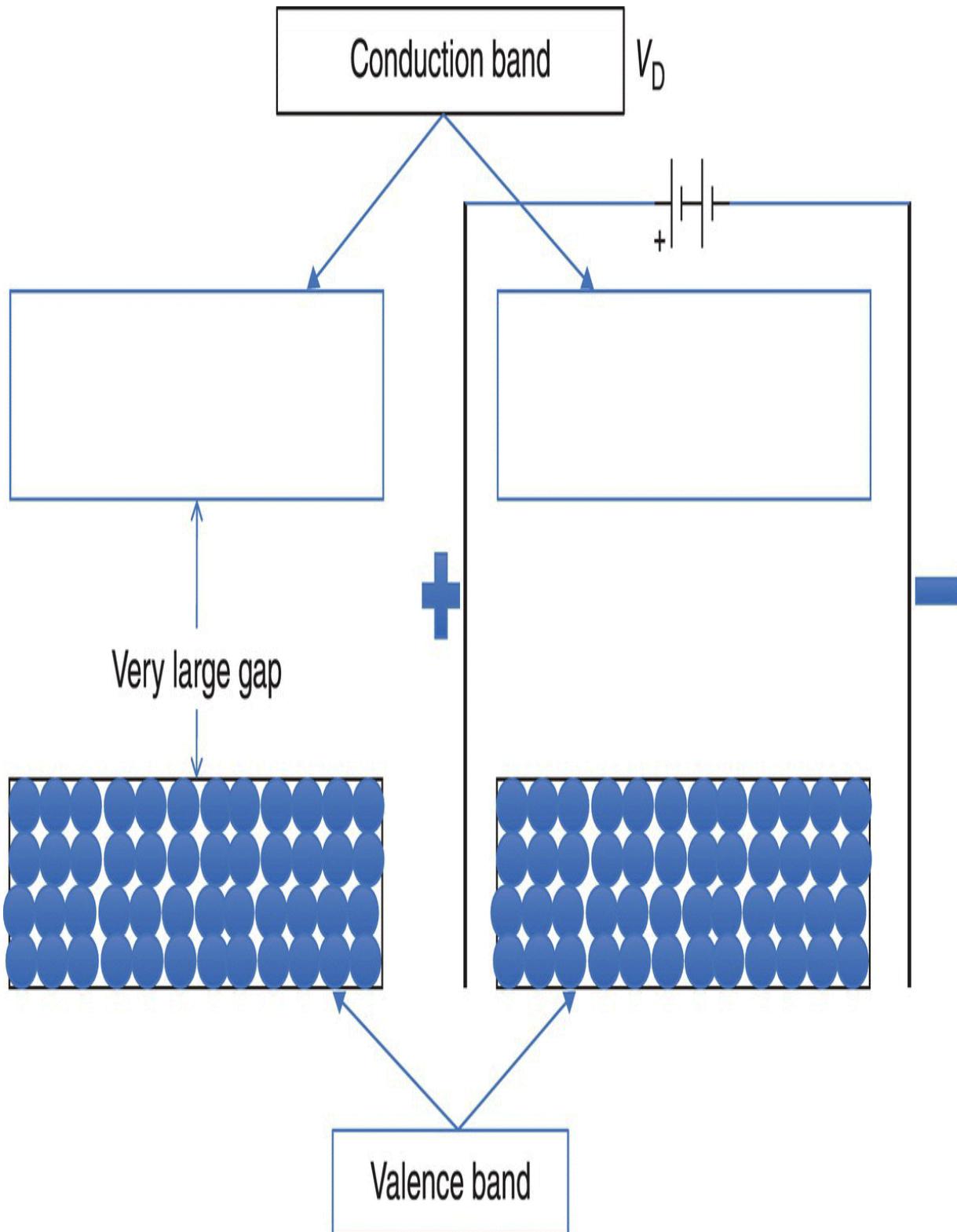

[Figure 2.5 In an insulator, the valence band is full of electrons, the condu...](#)

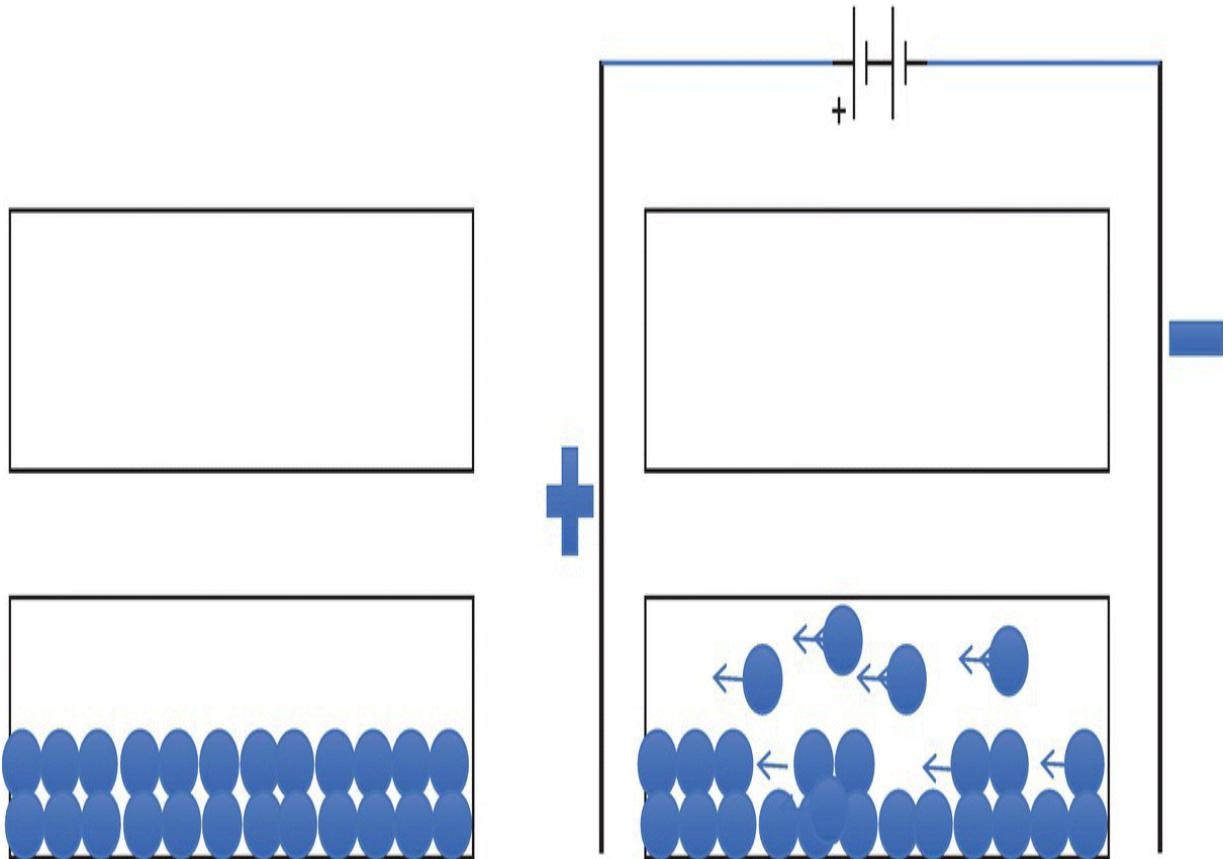

[Figure 2.6 If the valence band is not full of electrons, there is a lot of S...](#)

[Figure 2.7 Even if the valence band is full, if the conduction band encroach...](#)

[Figure 2.8 The valence band in a semiconductor is completely full, the condu...](#)

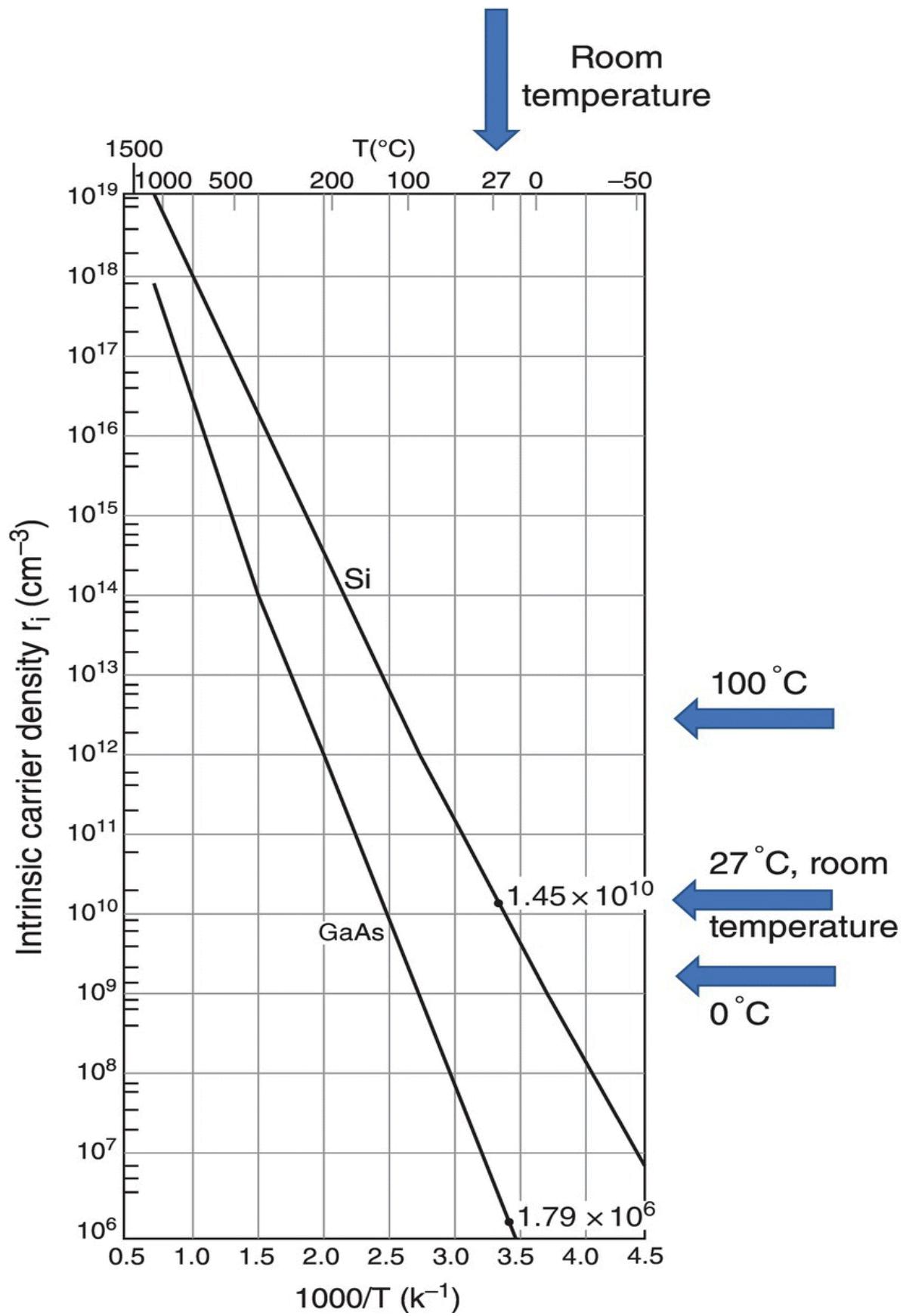

[Figure 2.9 Electron and hole concentrations in Si and GaAs change drasticall...](#)

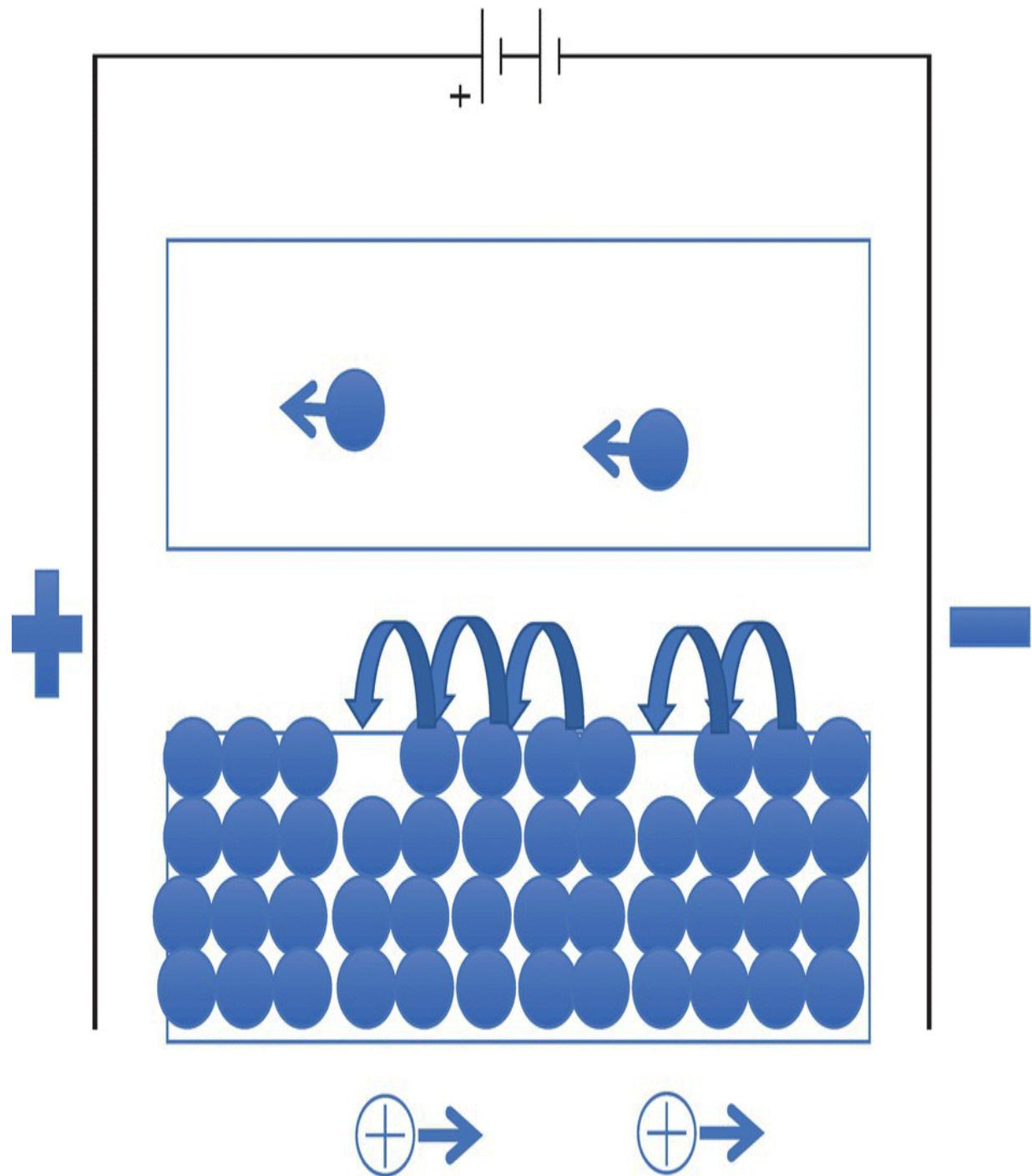

[Figure 2.10 Electrons in the conduction band are free to move, while those i...](#)

[Figure 2.11 There is a large difference in energy gaps in semiconductors, fr...](#)

[Figure 2.12 Enrico Fermi \(left\) and Paul Dirac \(right\), who developed the st...](#)

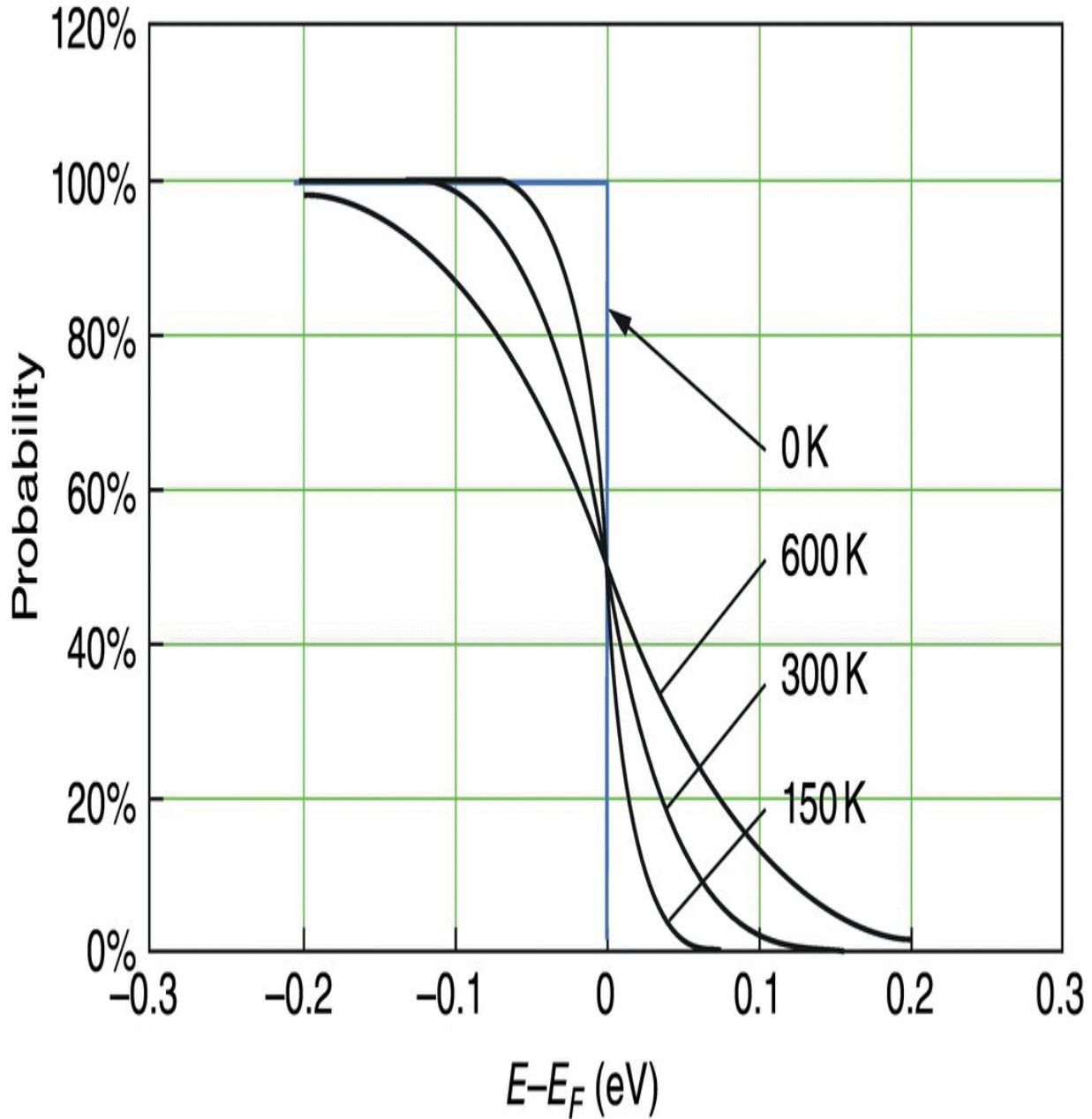

[Figure 2.13 The probability that electrons are free as a function of the dif...](#)

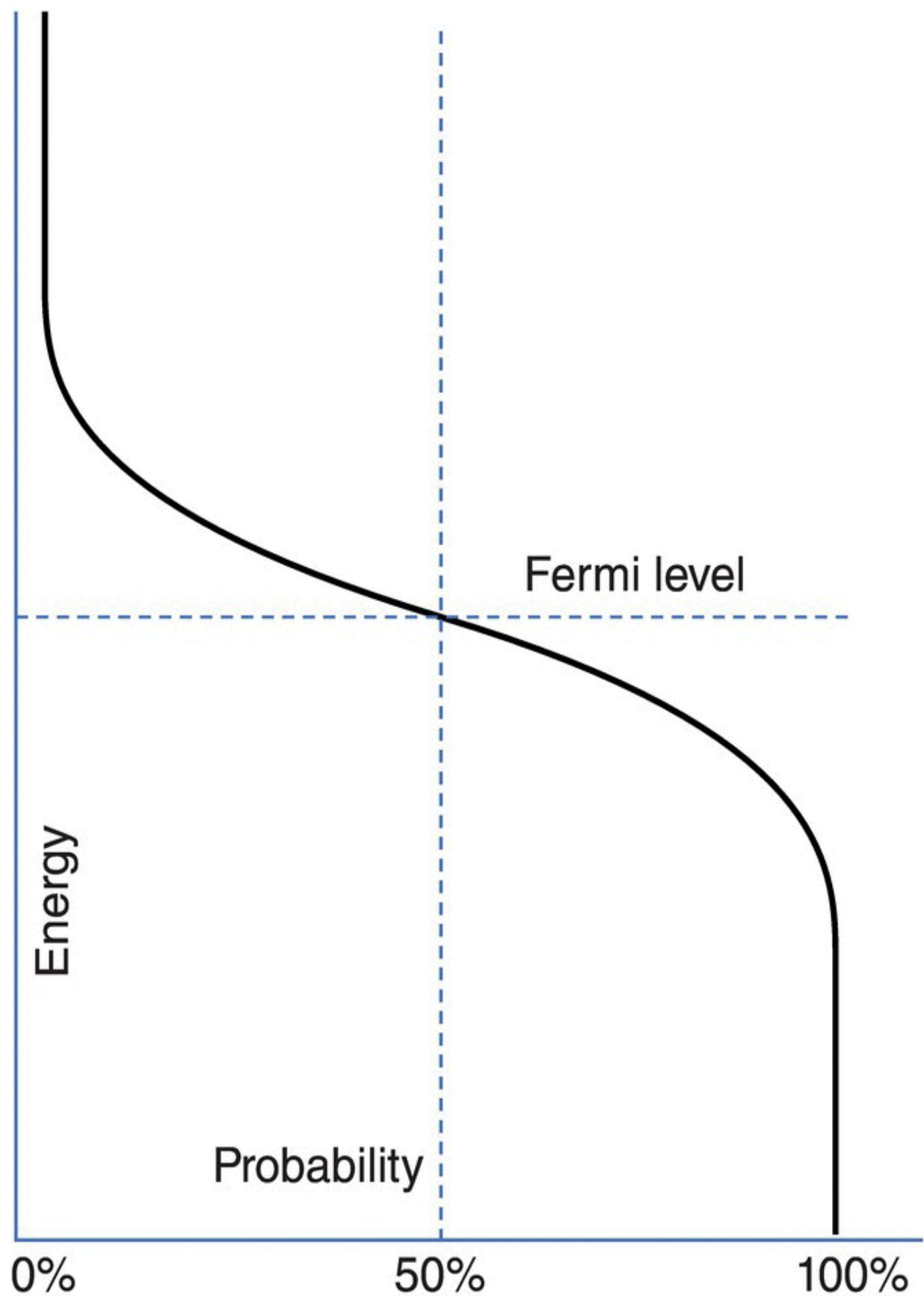

[Figure 2.14 The F-D function at room temperature.](#)

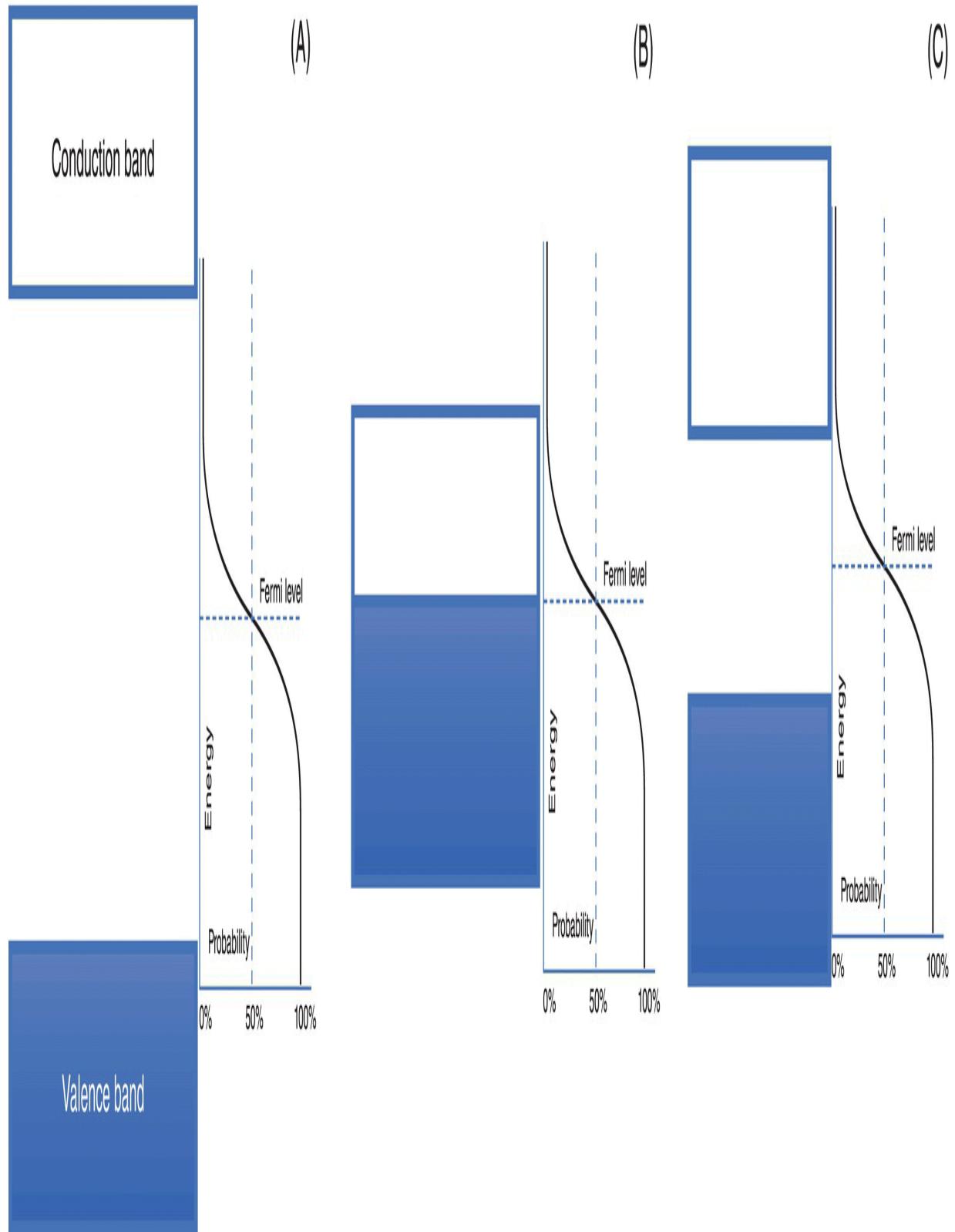

[Figure 2.15 The F-D functions on the side of the energy bands of insulators ...](#)

## Chapter 3

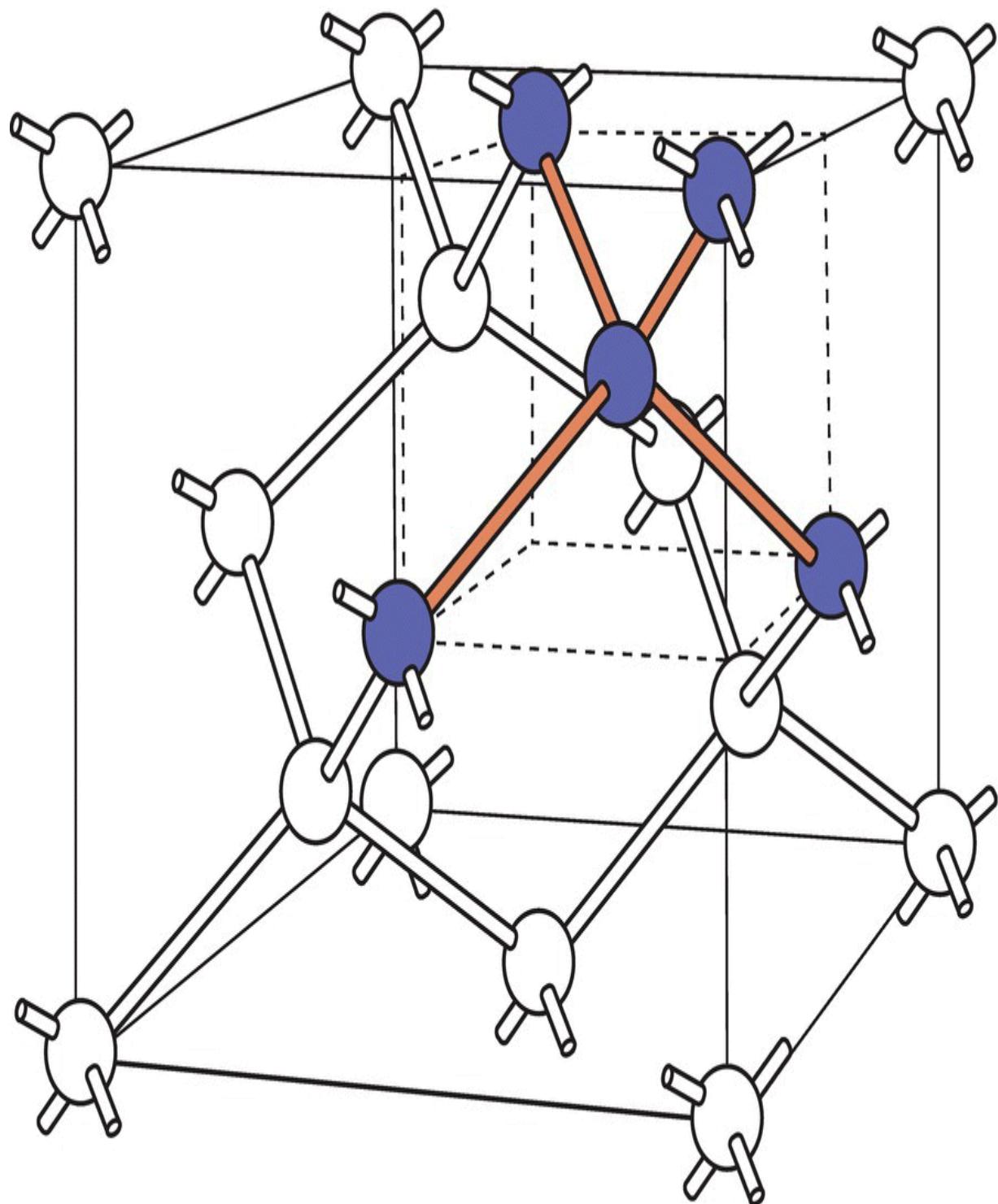

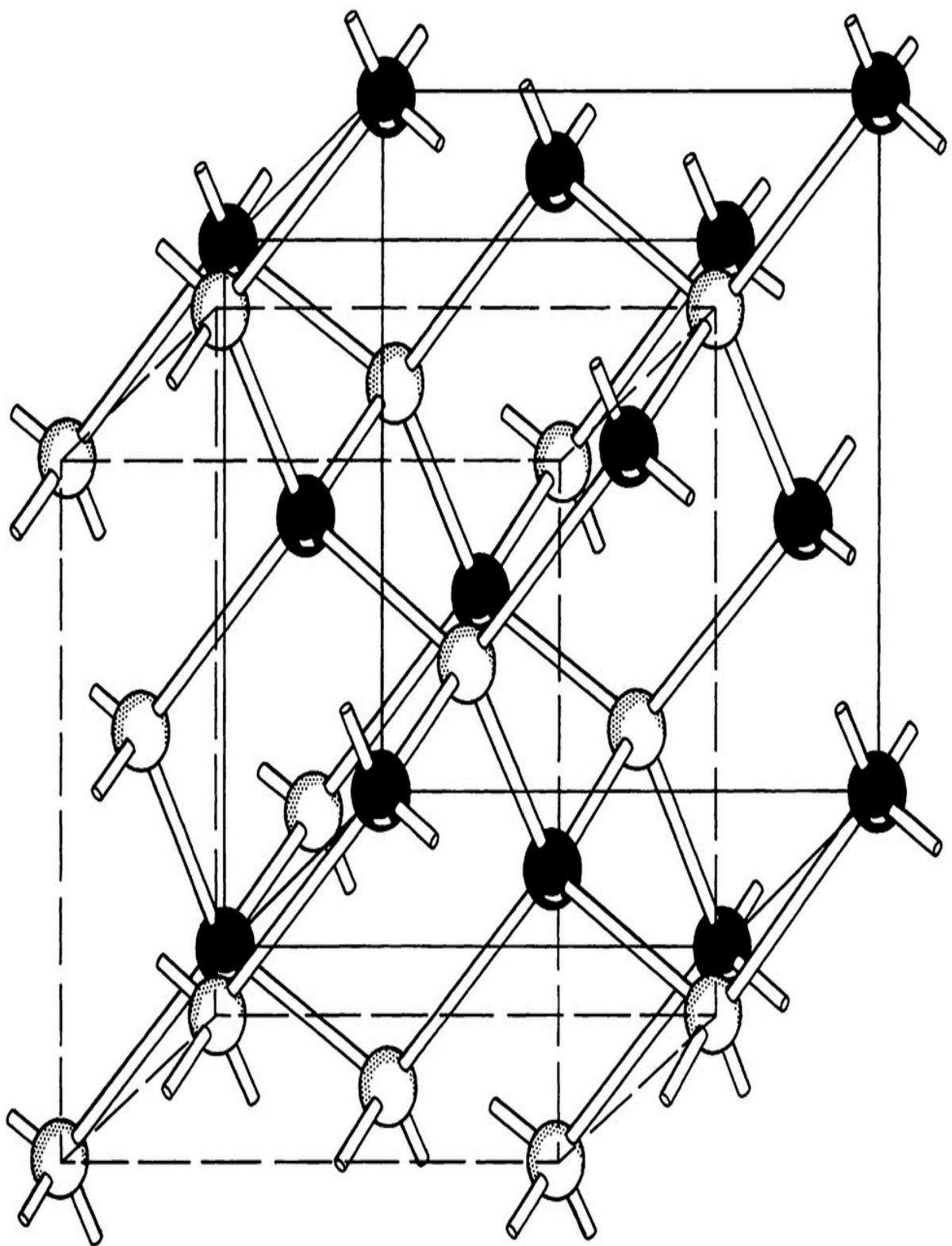

[Figure 3.1 Diamond crystal structure of silicon and germanium. The black bal...](#)

[Figure 3.2 Clemens Winkler, who discovered the element germanium.](#)

[Figure 3.3 John Bardeen, William Shockley, and Walter Brattain at Bell labs ...](#)

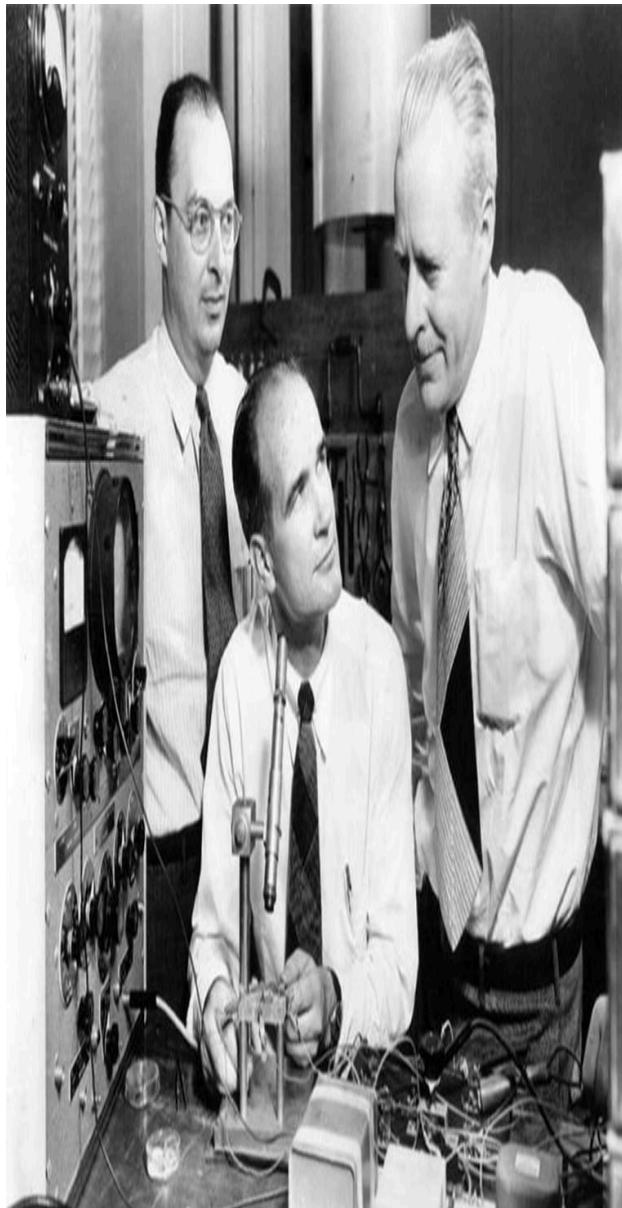

[Figure 3.4 The zincblende structure of GaAs is very similar to that of Si, t...](#)

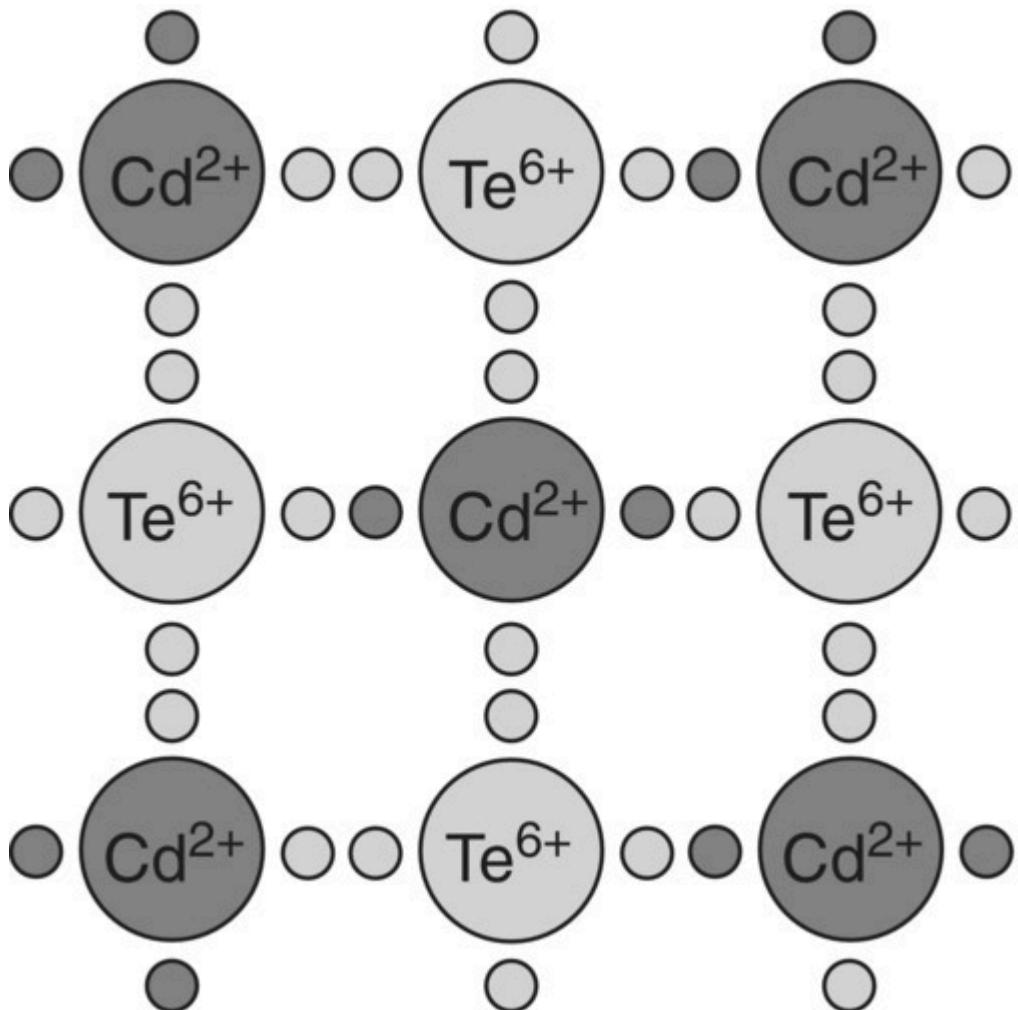

[Figure 3.5 The unit structure of CdTe shows how the cadmium, valence two, an...](#)

[Figure 3.6 The silicon atom has four electrons in the outer shell, shells 3s...](#)

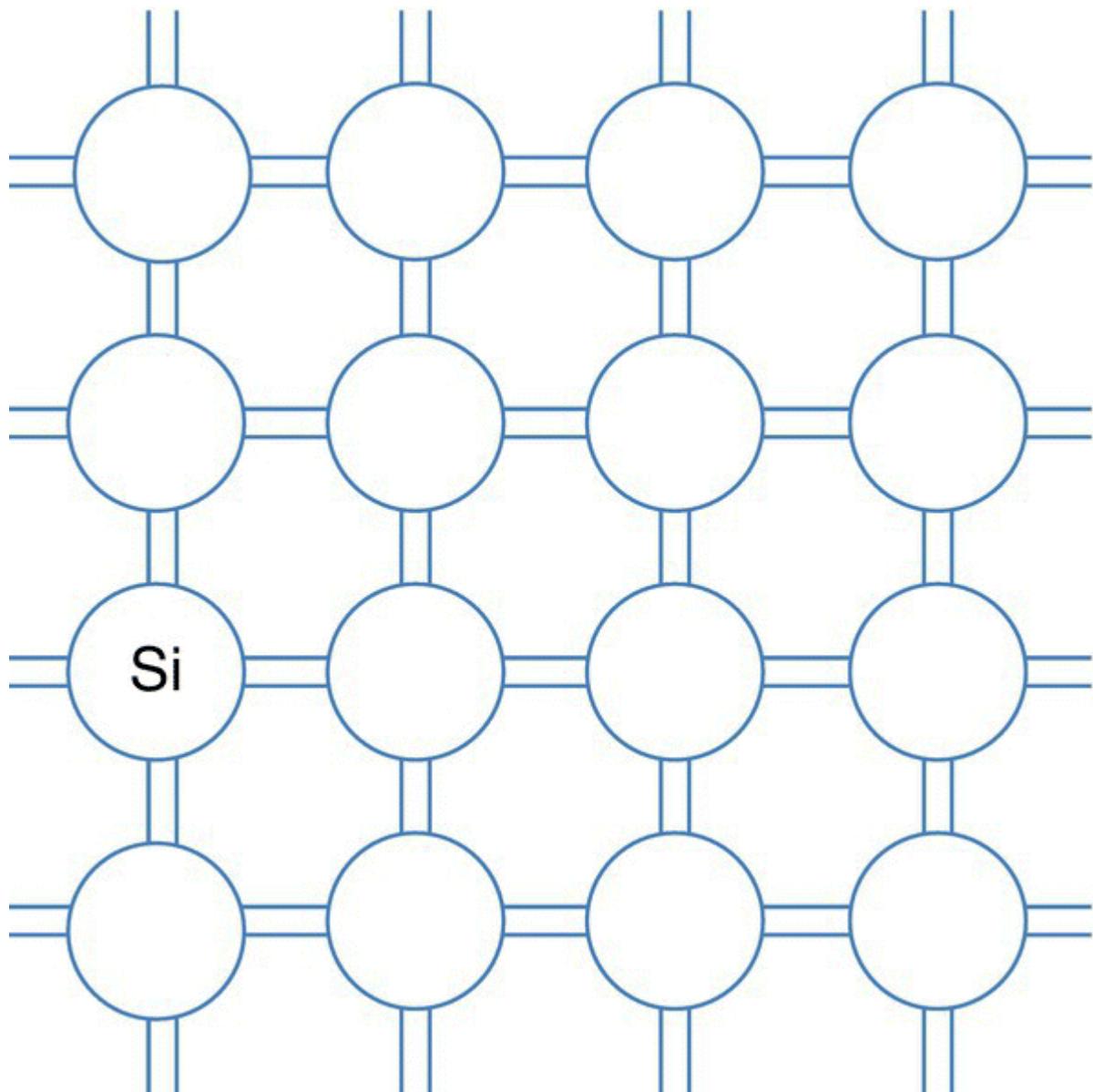

[Figure 3.7 A two-dimensional representation of the silicon crystal showing h...](#)

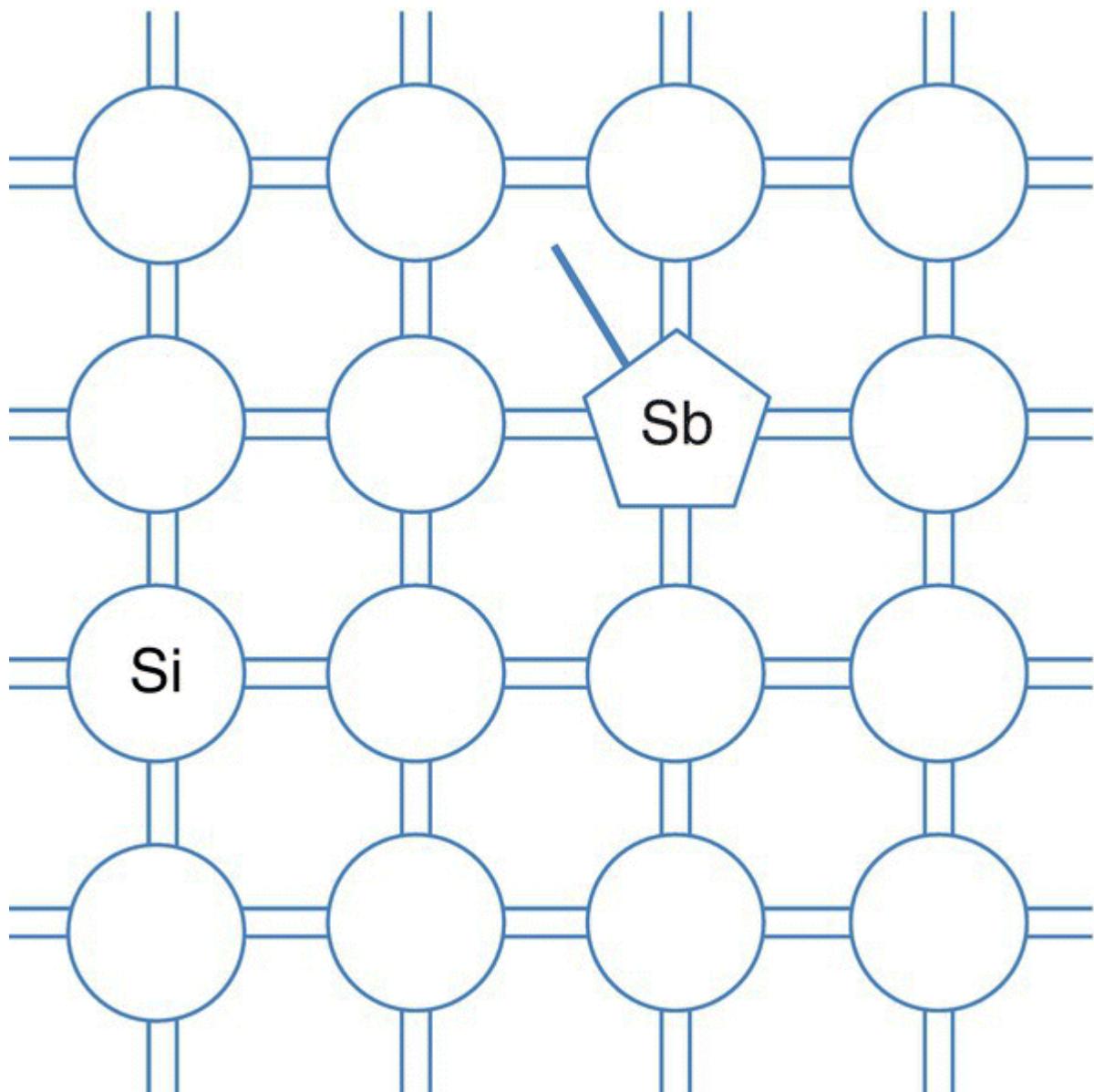

[Figure 3.8 A lonely Sb atom in a sea of Si atoms bonds to the surrounding Si...](#)

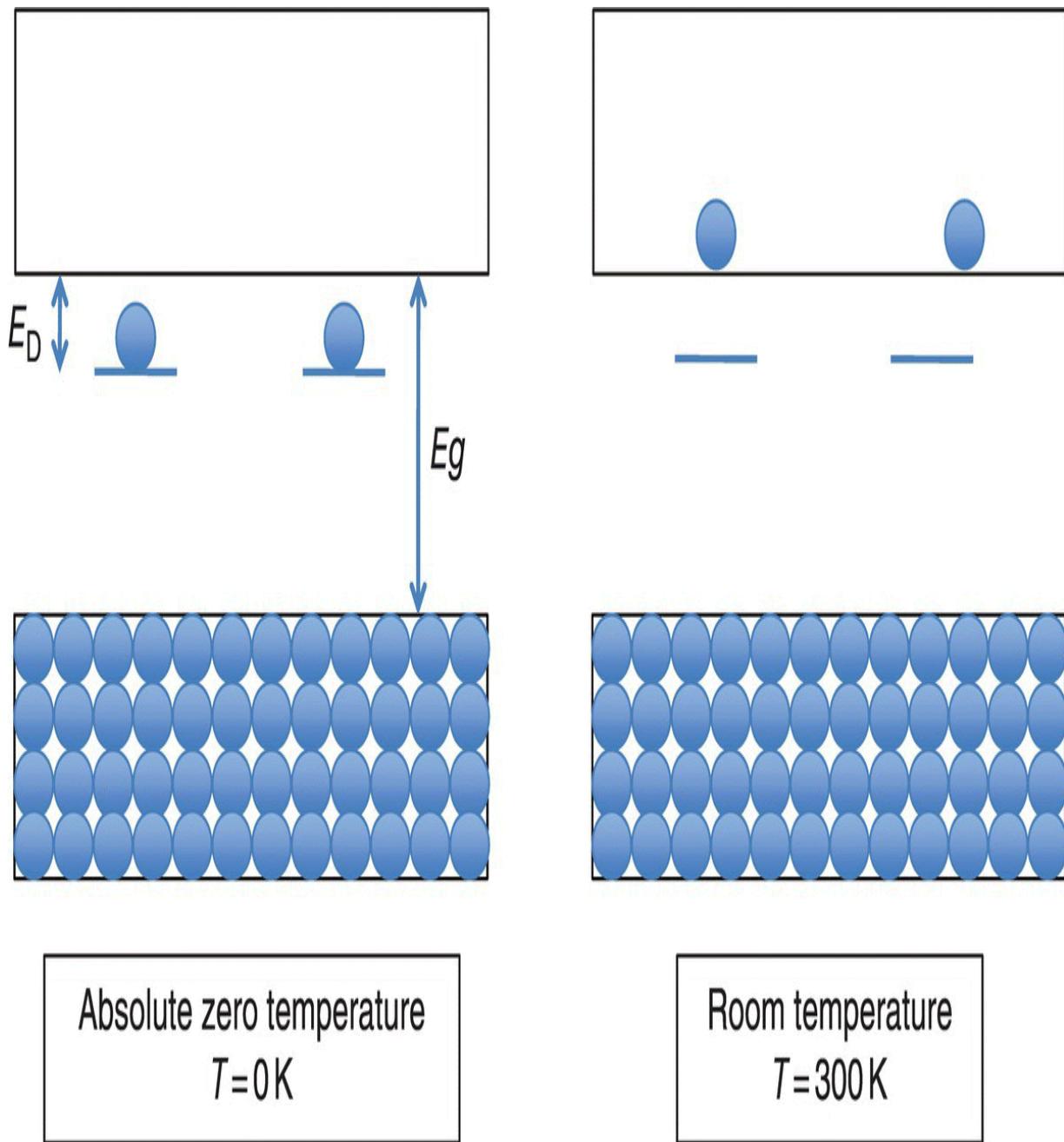

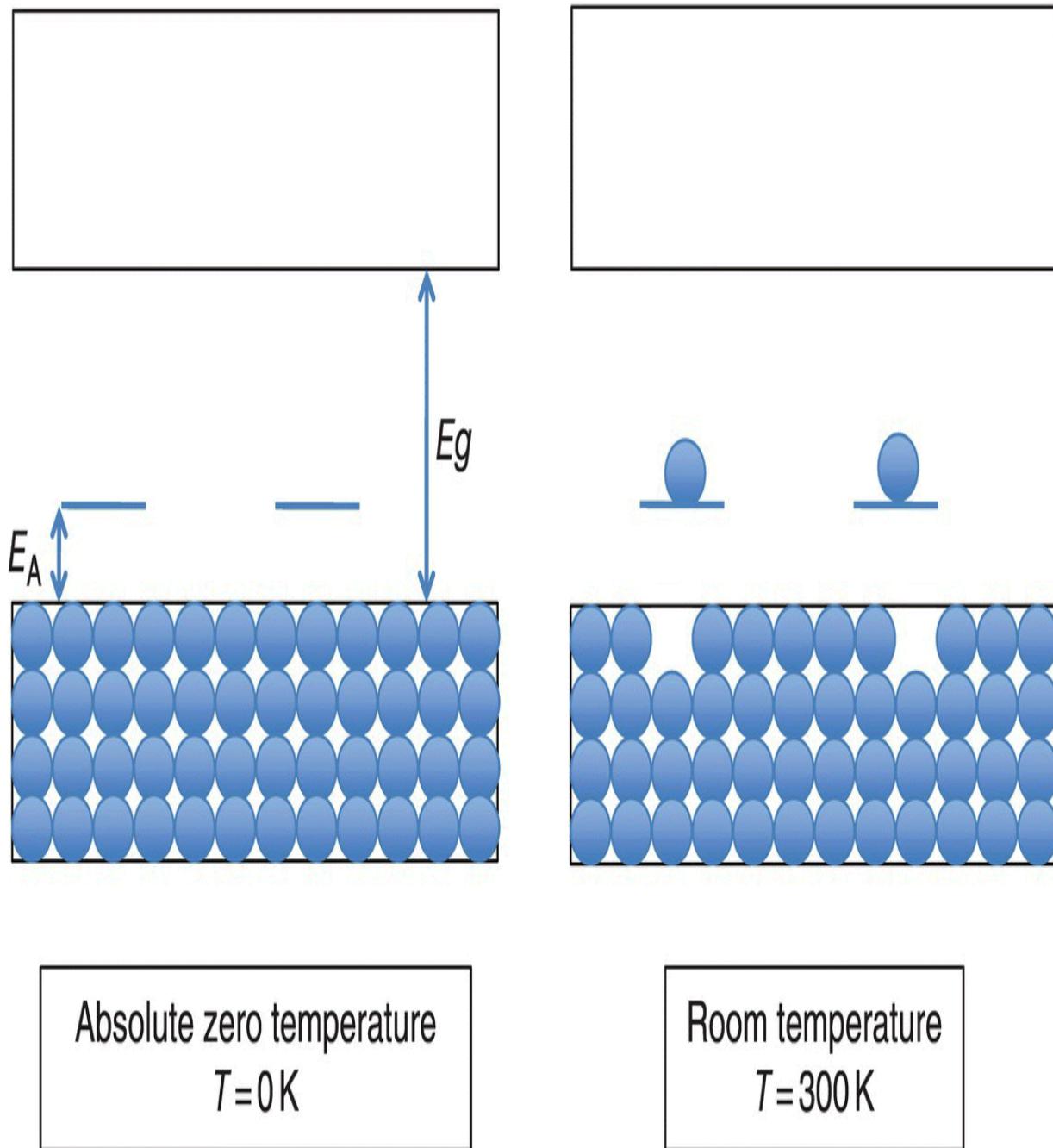

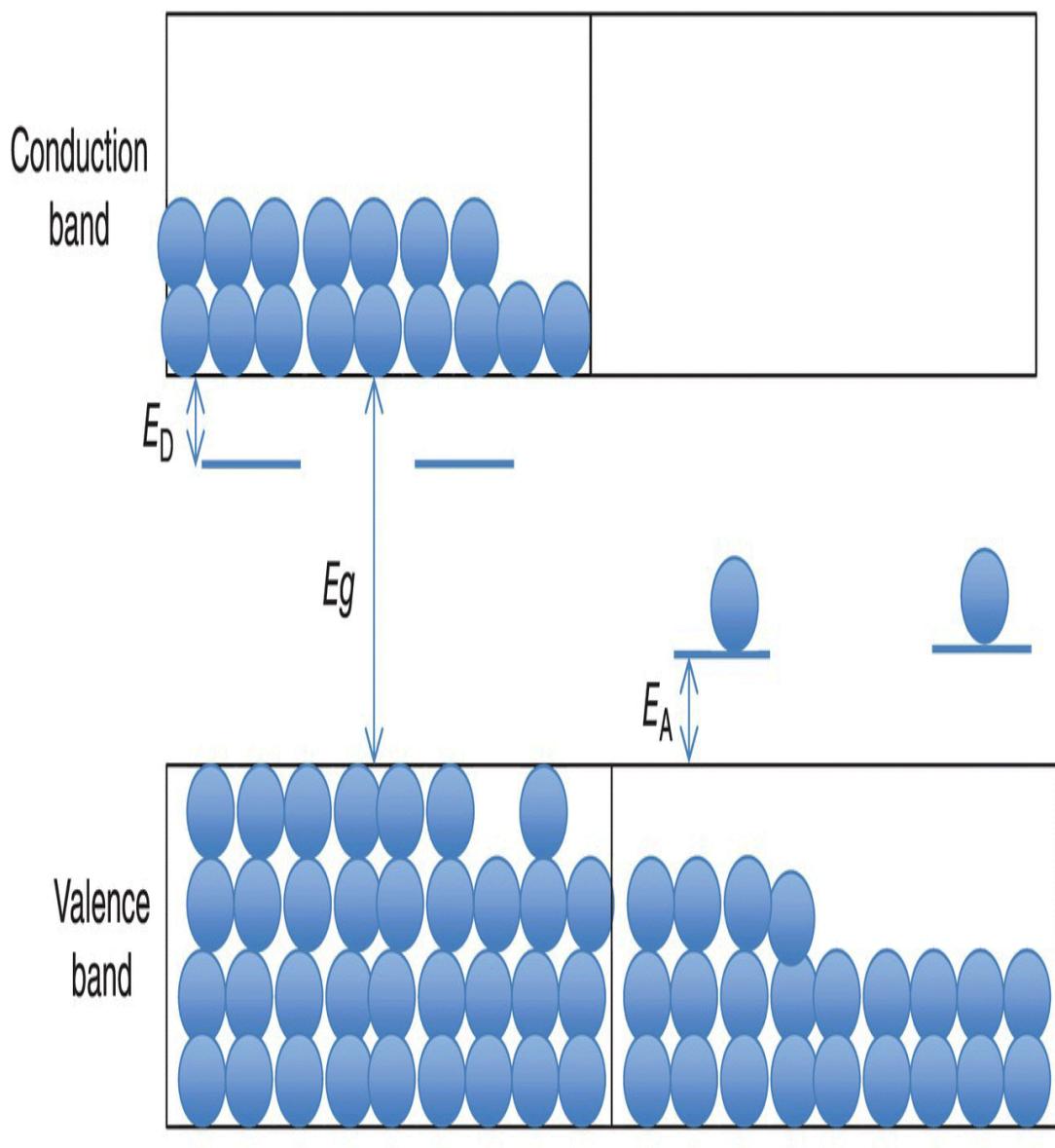

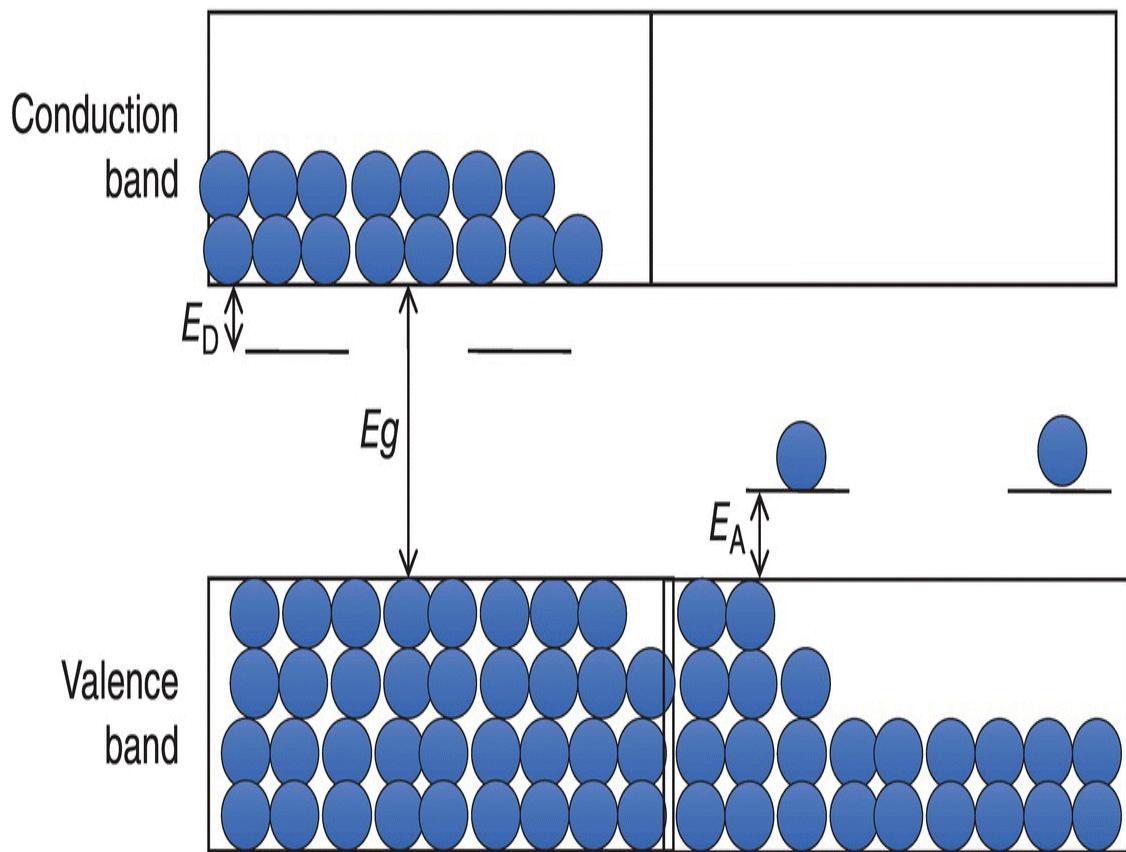

[Figure 3.9 Energy diagram of a semiconductor doped with donor atoms. At abso...](#)

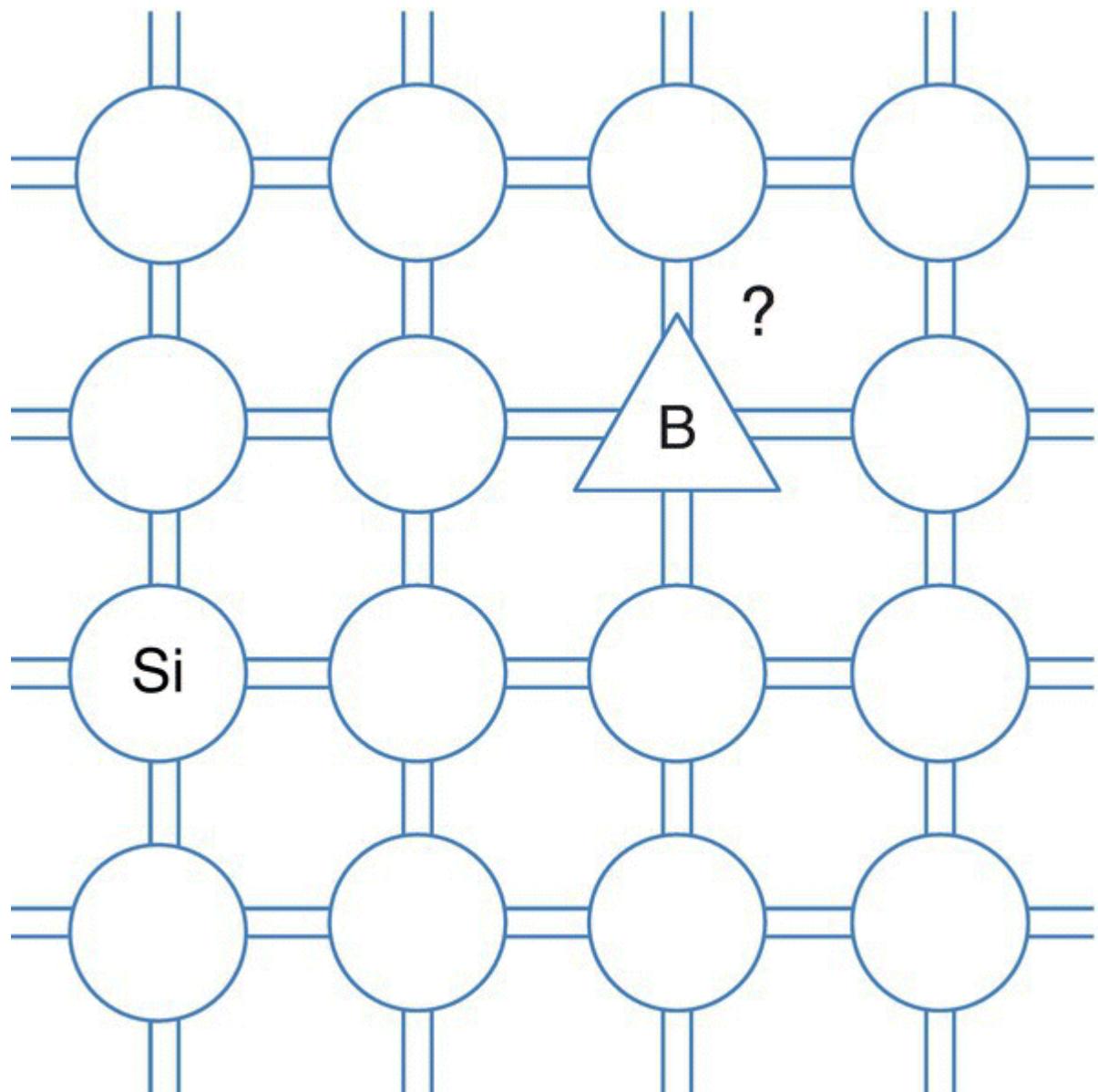

[Figure 3.10 The boron atom surrounded by a huge number of Si atoms takes the...](#)

[Figure 3.11 The energy of the boron empty bond is very close to the valence ...](#)

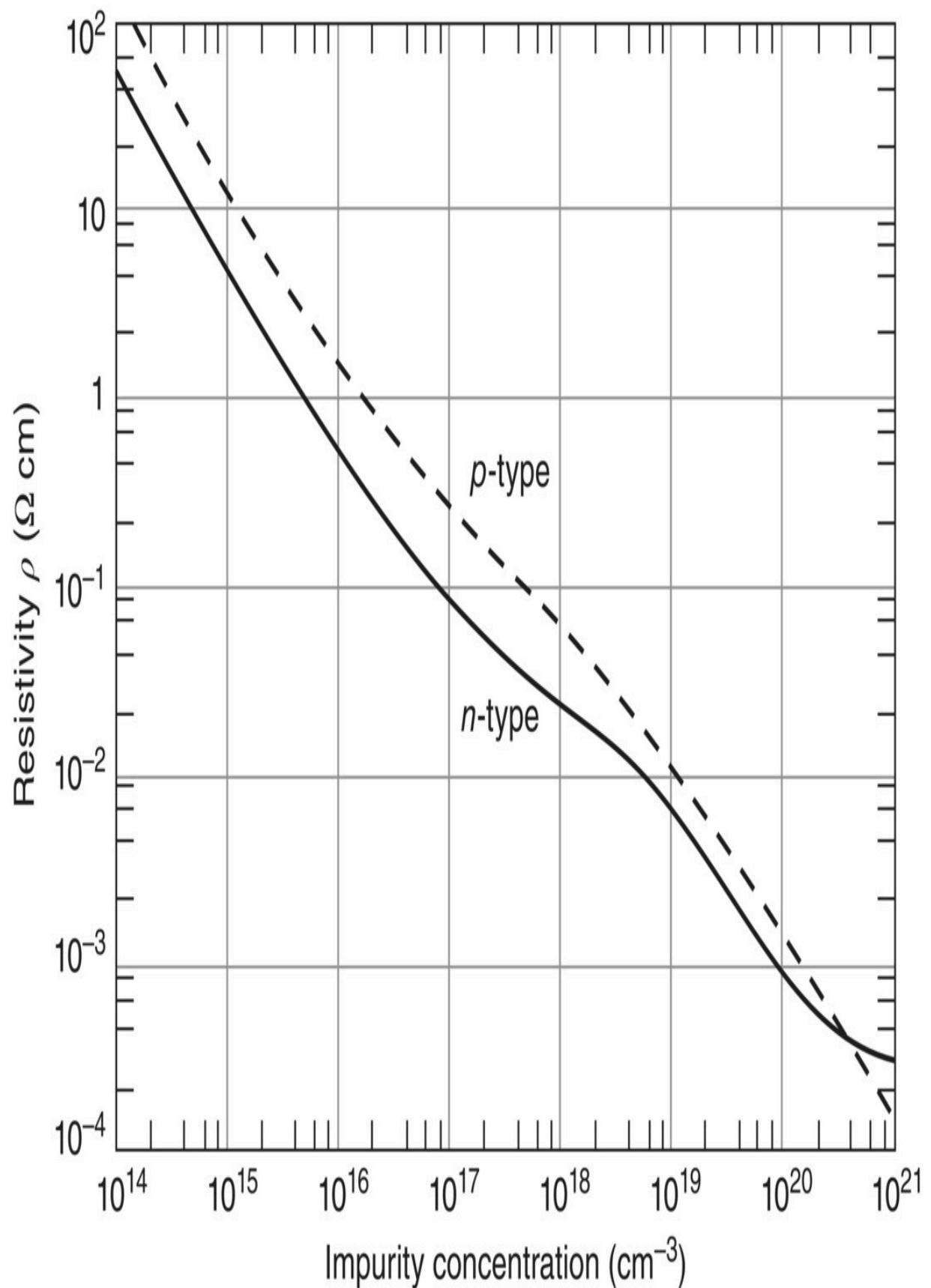

[Figure 3.12 the resistivity of n- and p-type silicon changes drastically as ...](#)

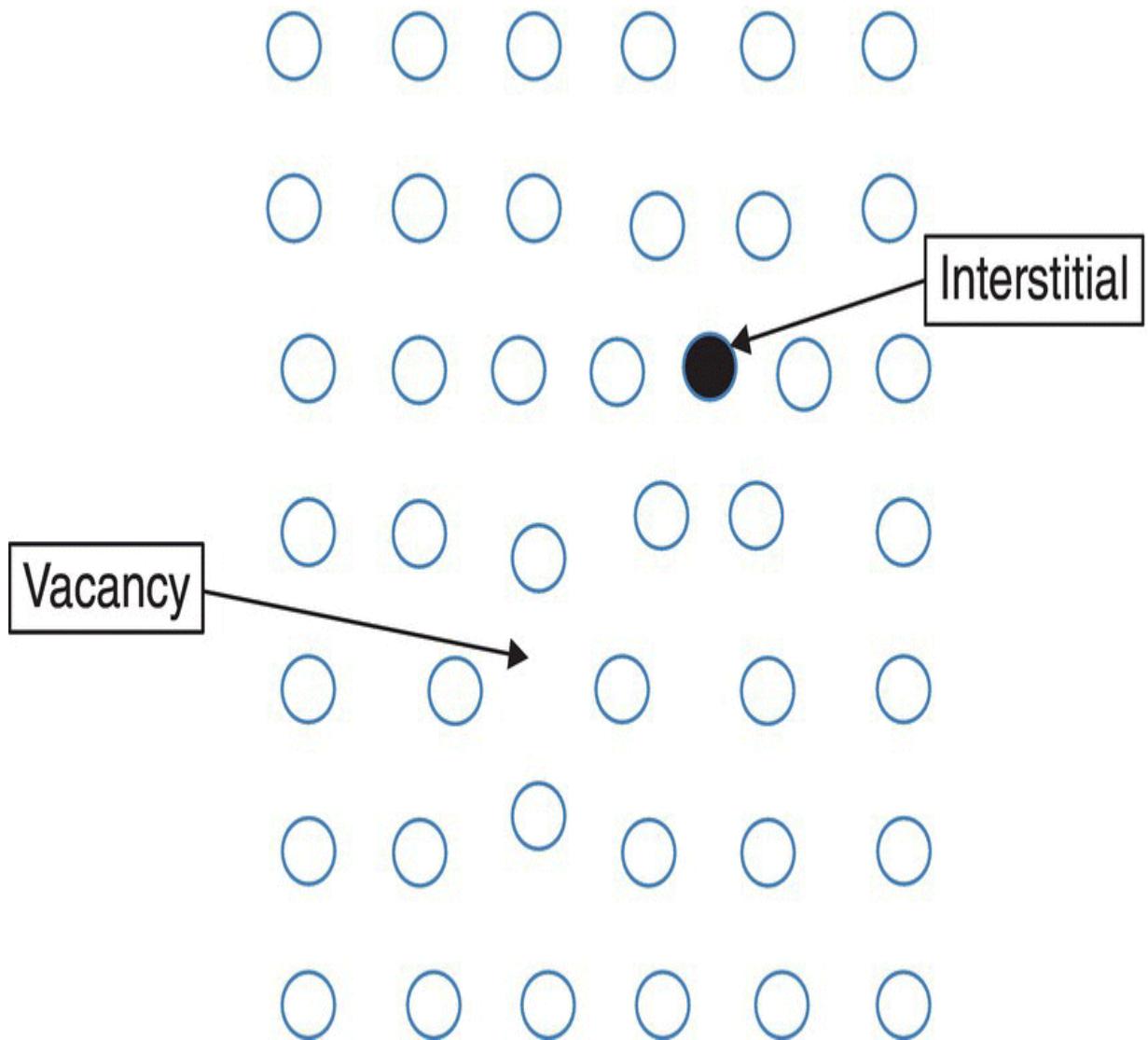

[Figure 3.13 Point defects in semiconductors, interstitial atoms or vacancies...](#)

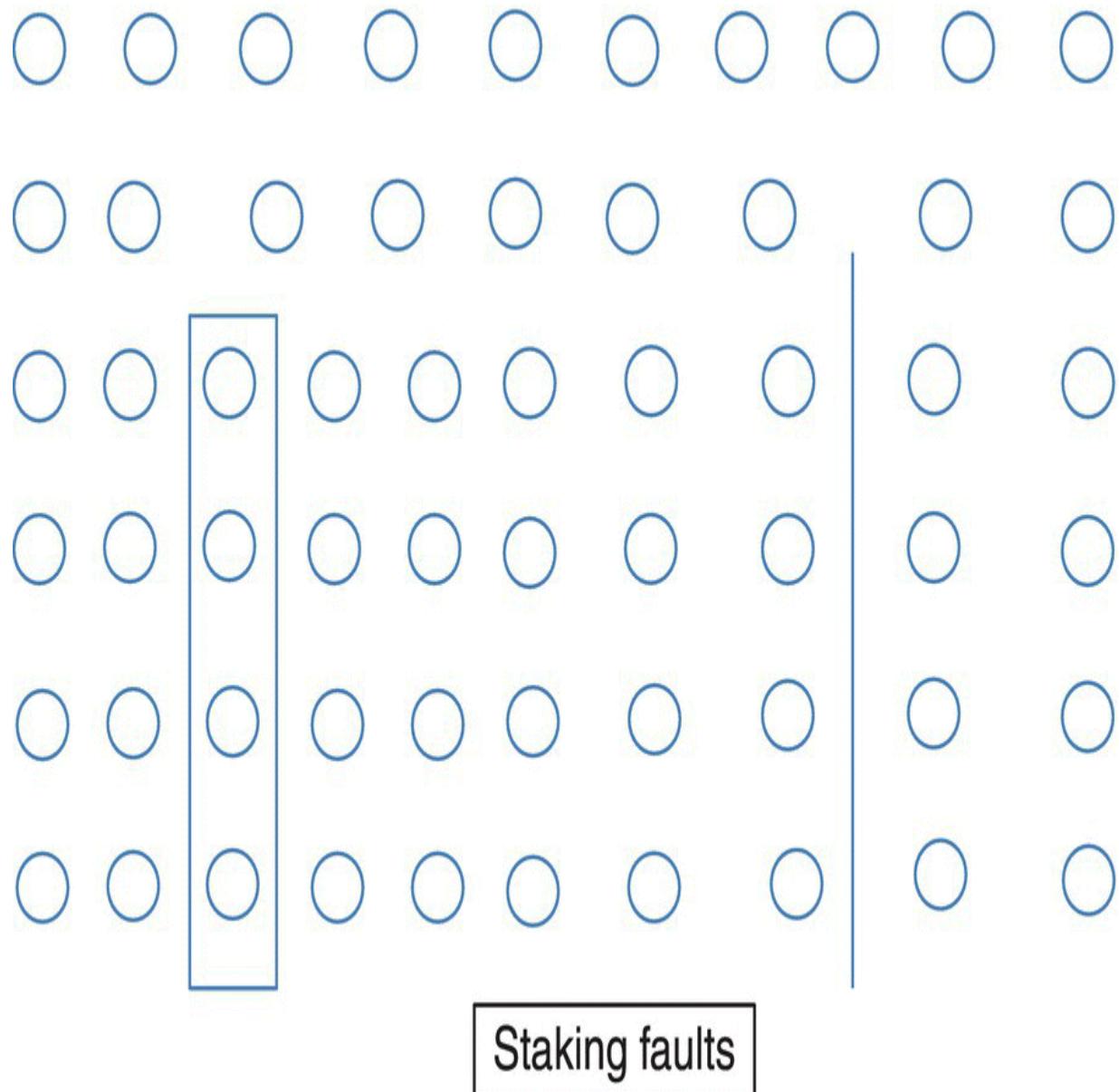

[Figure 3.14 Line dislocations, adding or losing a plane of atoms, also cause...](#)

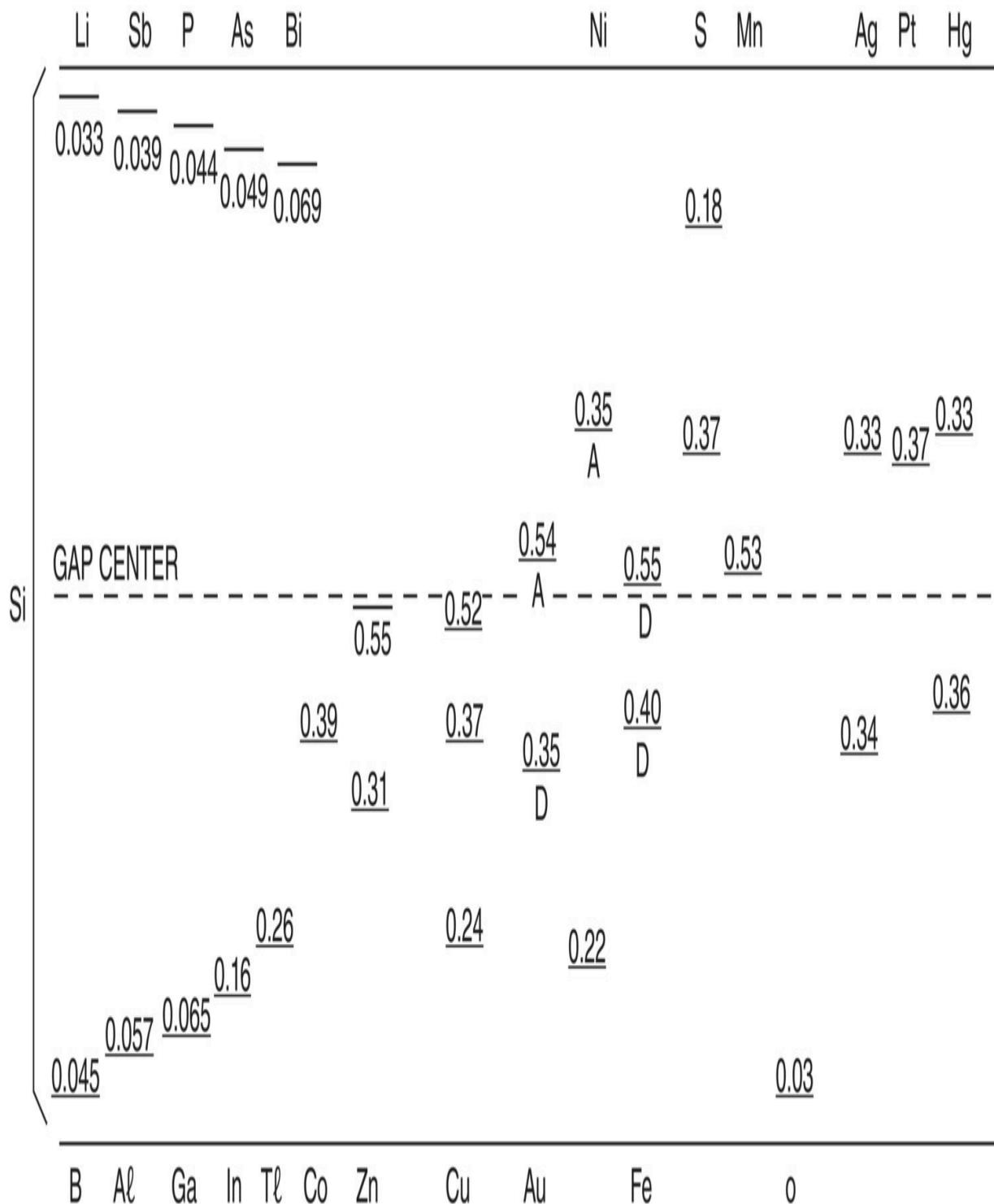

Figure 3.15 There are many native and doped impurities in Si that have very ...

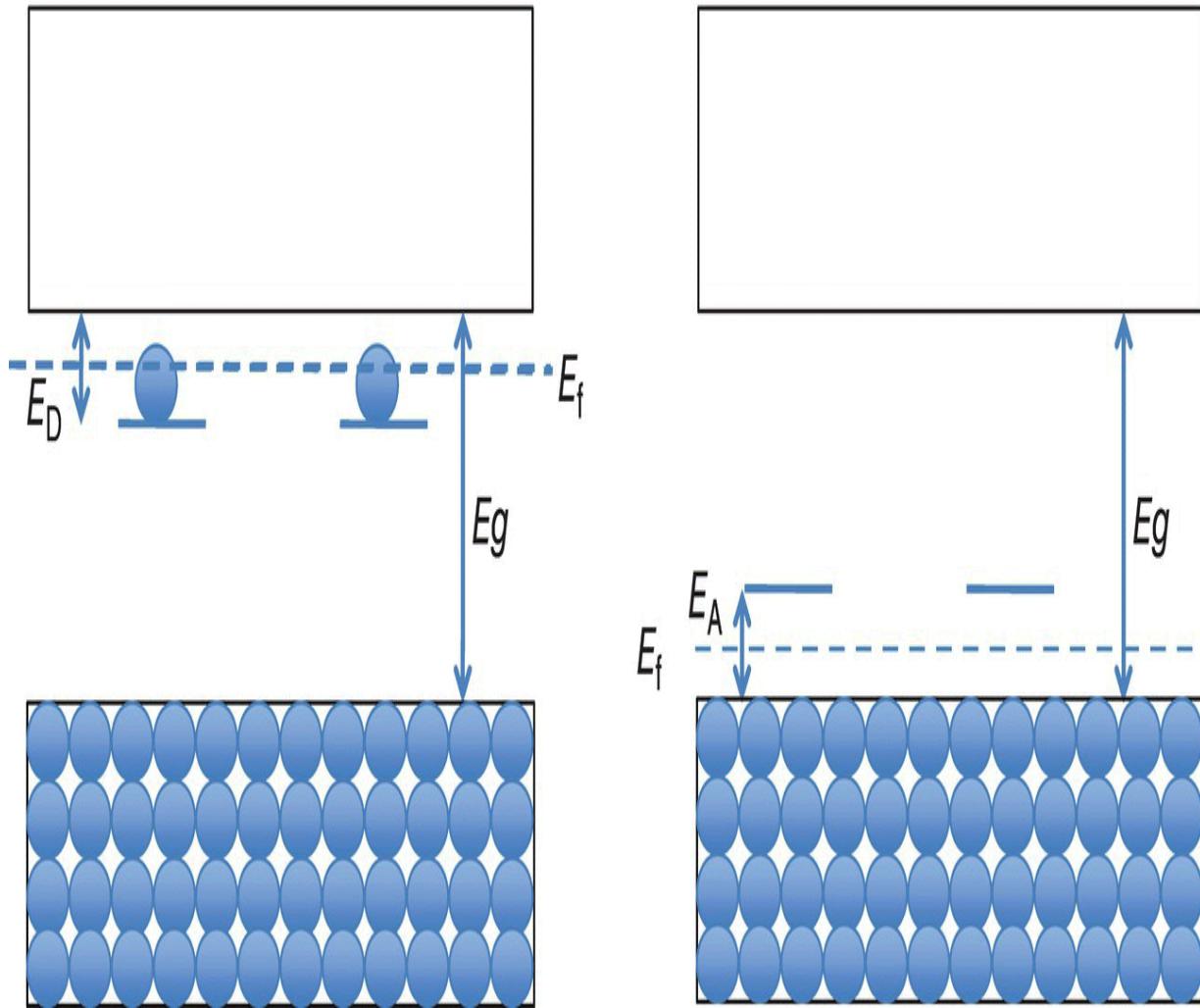

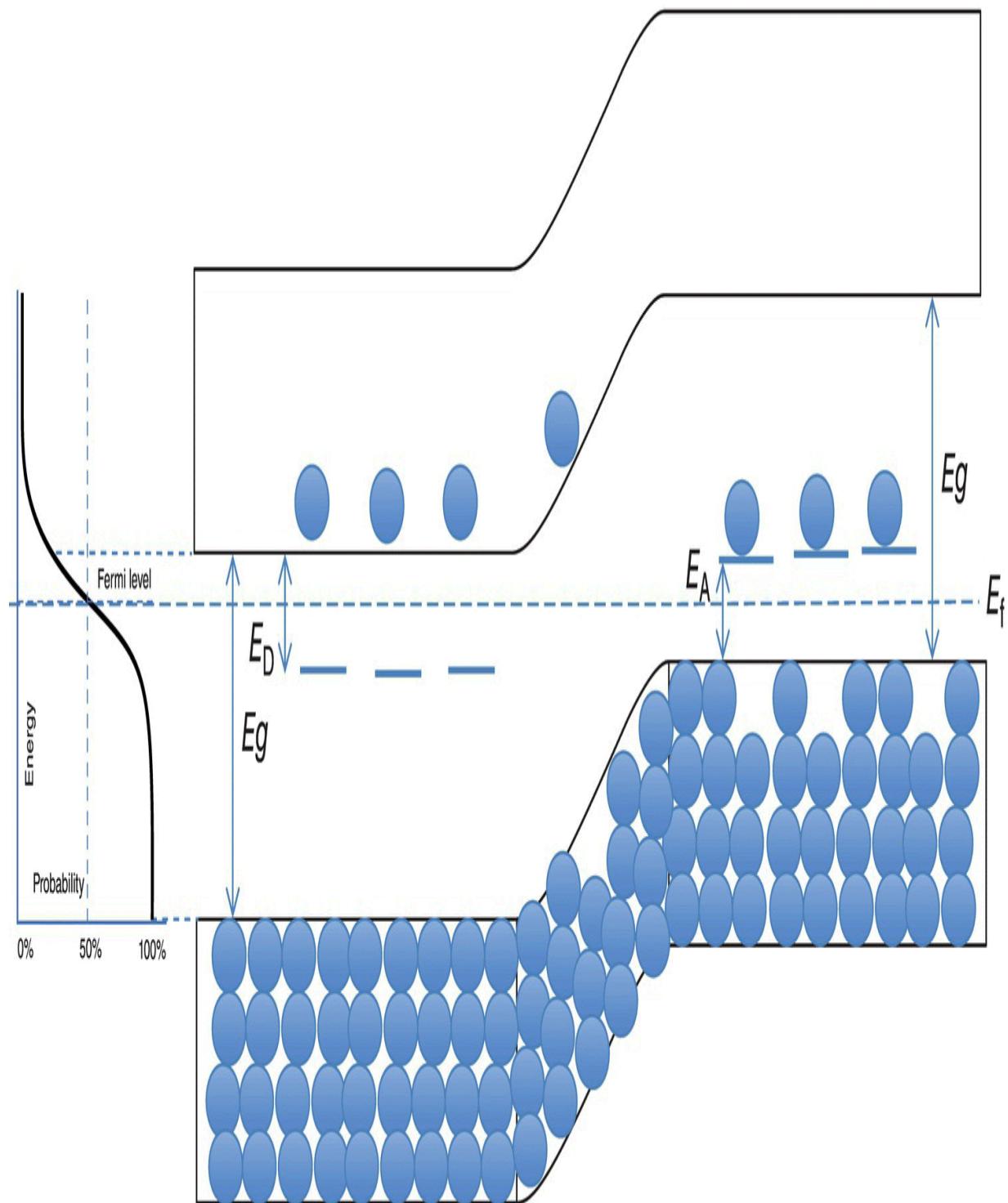

Figure 3.16 The Fermi level in n- and p-type semiconductors at 0 K are in th...

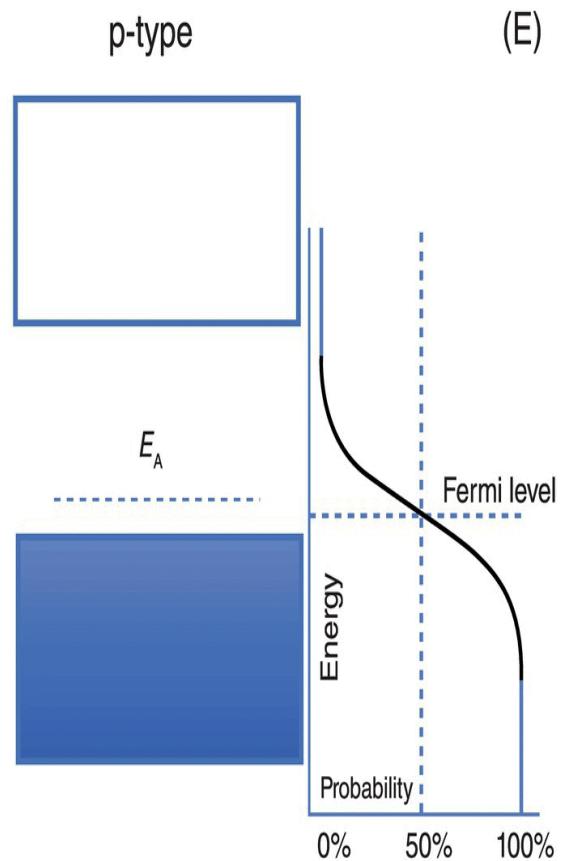

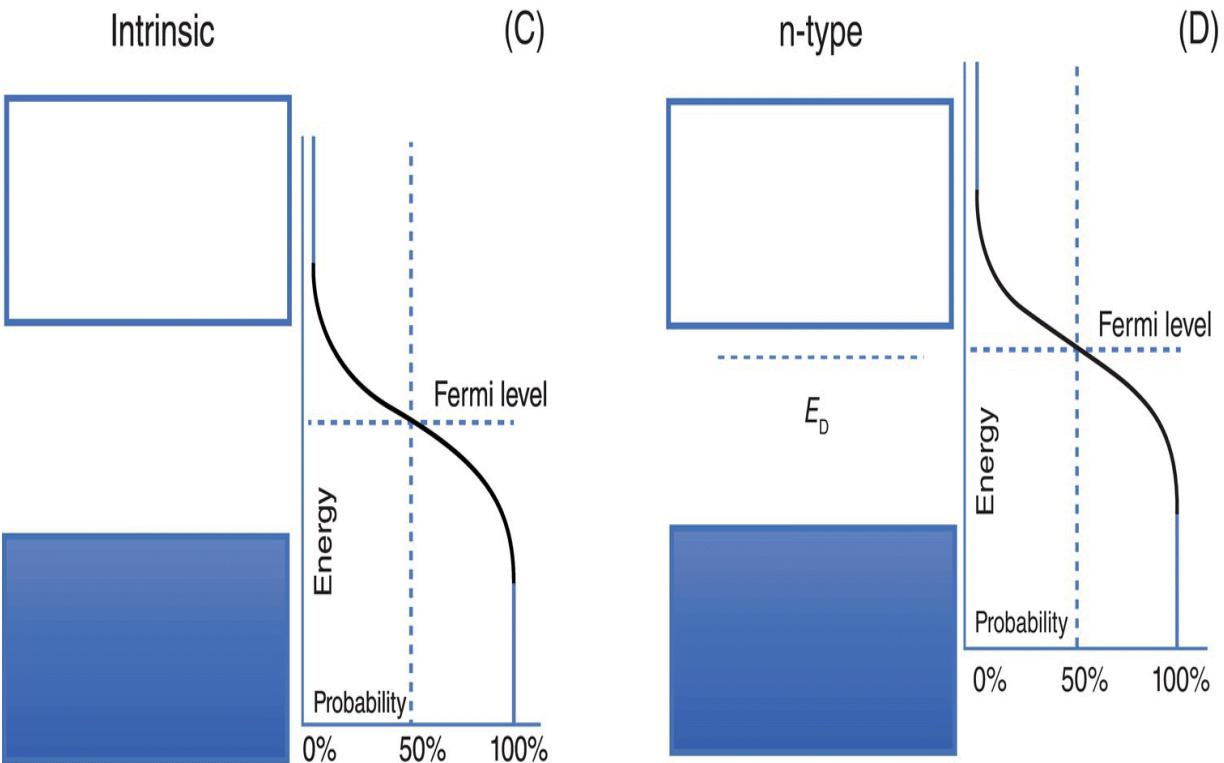

Figure 3.17 Intrinsic and doped semiconductors energy bands at 300 K. In the...

## Chapter 4

Figure 4.1 Hershel's experiment consisted of placing a thermometer beyond th...

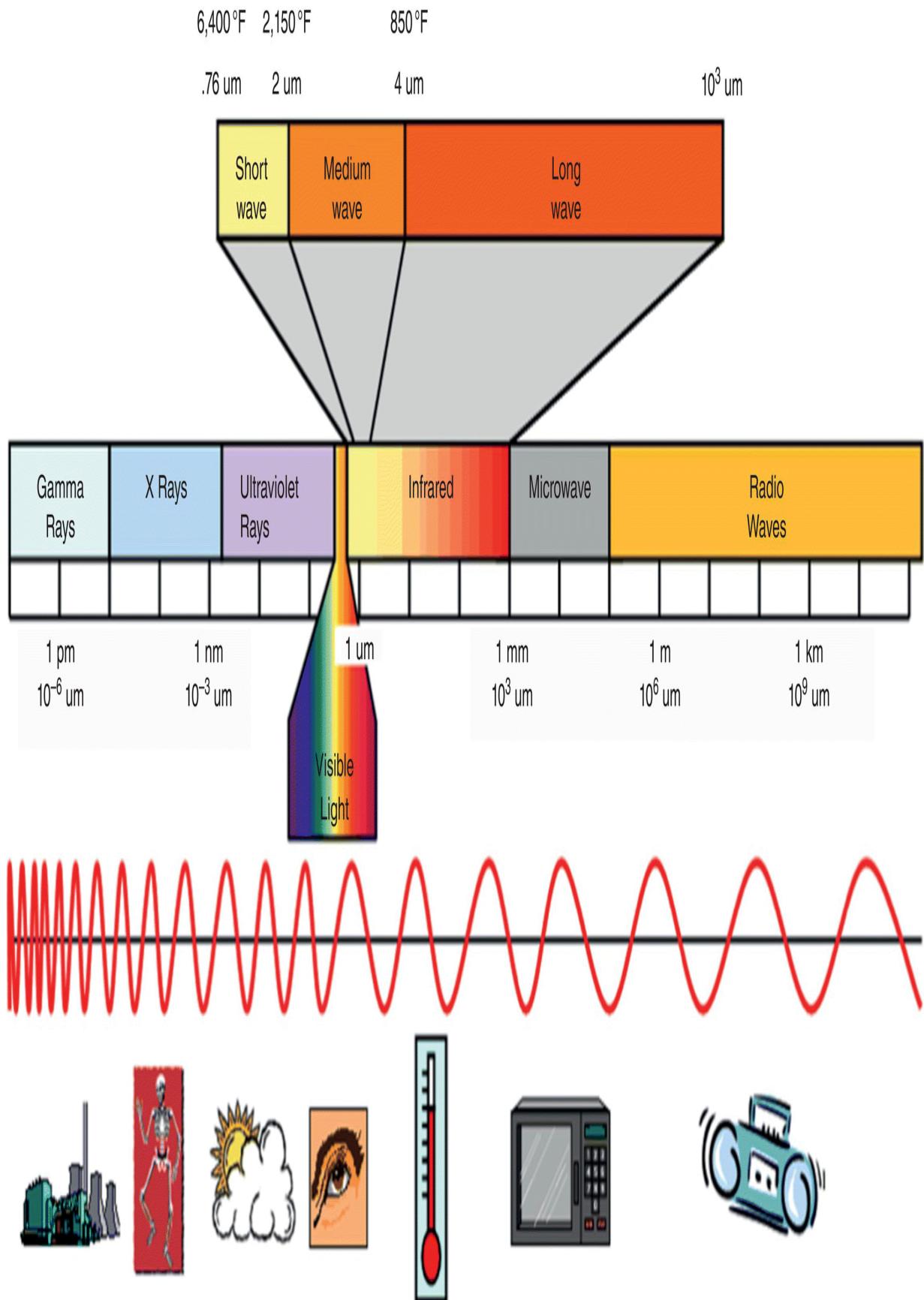

Figure 4.2 The entire radiation spectrum goes from gamma to radio waves, and...

Figure 4.3 Heinrich Rudolf Hertz, who studied electromagnetic waves, was rew...

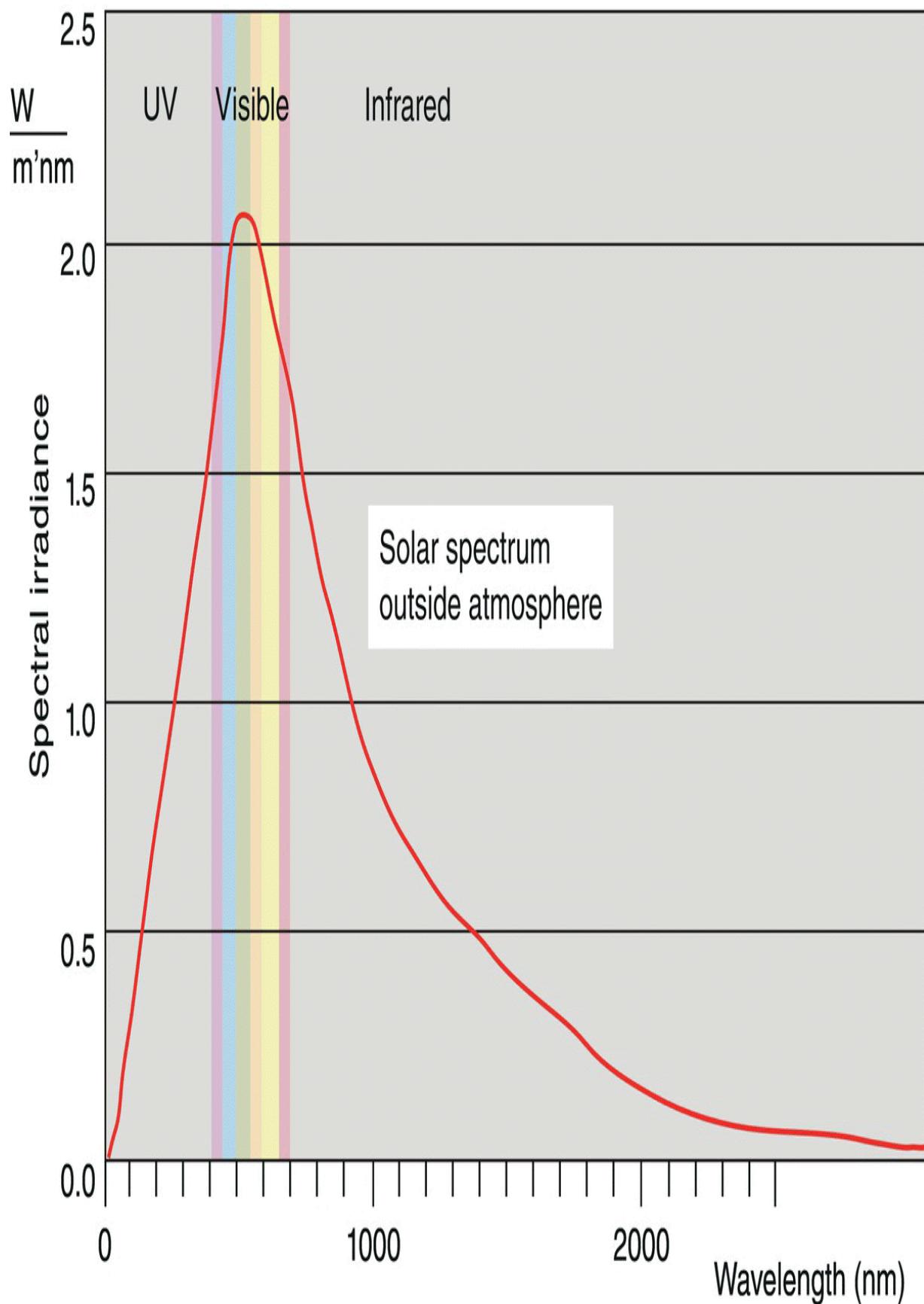

Figure 4.4 The sun's radiation spectrum is strongest in the range of wavelen...

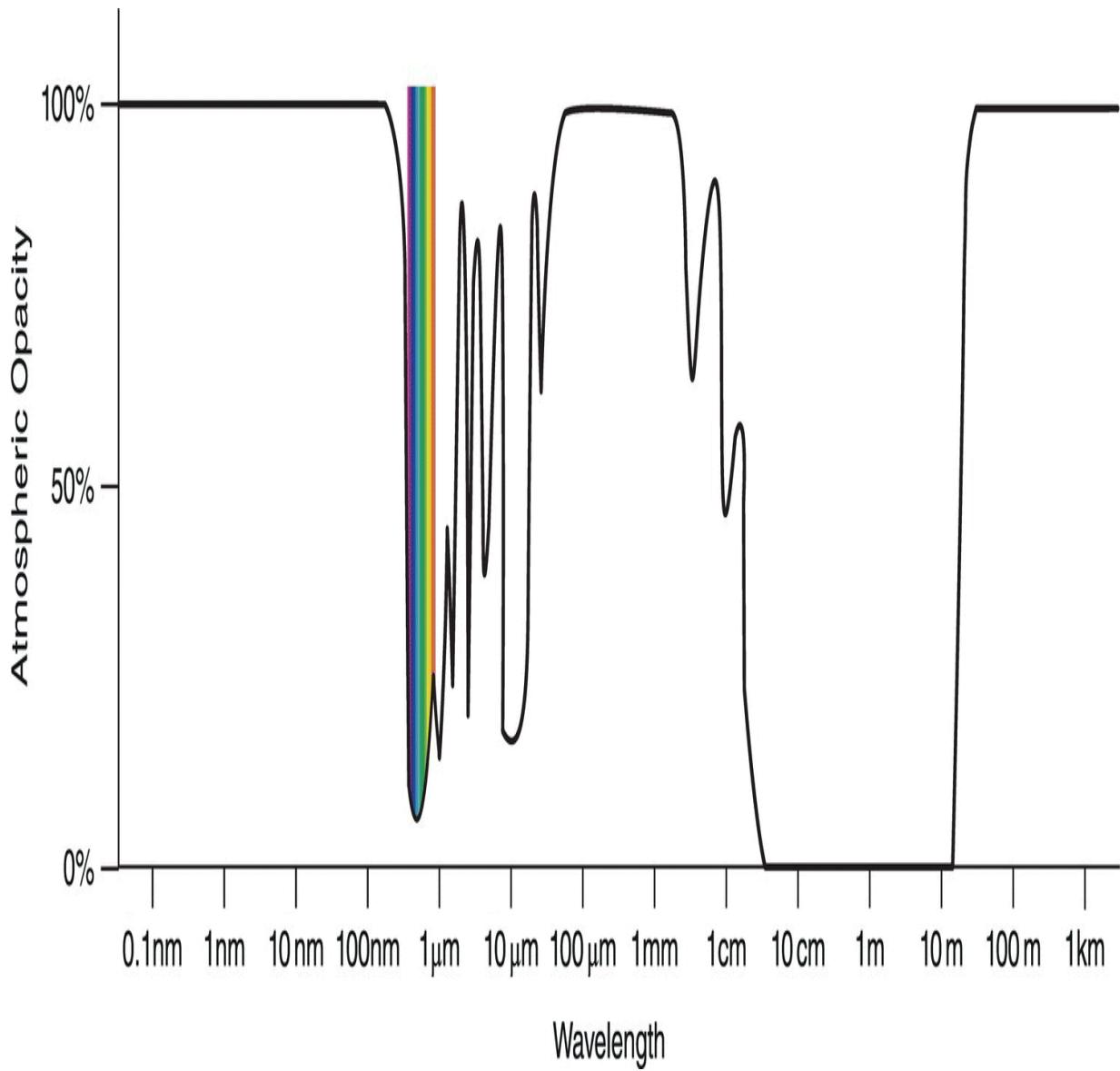

Figure 4.5 The earth's atmosphere is opaque except in the visible range and ...

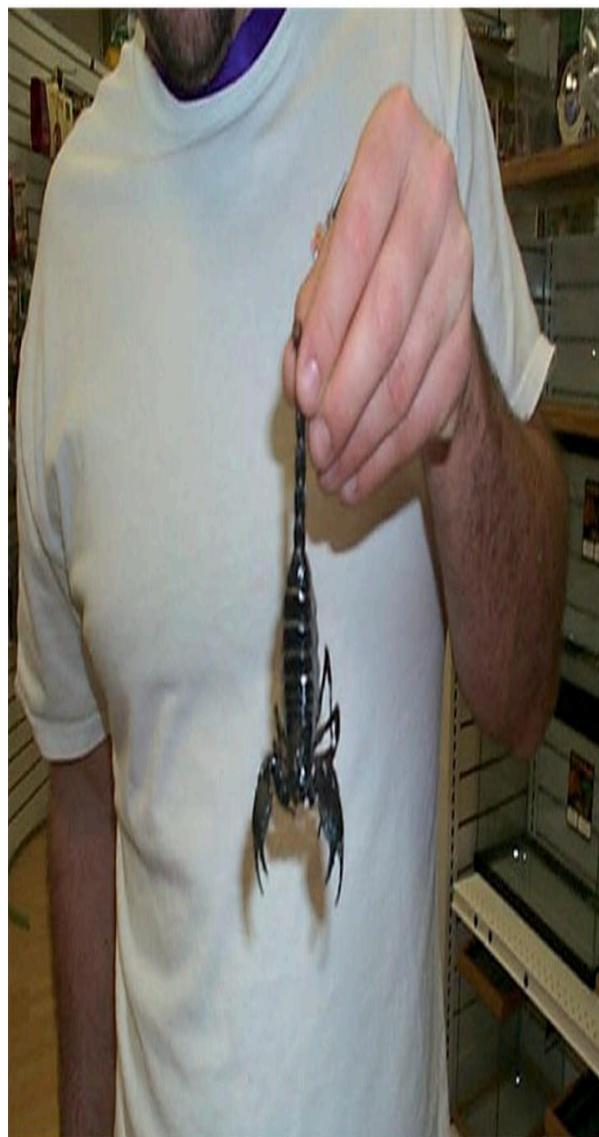

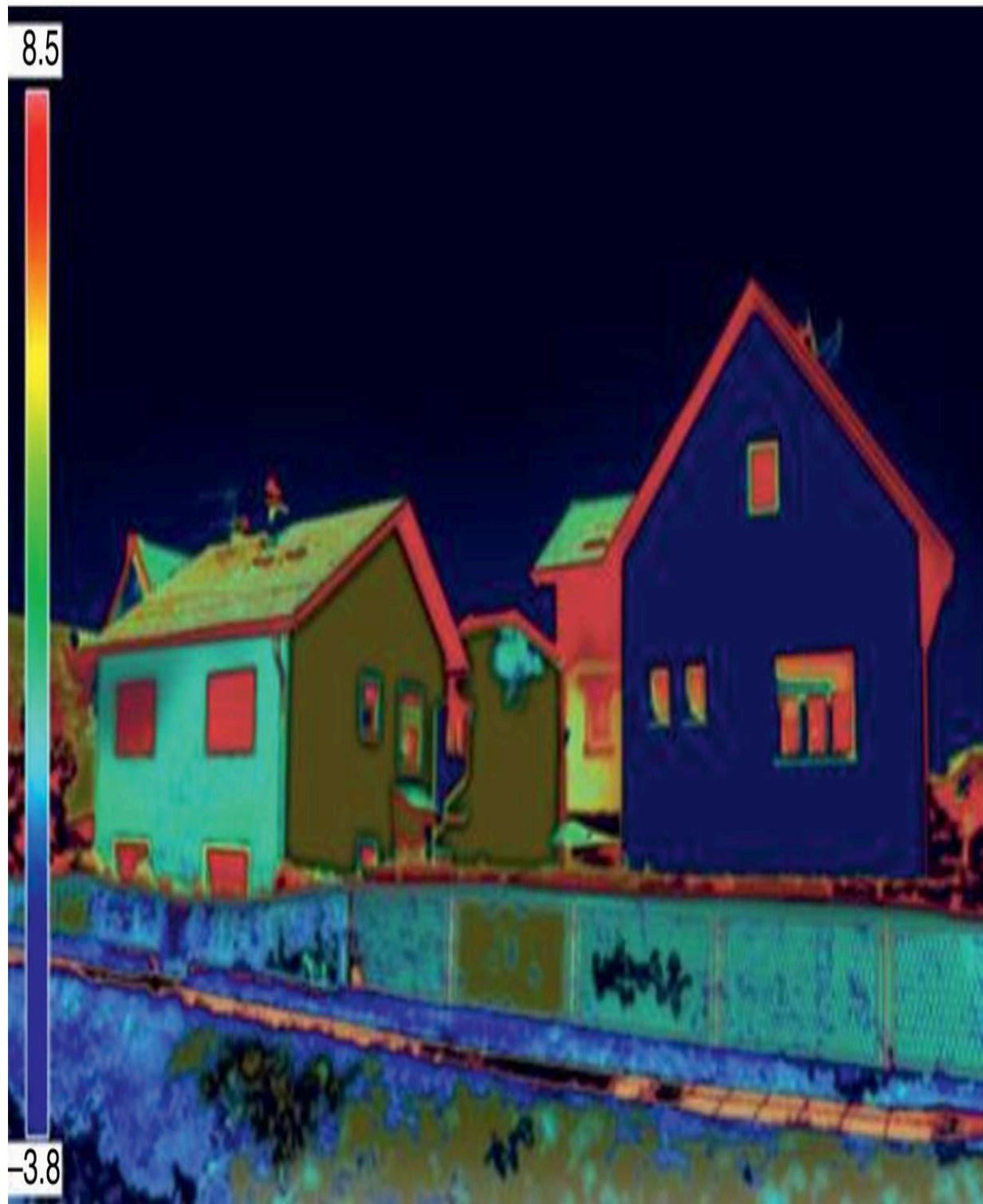

Figure 4.6 Visible and infrared photographs comparing the cold body of a sco...

Figure 4.7 On the right the man hides his arm with a plastic bag. The arm is...

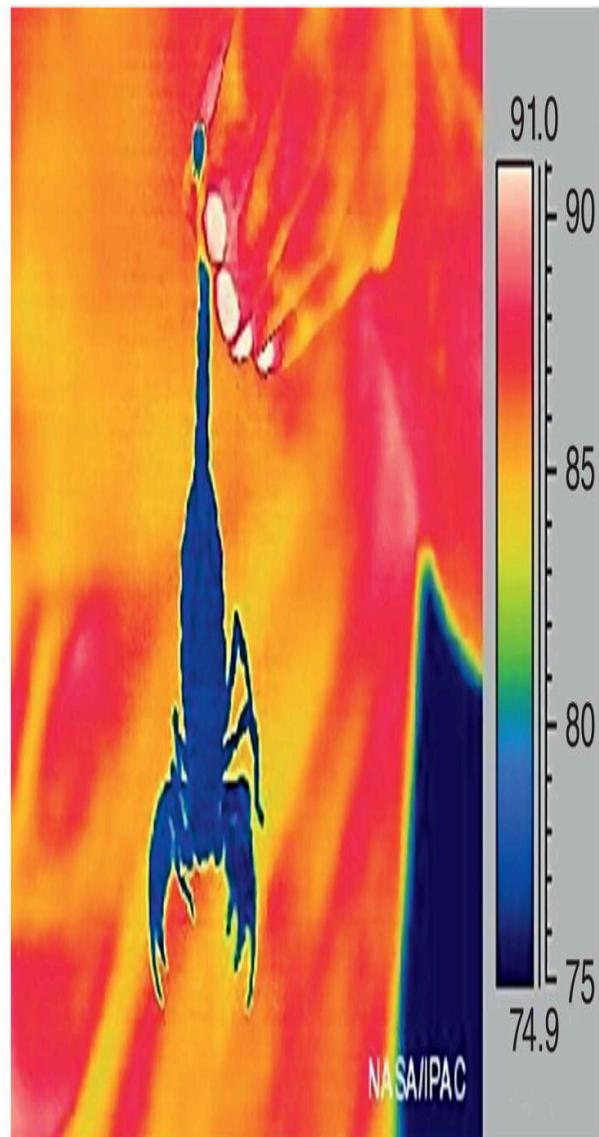

Figure 4.8 This infrared image of houses shows where heat is lost due to lac...

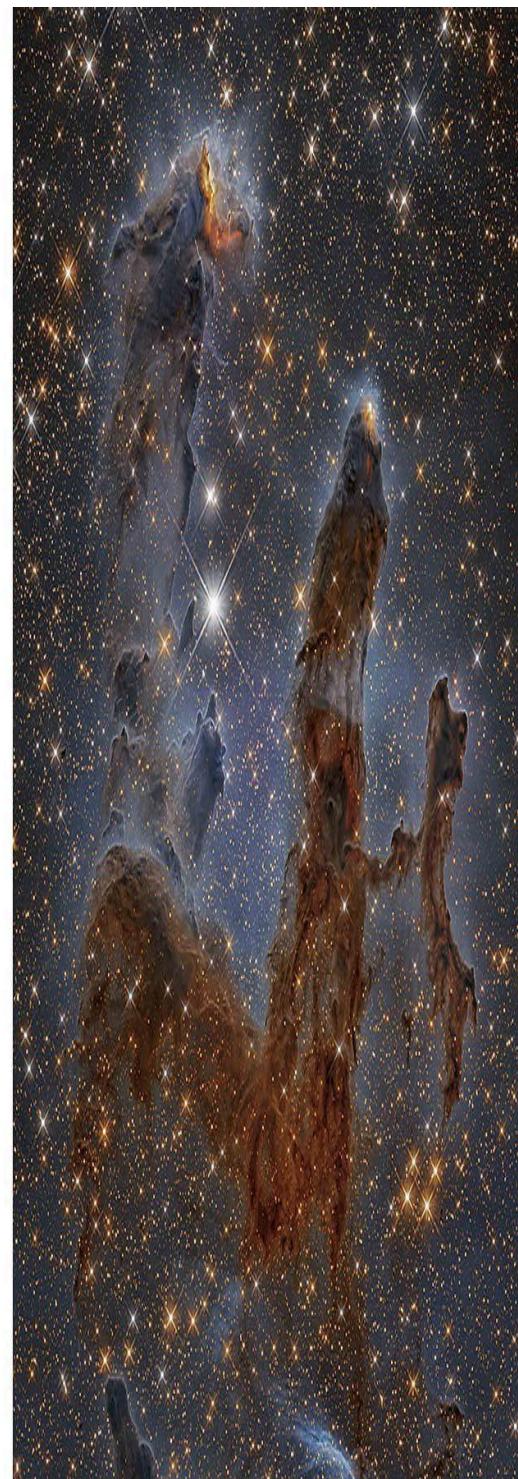

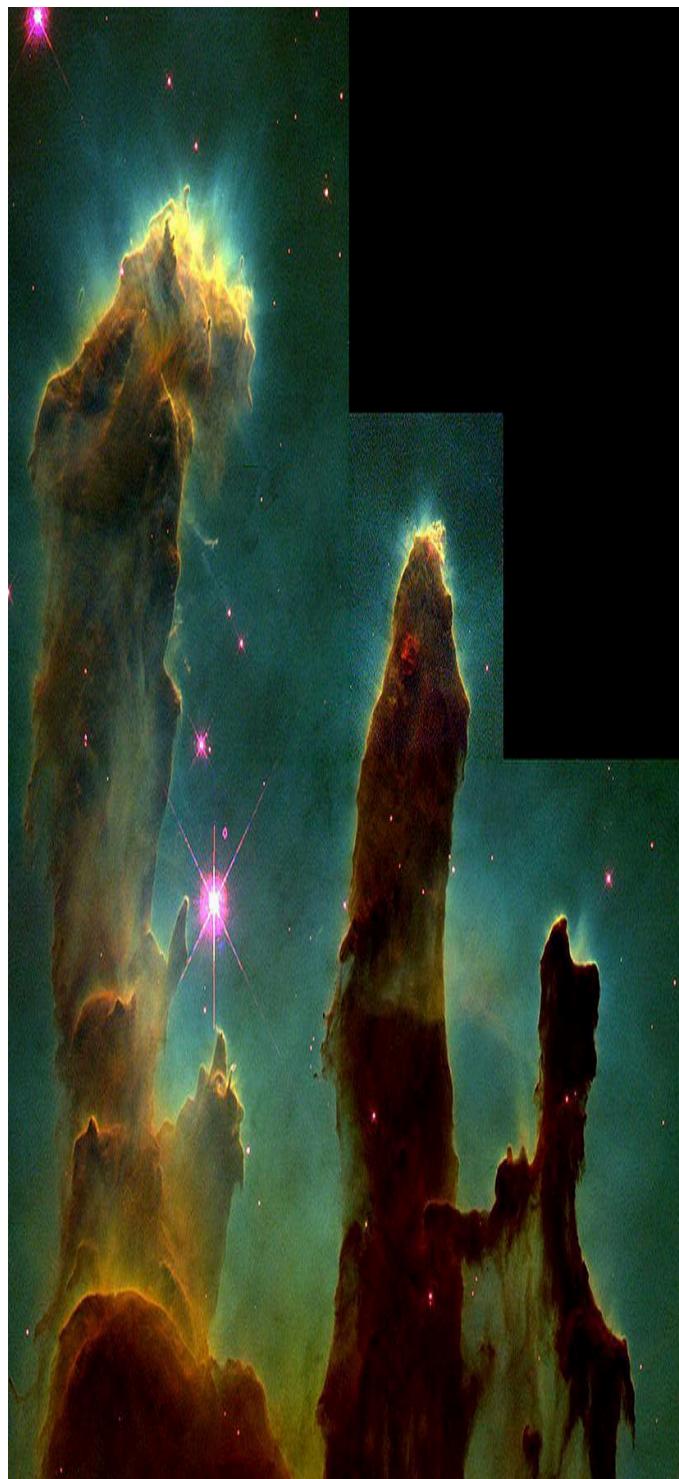

Figure 4.9 The Eagle nebula captured by the Hubble telescope using the visib...

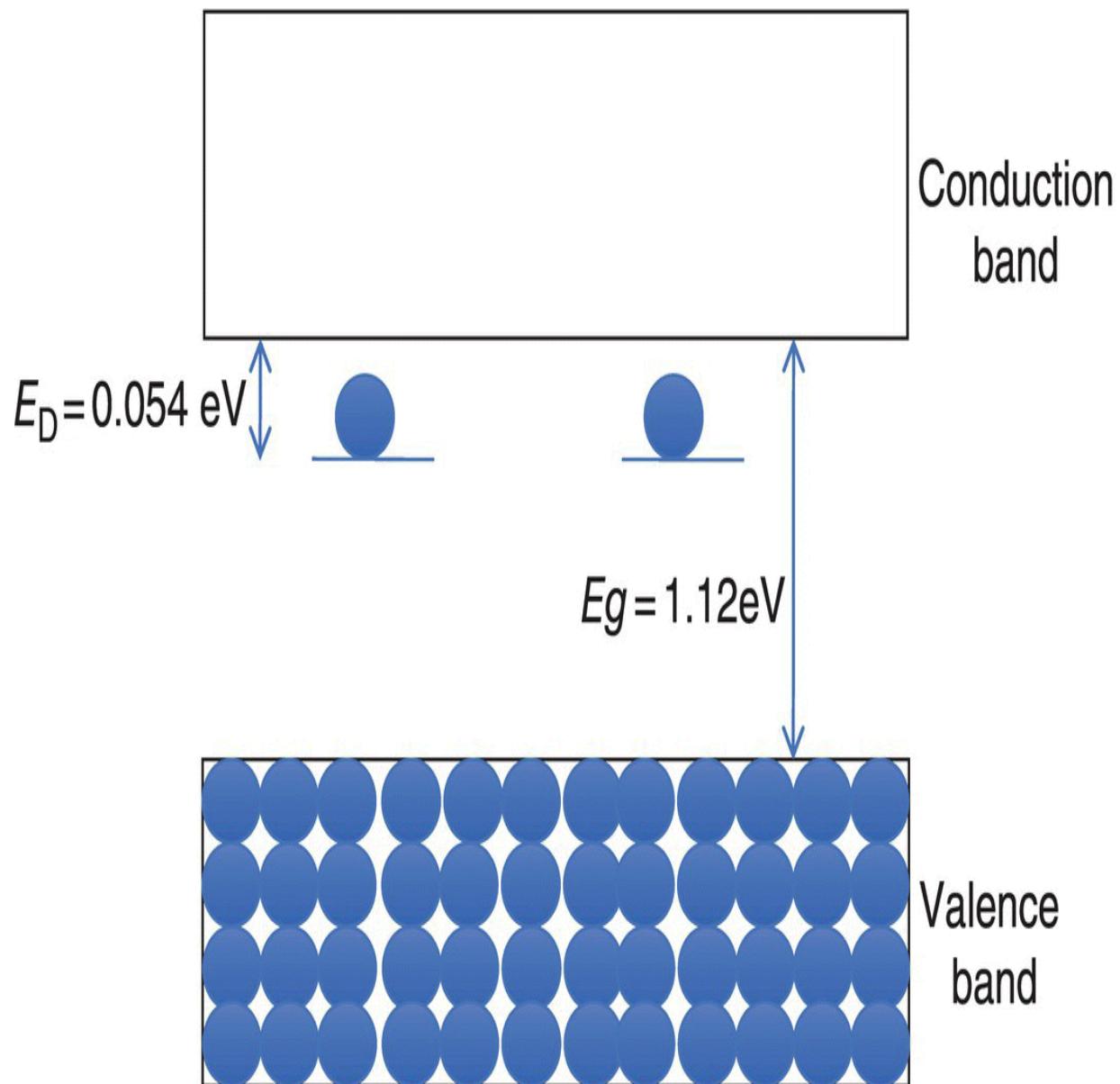

Figure 4.10 At very close to absolute zero all the electrons from the donor ...

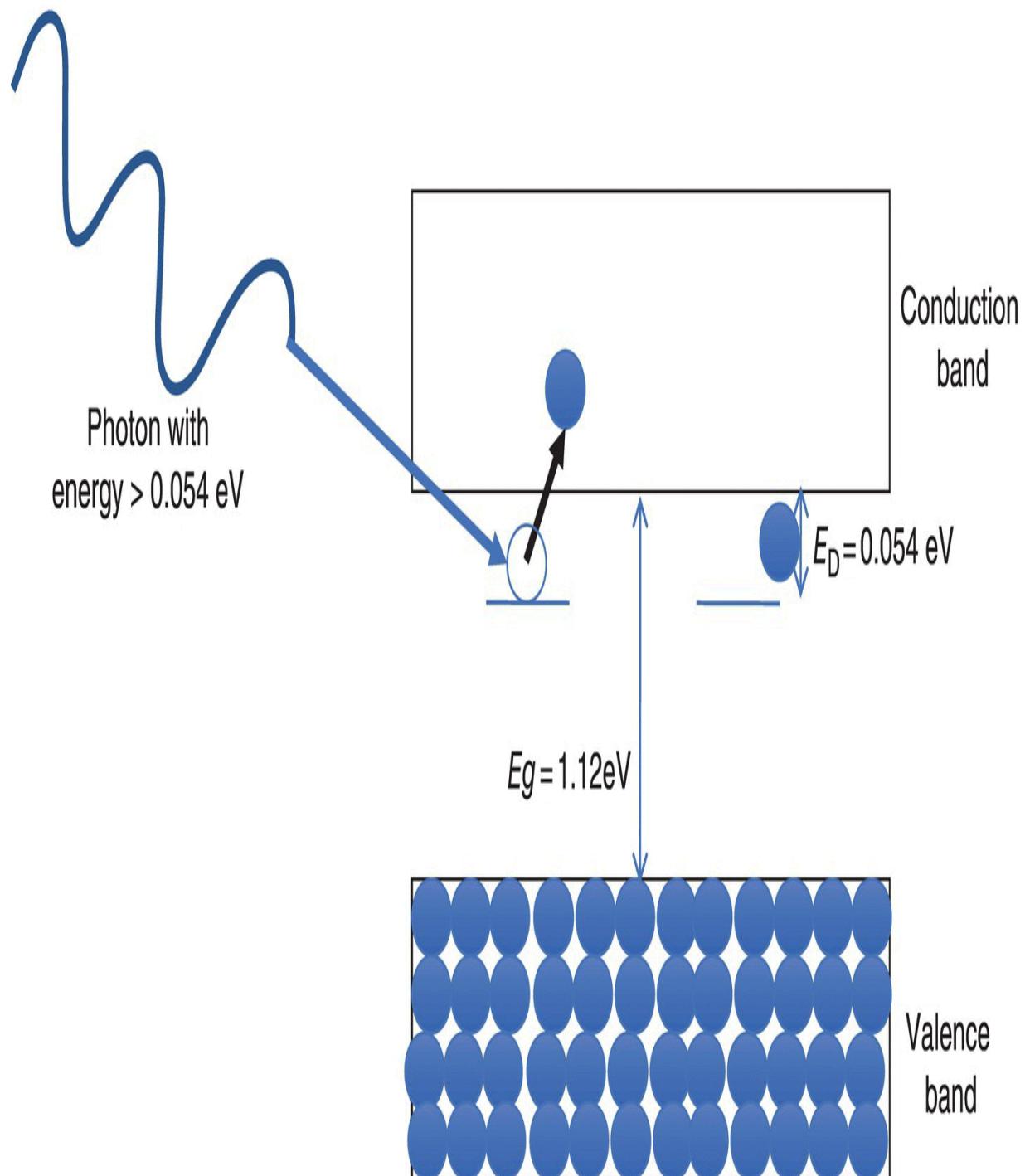

Figure 4.11 A photon with energy greater than 0.054 eV hits the As-doped sil...

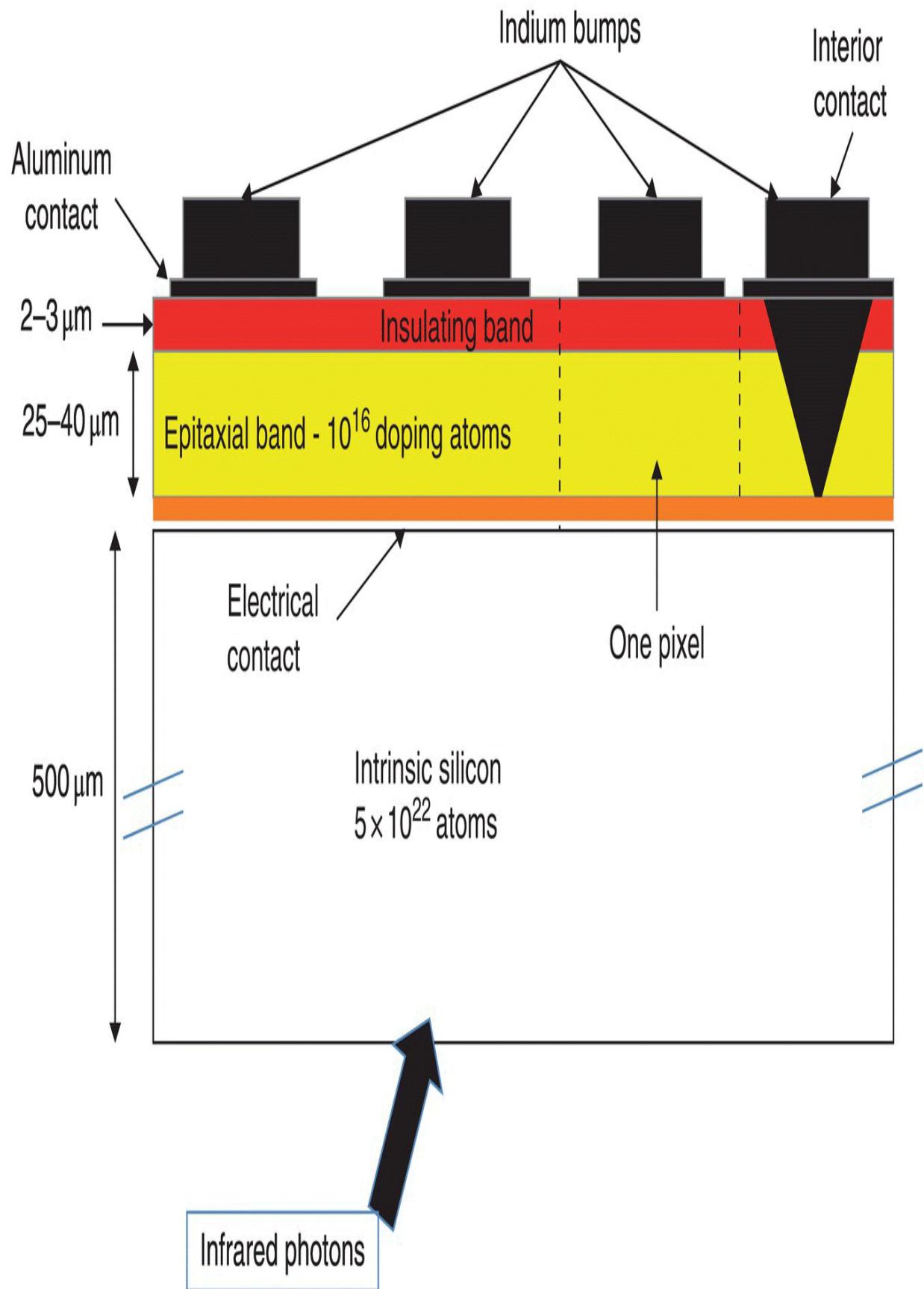

[Figure 4.12 Cross-section of an arsenic doped infrared detector showing the ...](#)

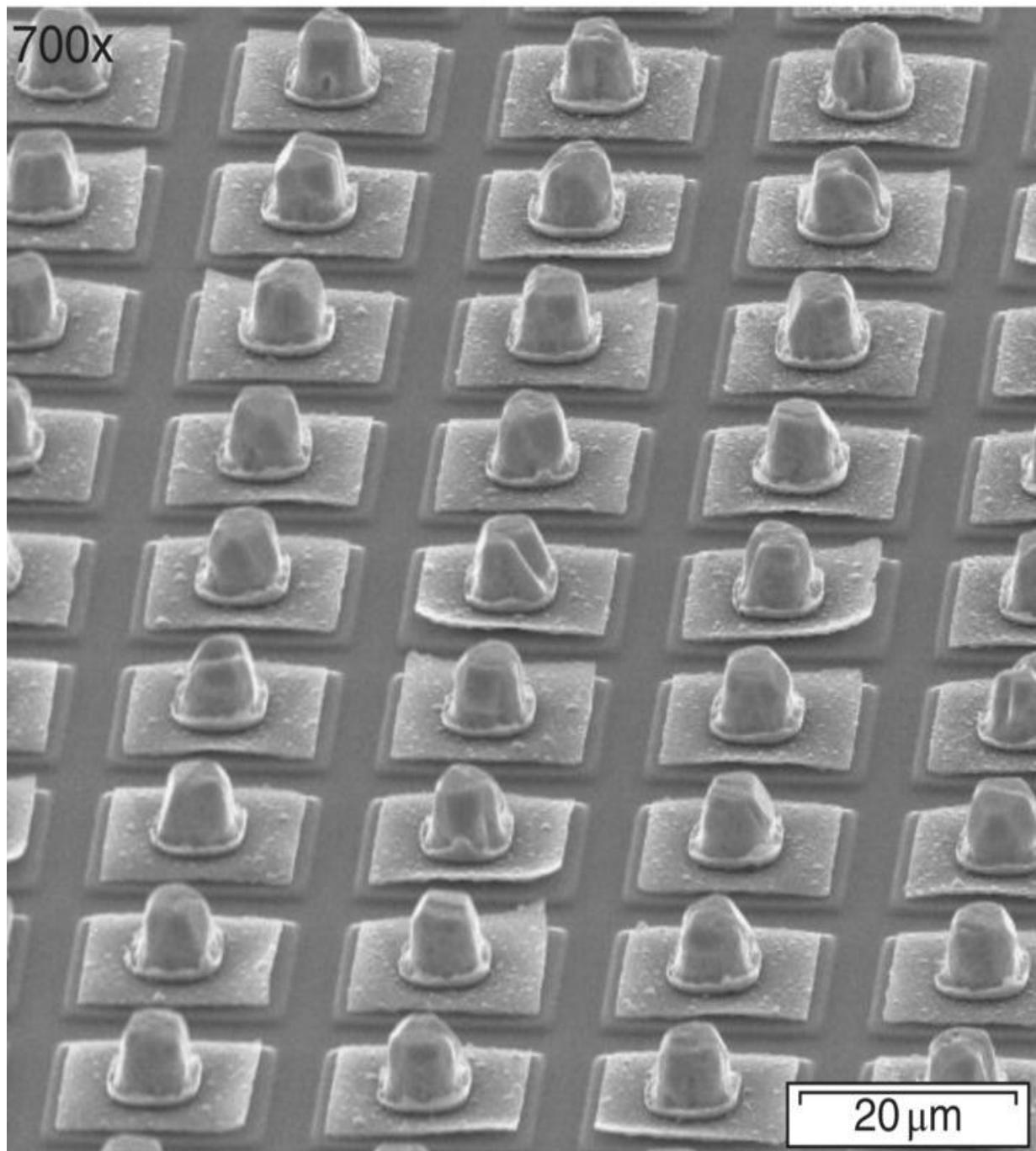

[Figure 4.13 A photograph of the contacts and indium bumps that define and co...](#)

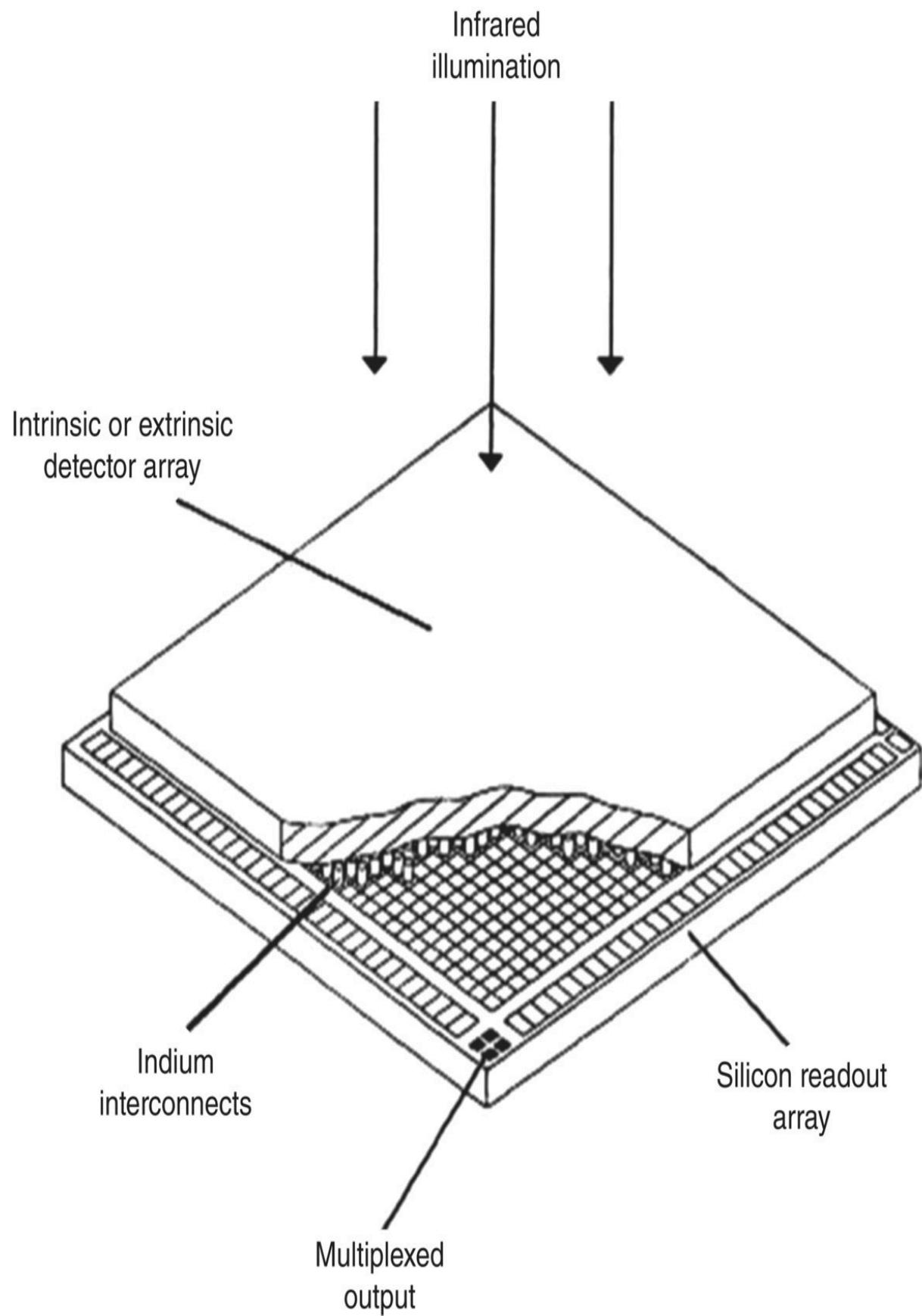

[Figure 4.14 A completed detector assembly with the detector array on top of ...](#)

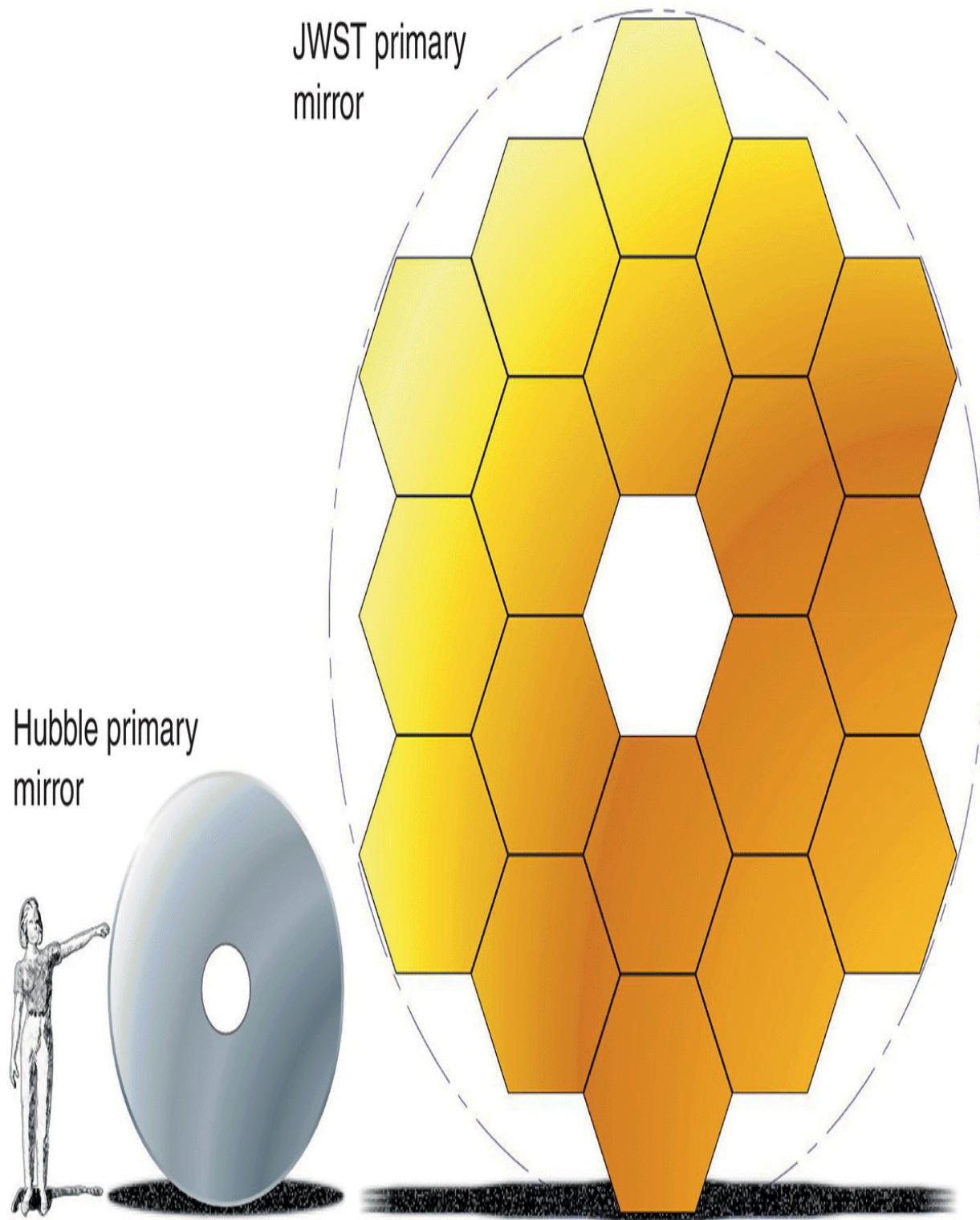

[Figure 4.15 The primary mirror of the Jack Webb telescope consists of very l...](#)

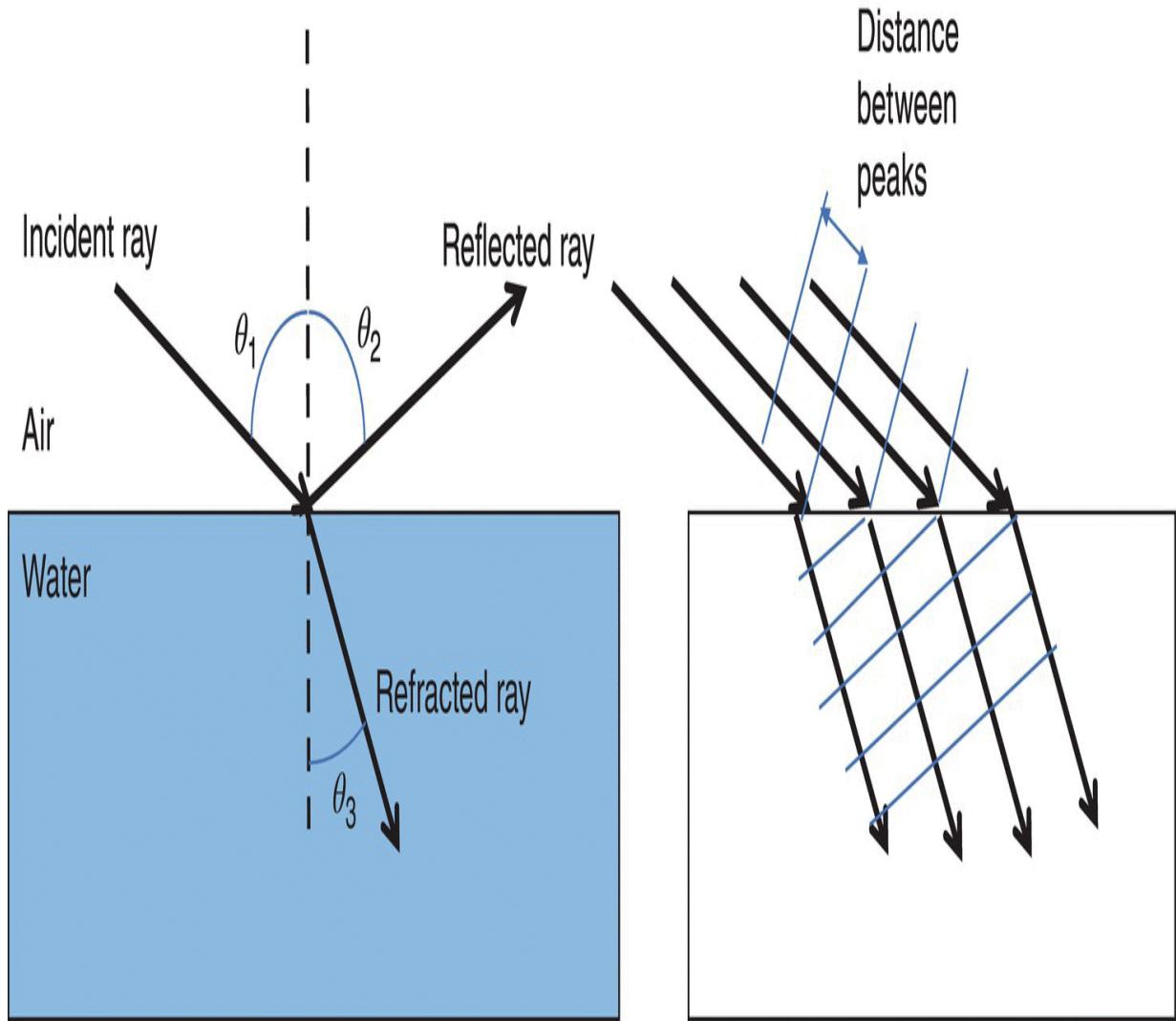

[Figure 4.16 The reflection and refraction of light as it moves from air to w...](#)

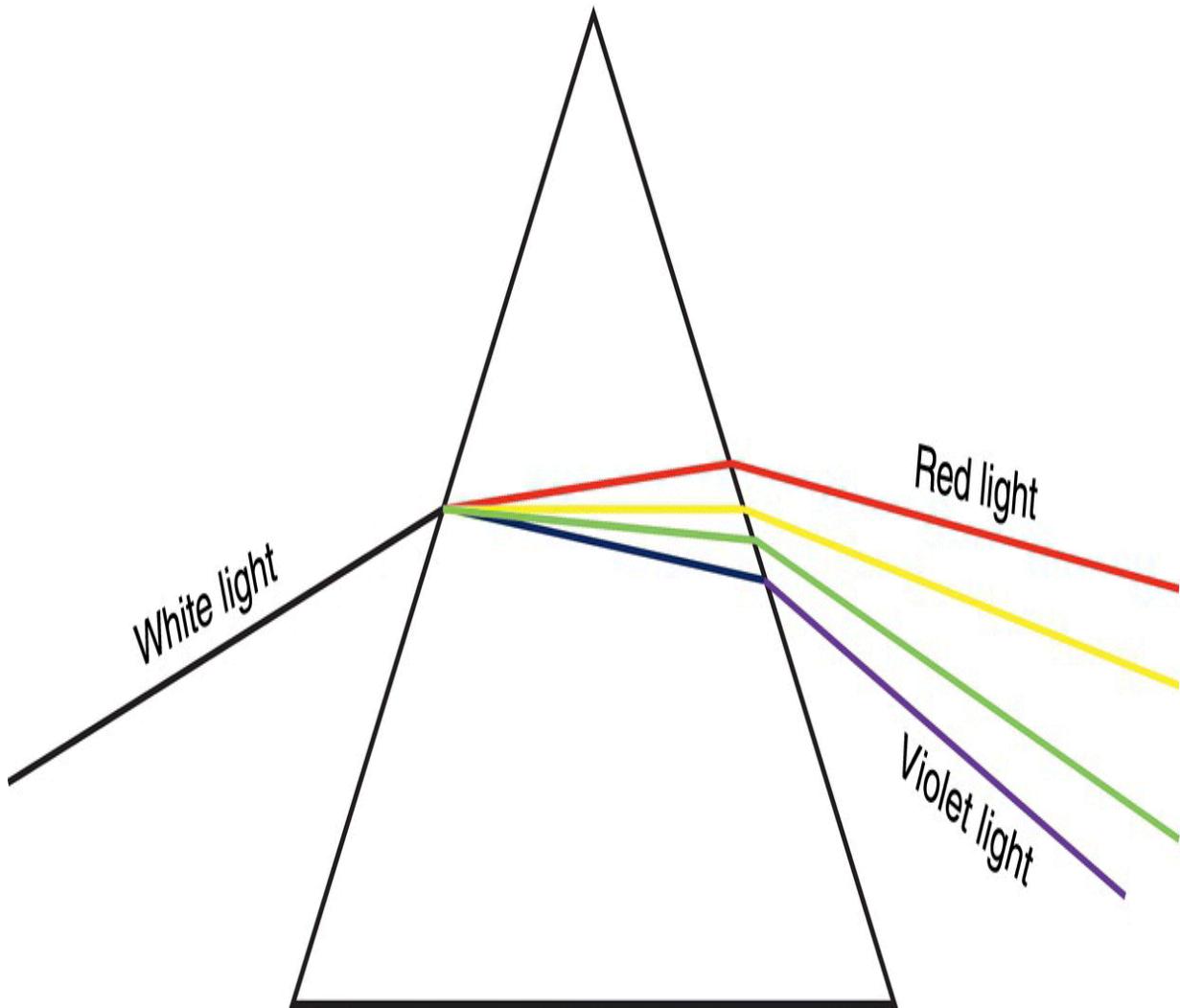

[Figure 4.17 Light dispersion as it crosses a prism, separating the different...](#)

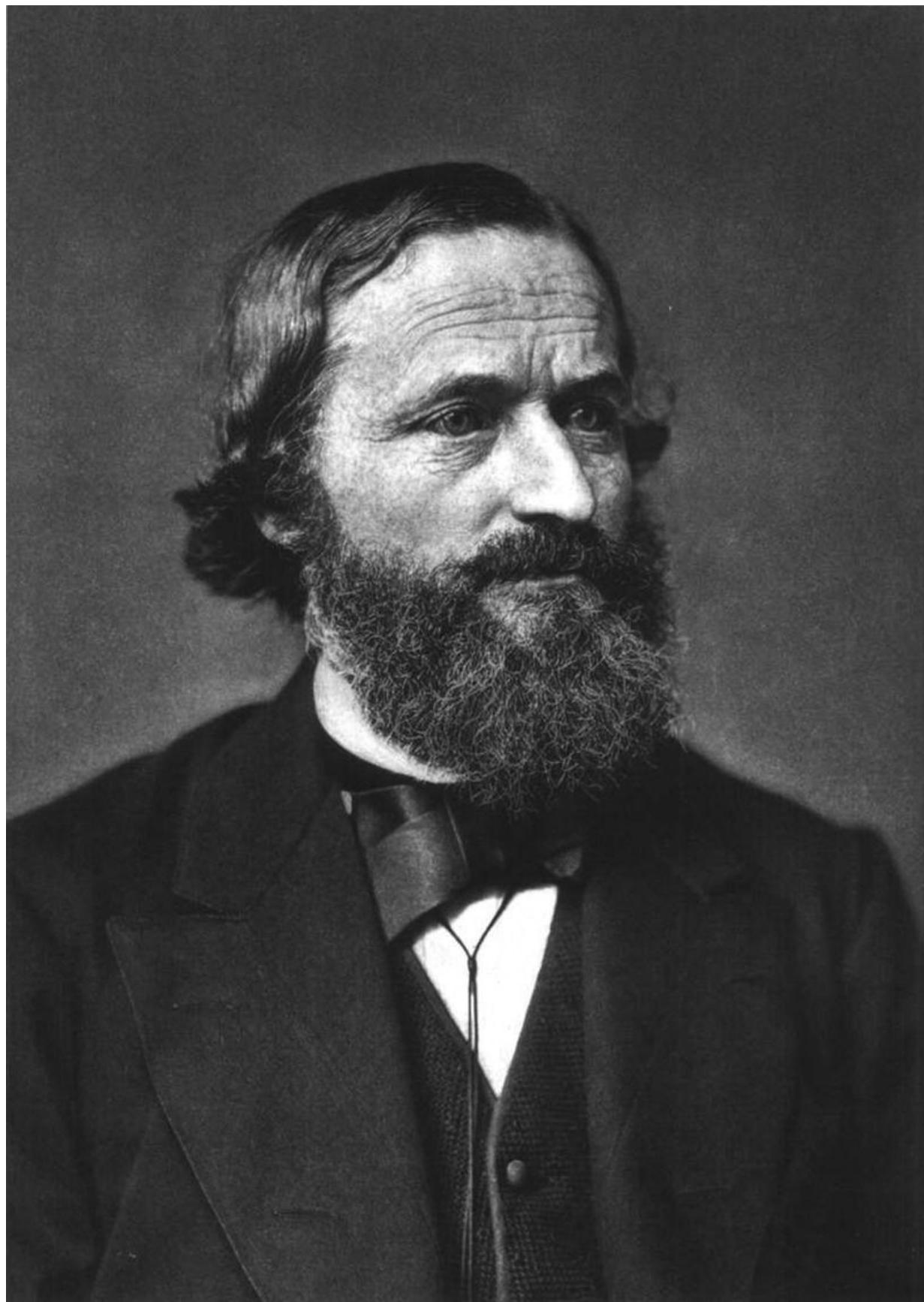

[Figure 4.18 Gustav Kirchhoff defined the term “blackbody,” an object which w...](#)

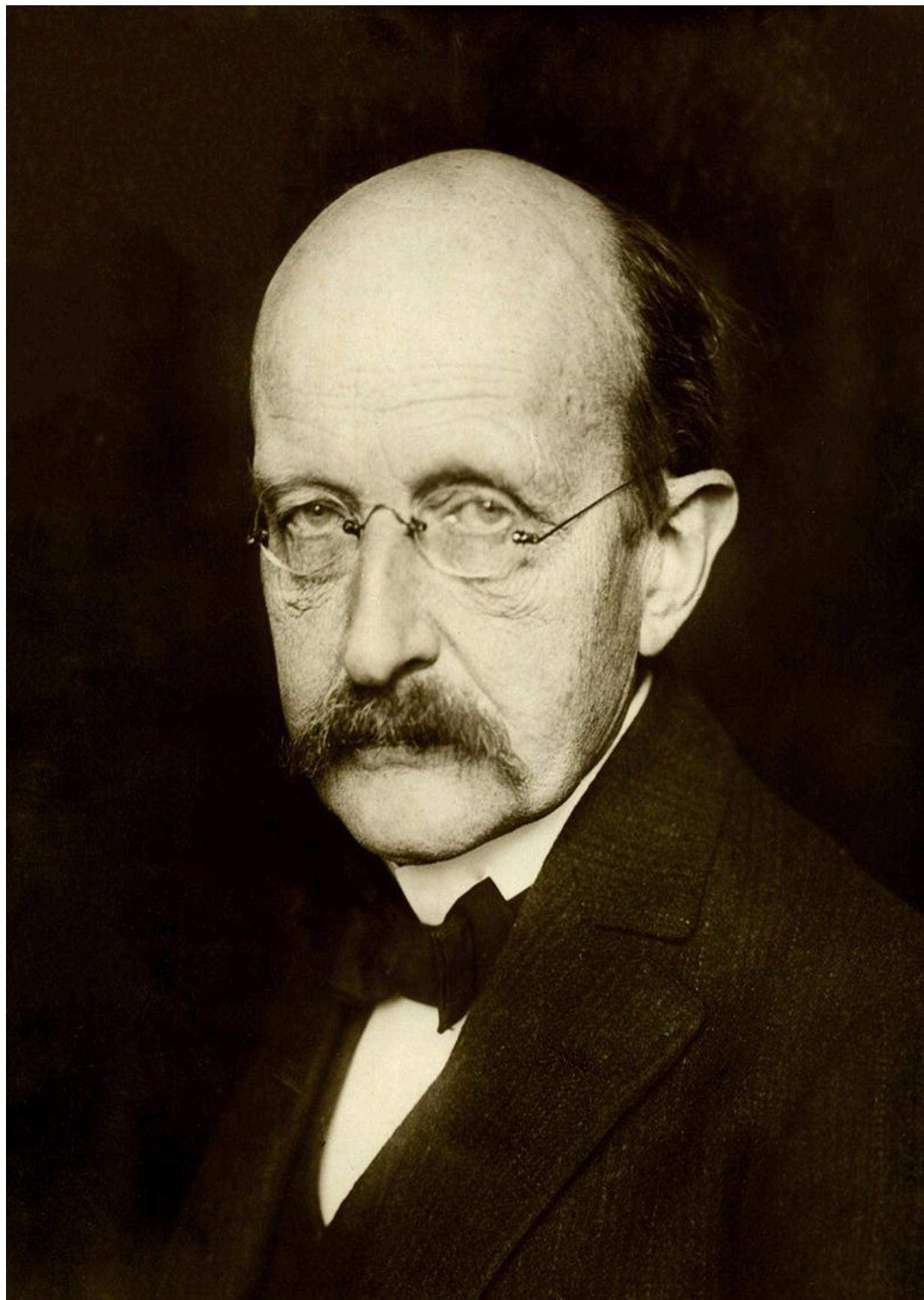

[Figure 4.19 Max Planck solved the radiation problem by assuming that energie...](#)

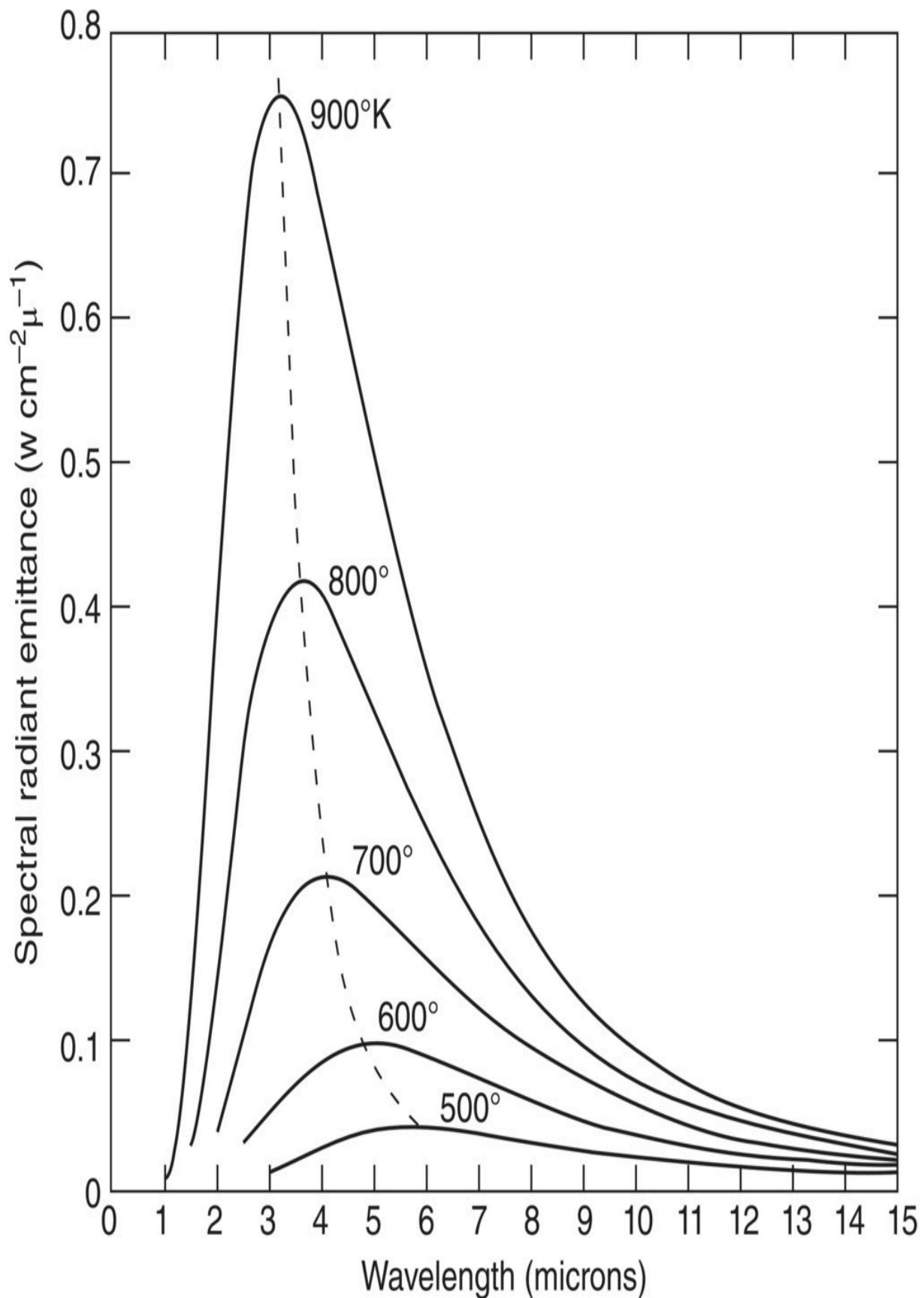

[Figure 4.20 The spectral emittance of a blackbody as a function of wavelengt...](#)

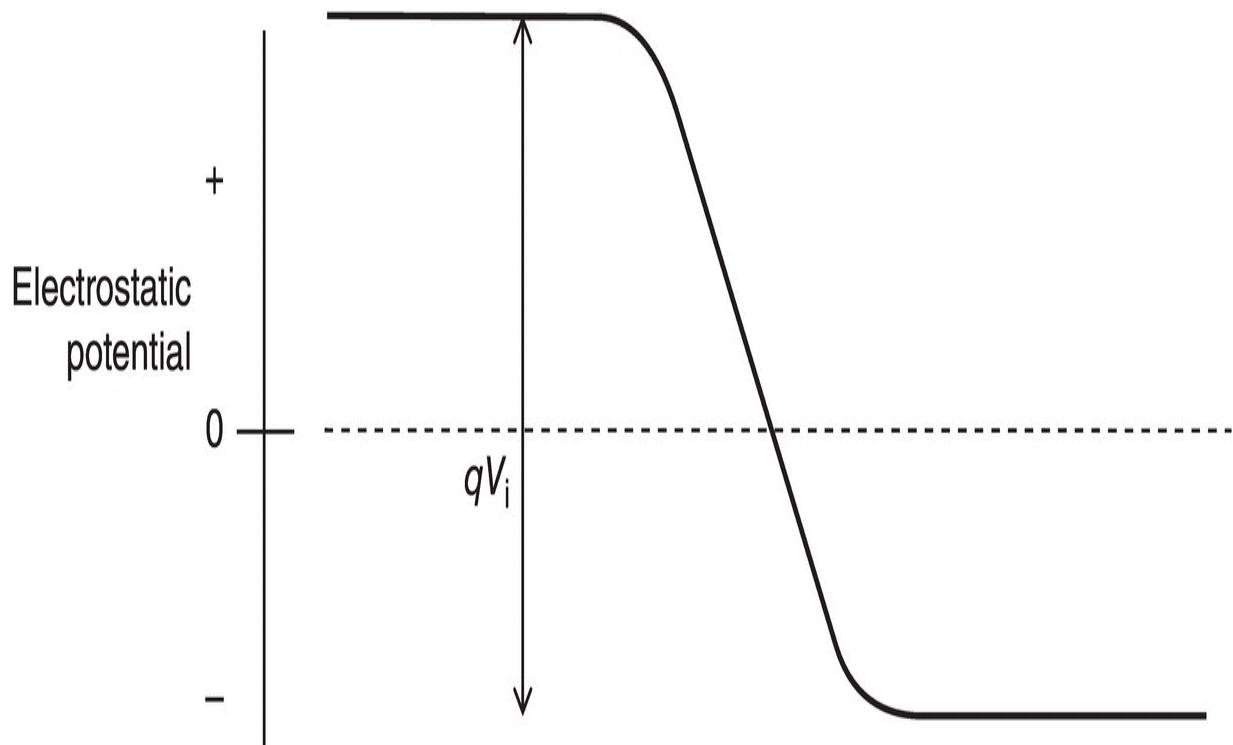

## Chapter 5

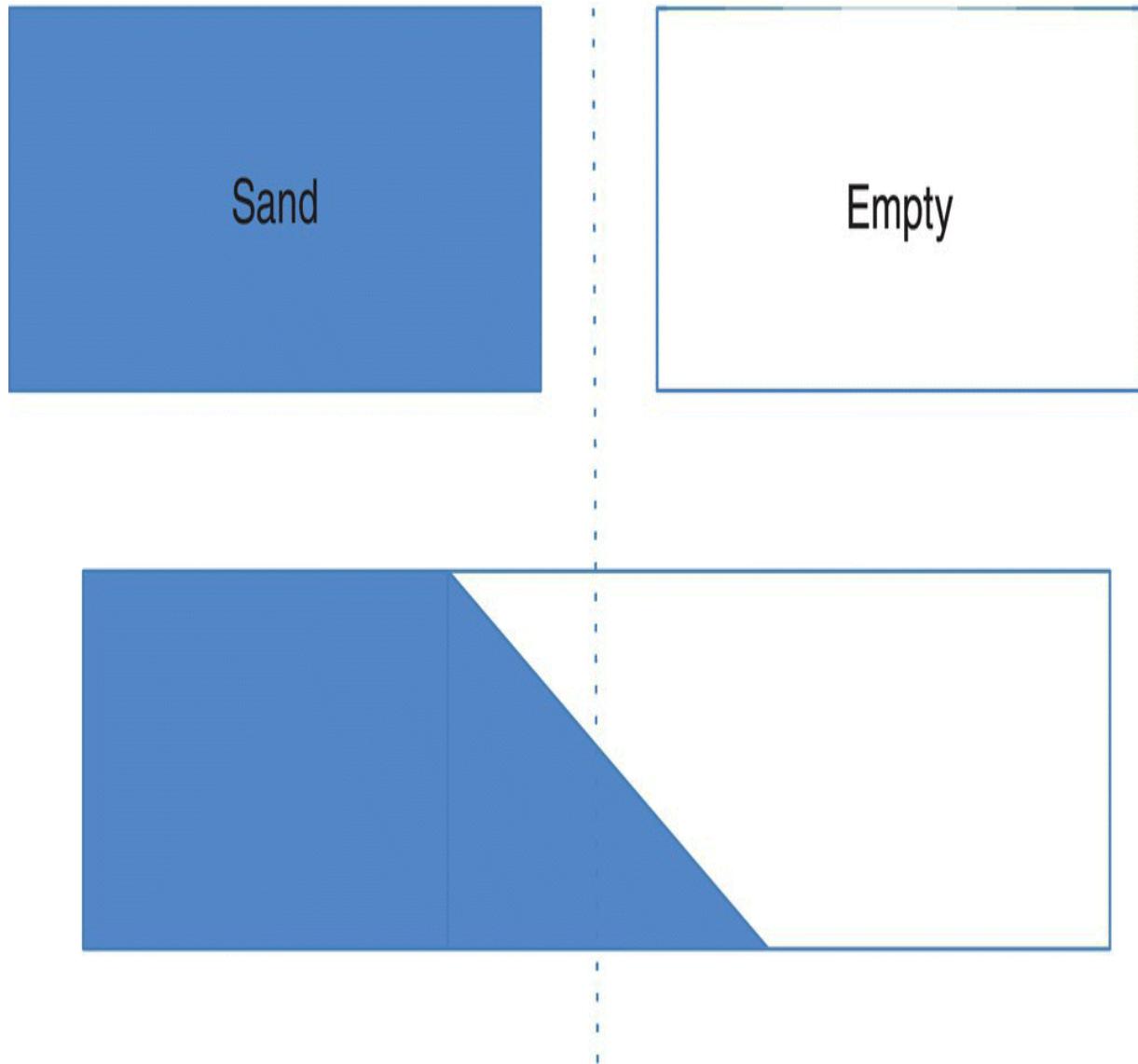

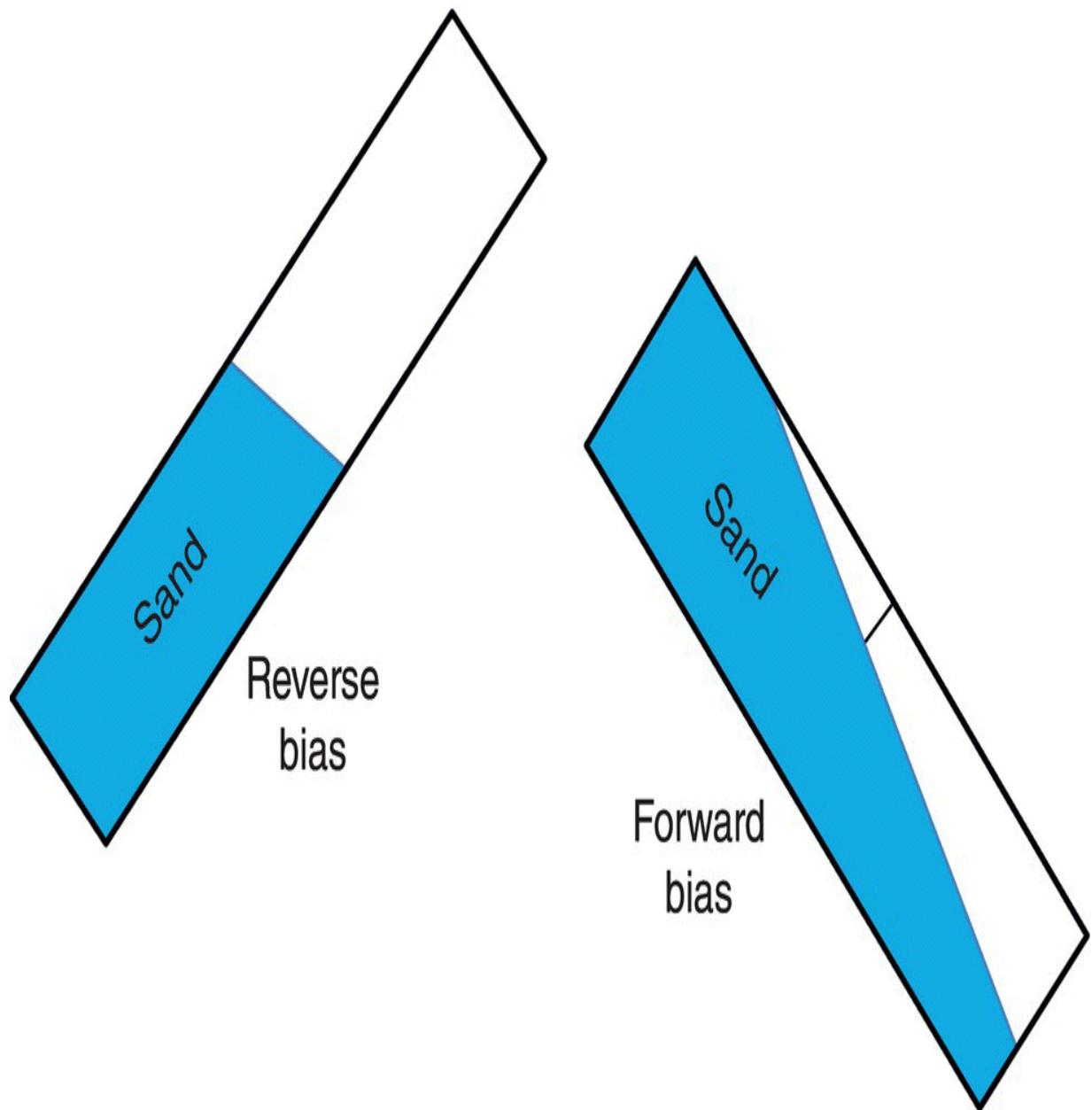

[Figure 5.1 If a box full of sand is placed adjacent to an empty one, the san...](#)

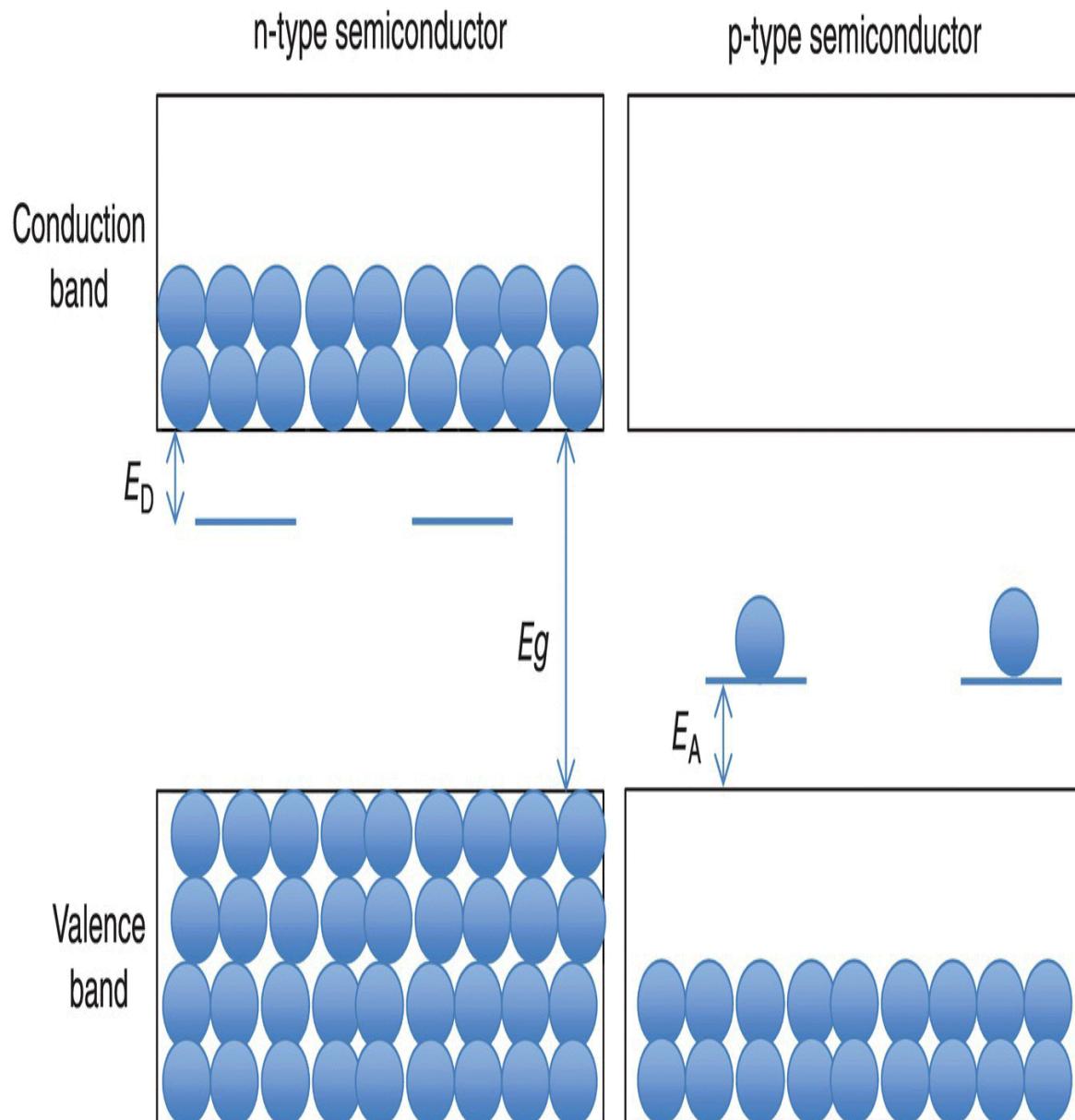

[Figure 5.2 An n-type semiconductor at room temperature has lots of electrons...](#)

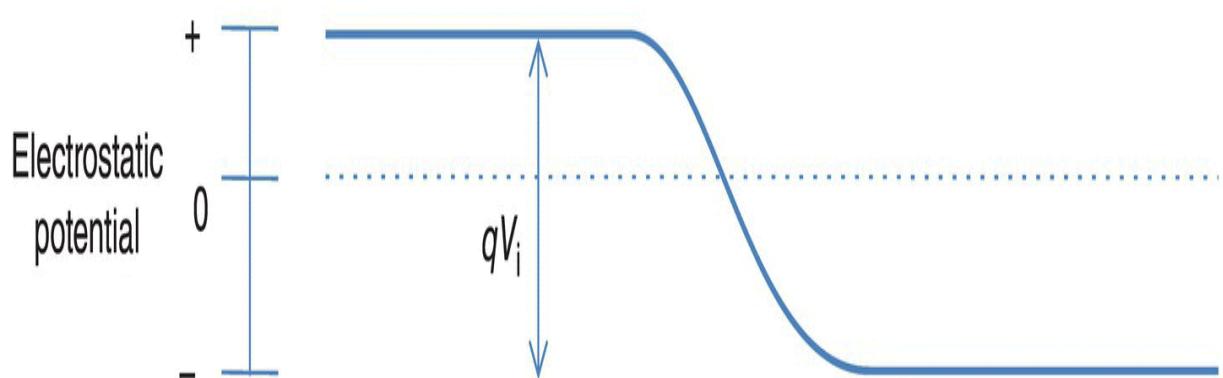

[Figure 5.3 When there is no separation between the p- and n-type semiconduct...](#)

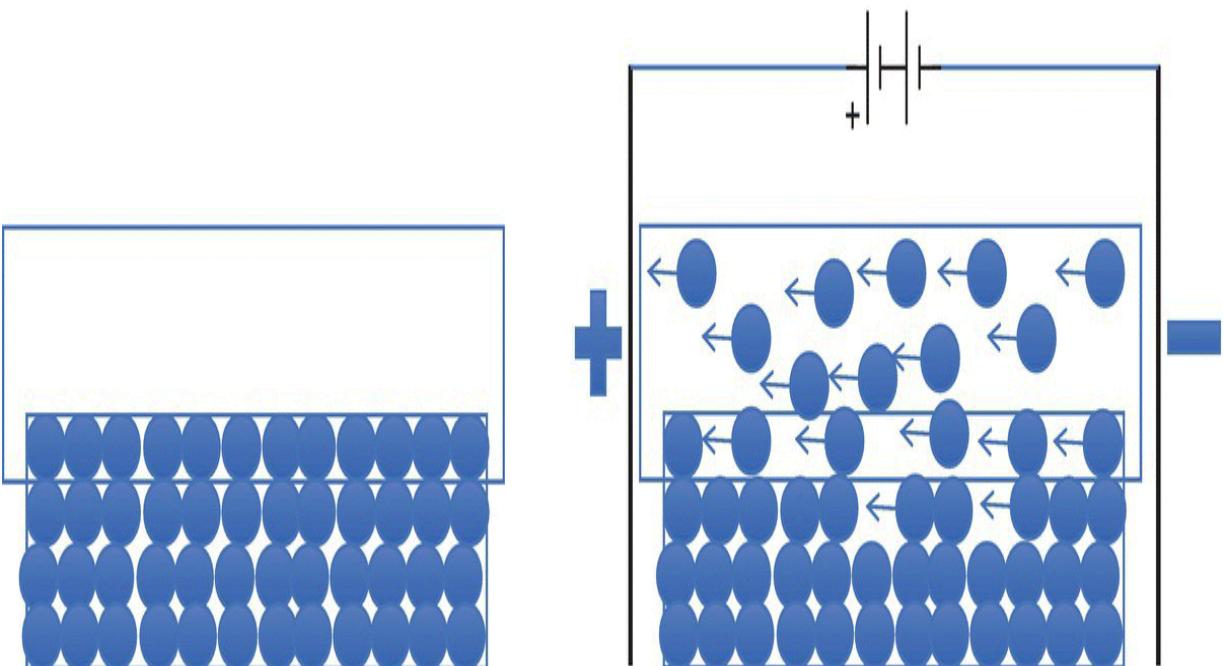

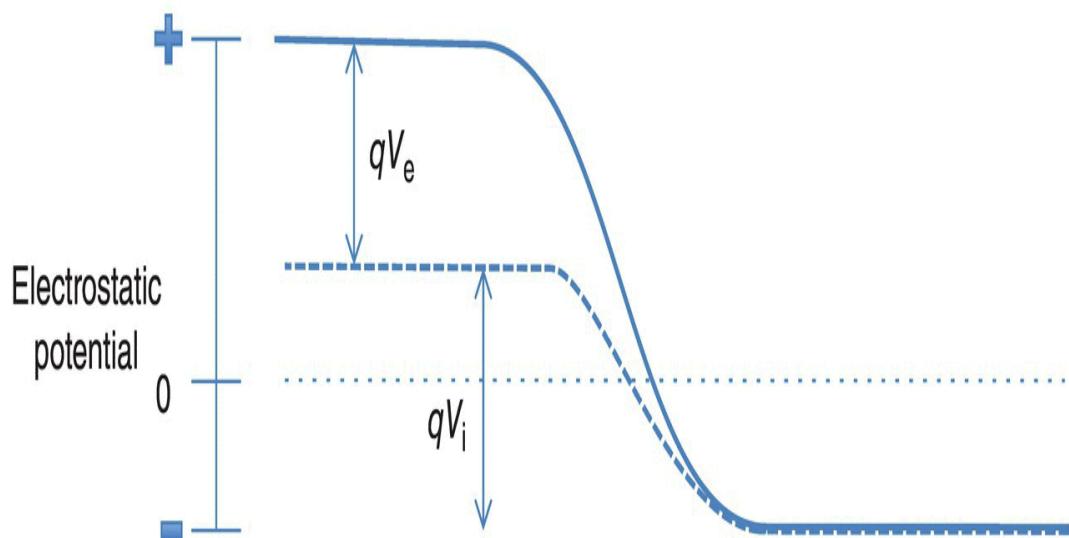

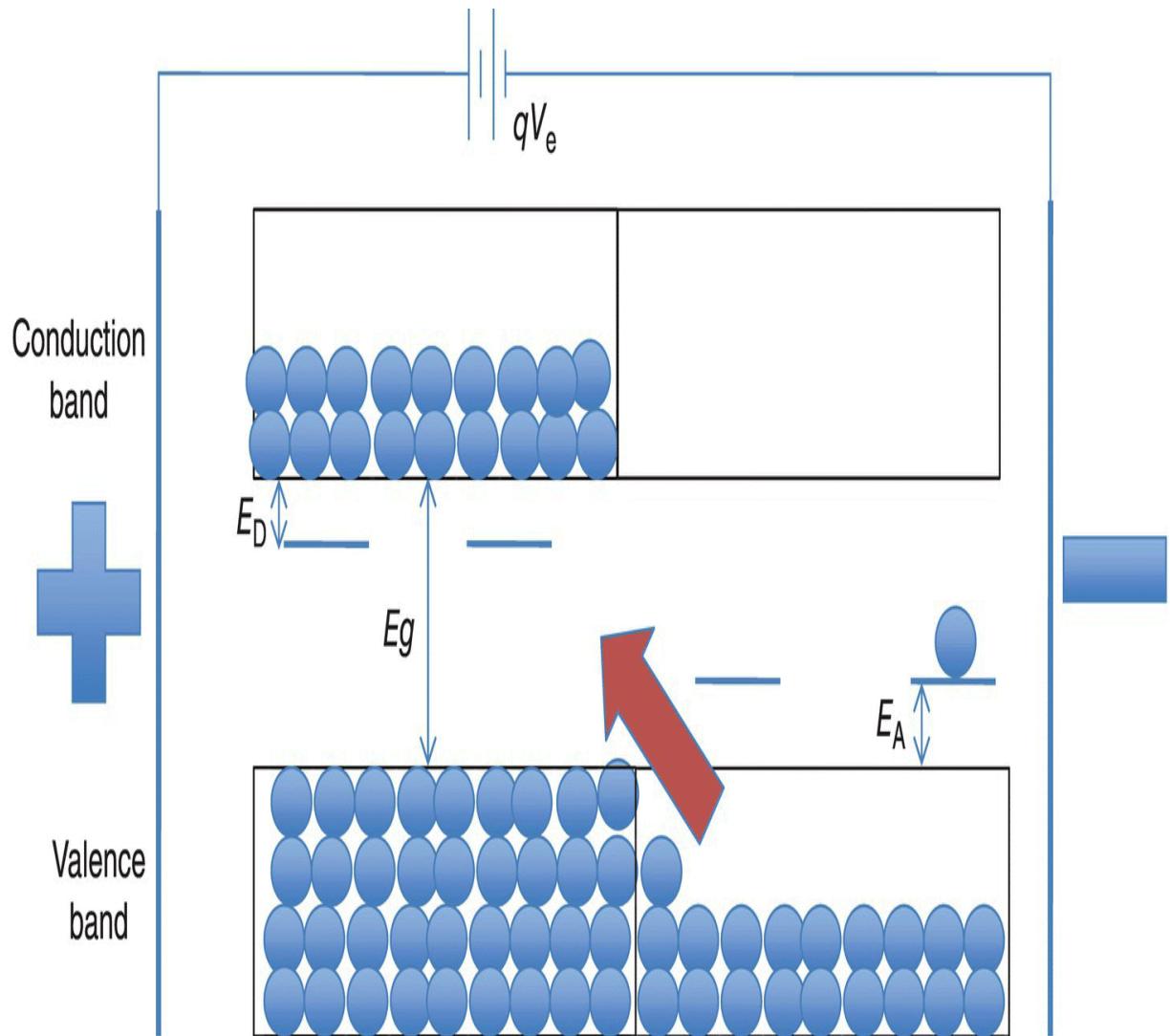

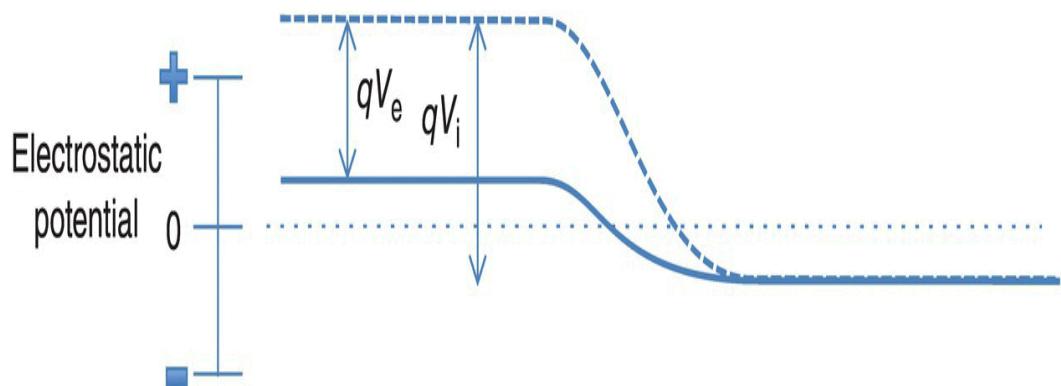

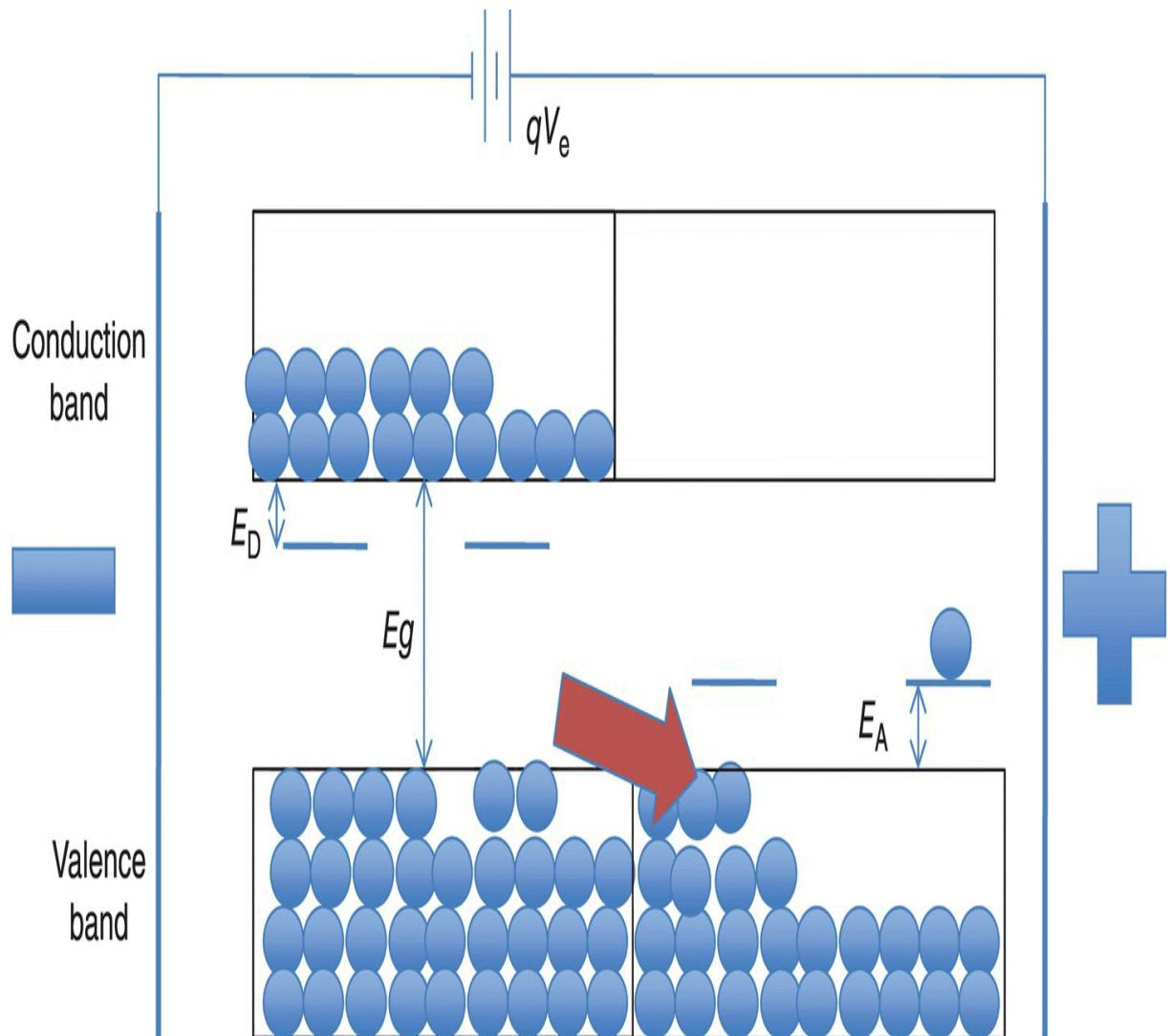

[Figure 5.4 A positive potential in the n-type semiconductor pulls electrons ...](#)

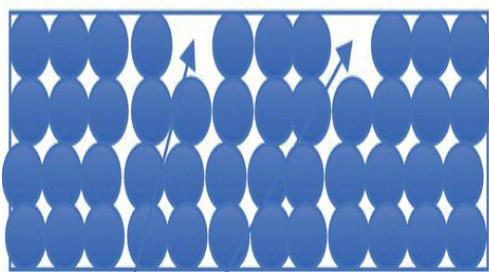

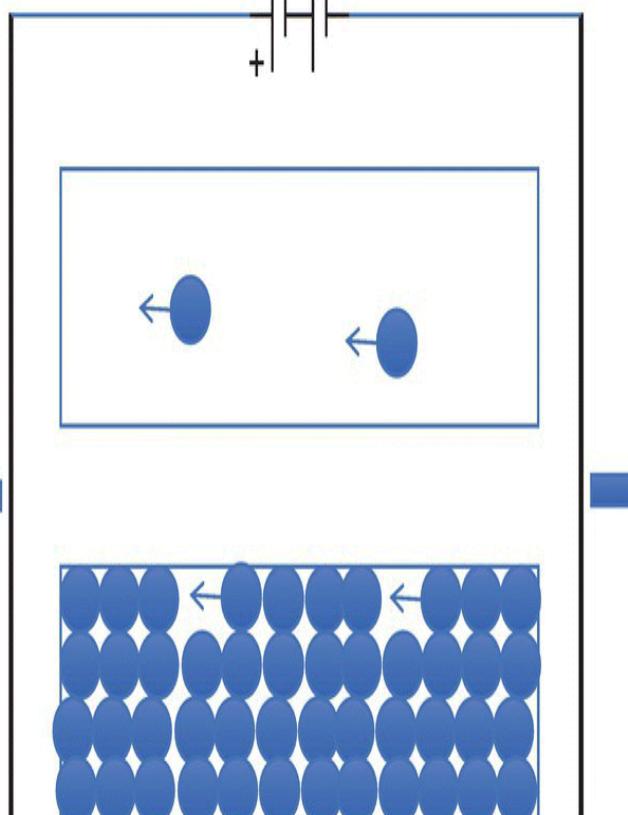

[Figure 5.5 A positive potential applied to the p-type semiconductor attracts...](#)

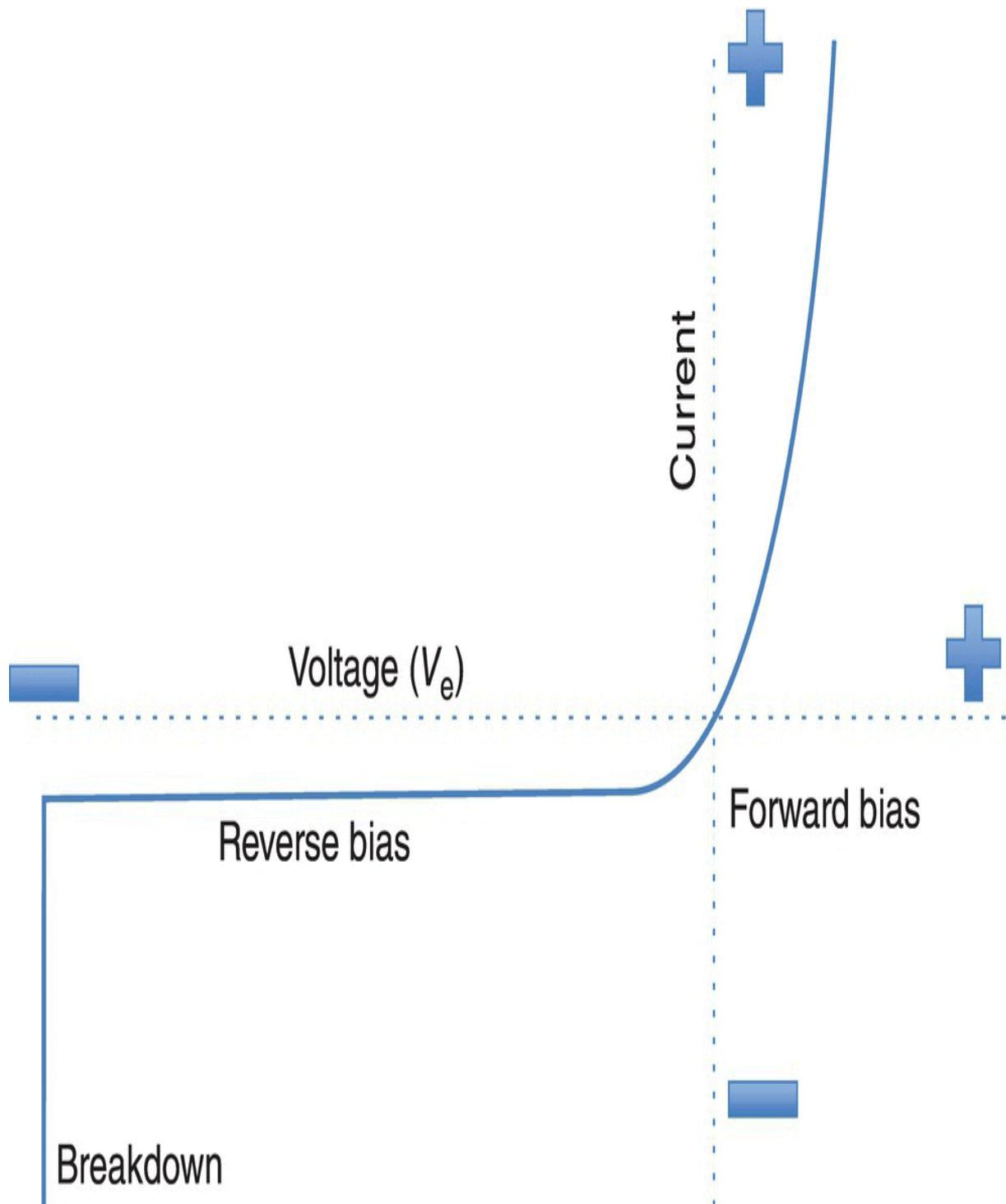

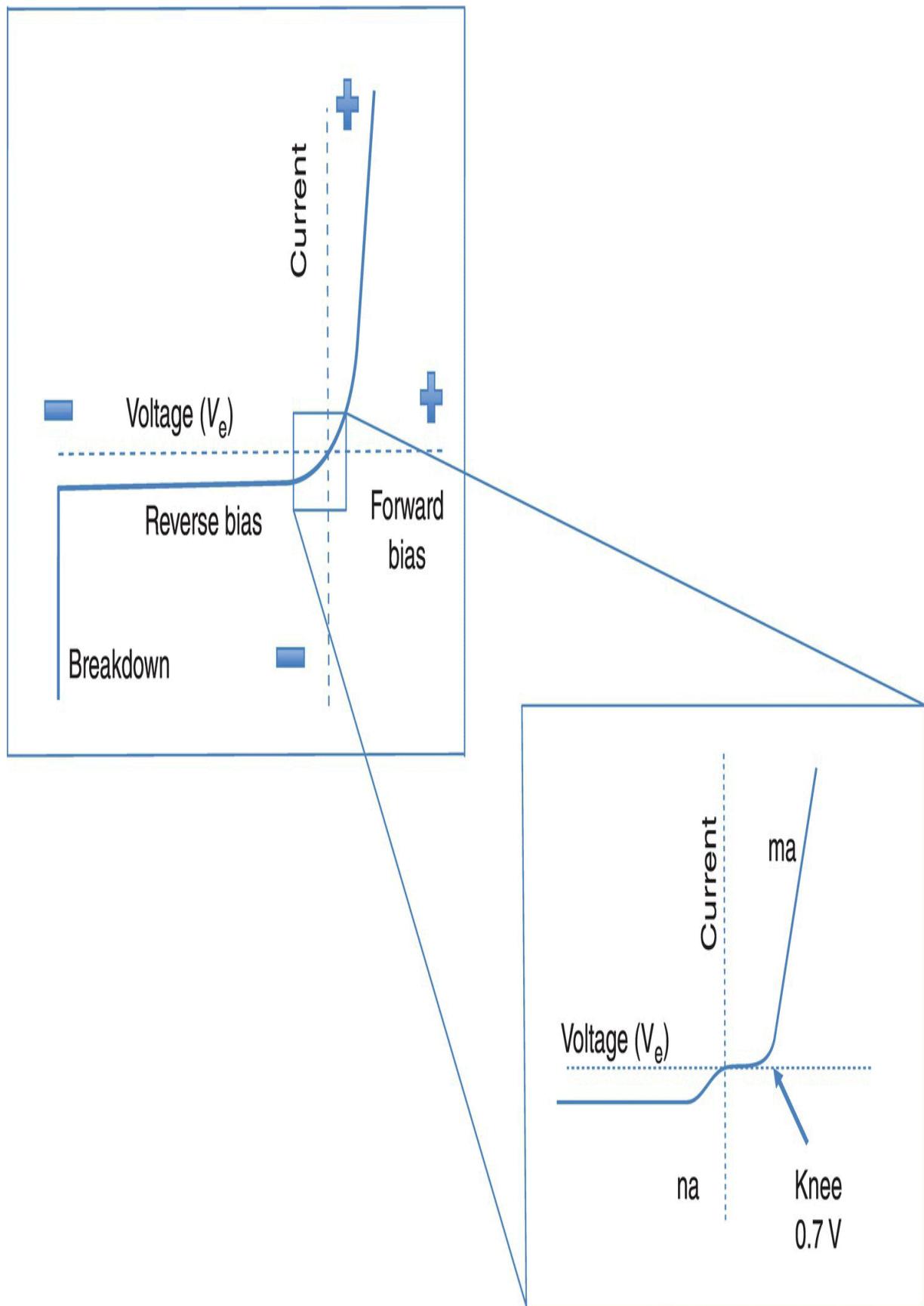

[Figure 5.6 The characteristic curves of a pn-junction show current increasing...](#)

[Figure 5.7 The analogy of the sand boxes with a tilt toward the full box, re...](#)

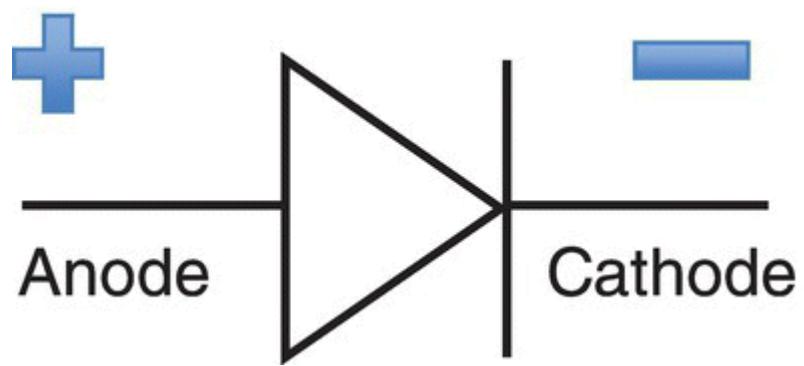

[Figure 5.8 The symbol for a diode showing the direction of the current when ...](#)

[Figure 5.9 Diode characteristics showing the turn-on voltage, or the knee. N...](#)

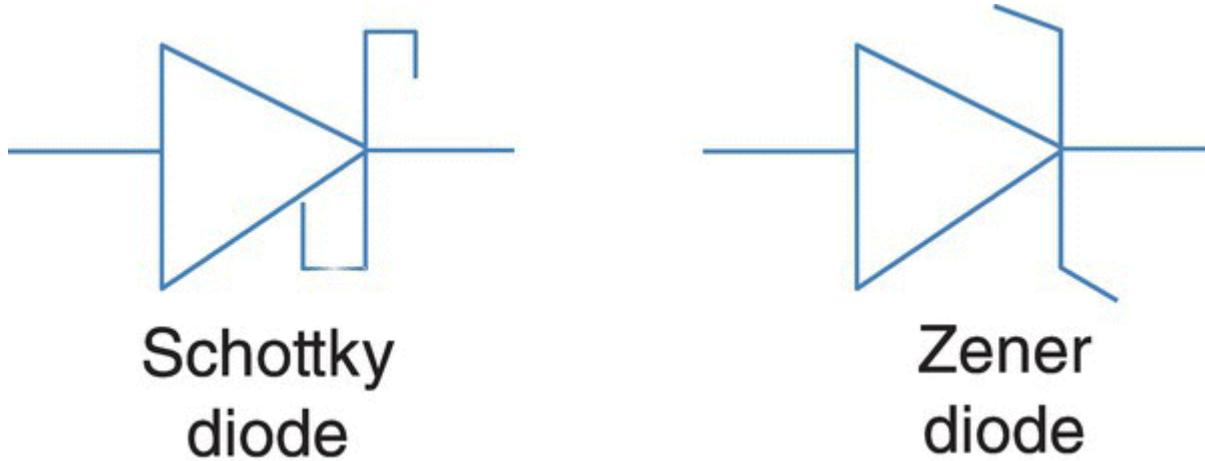

[Figure 5.10 Symbols for Schottky and Zener diodes.](#)

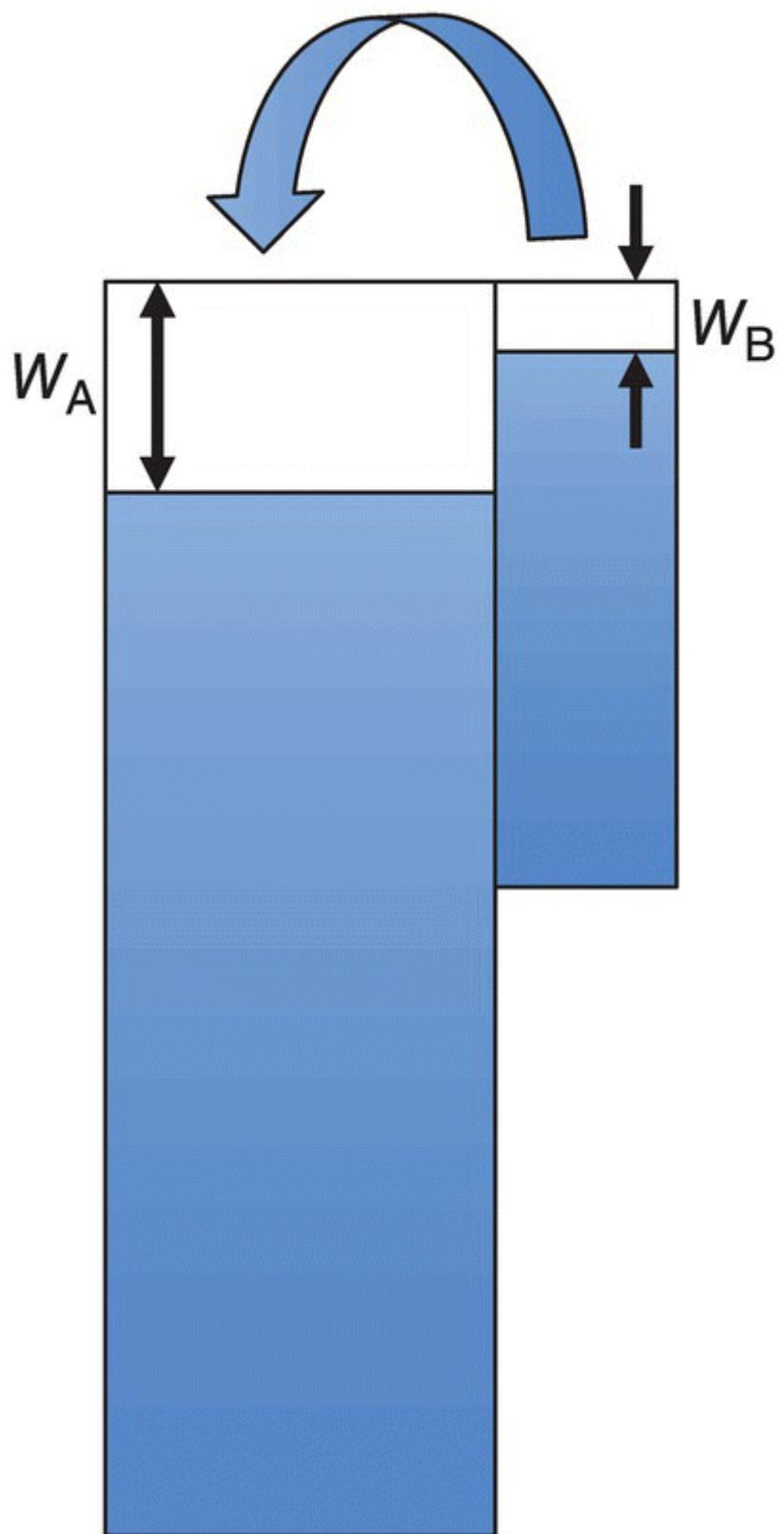

[Figure 5.11 The water in the small container on the right will boil over int...](#)

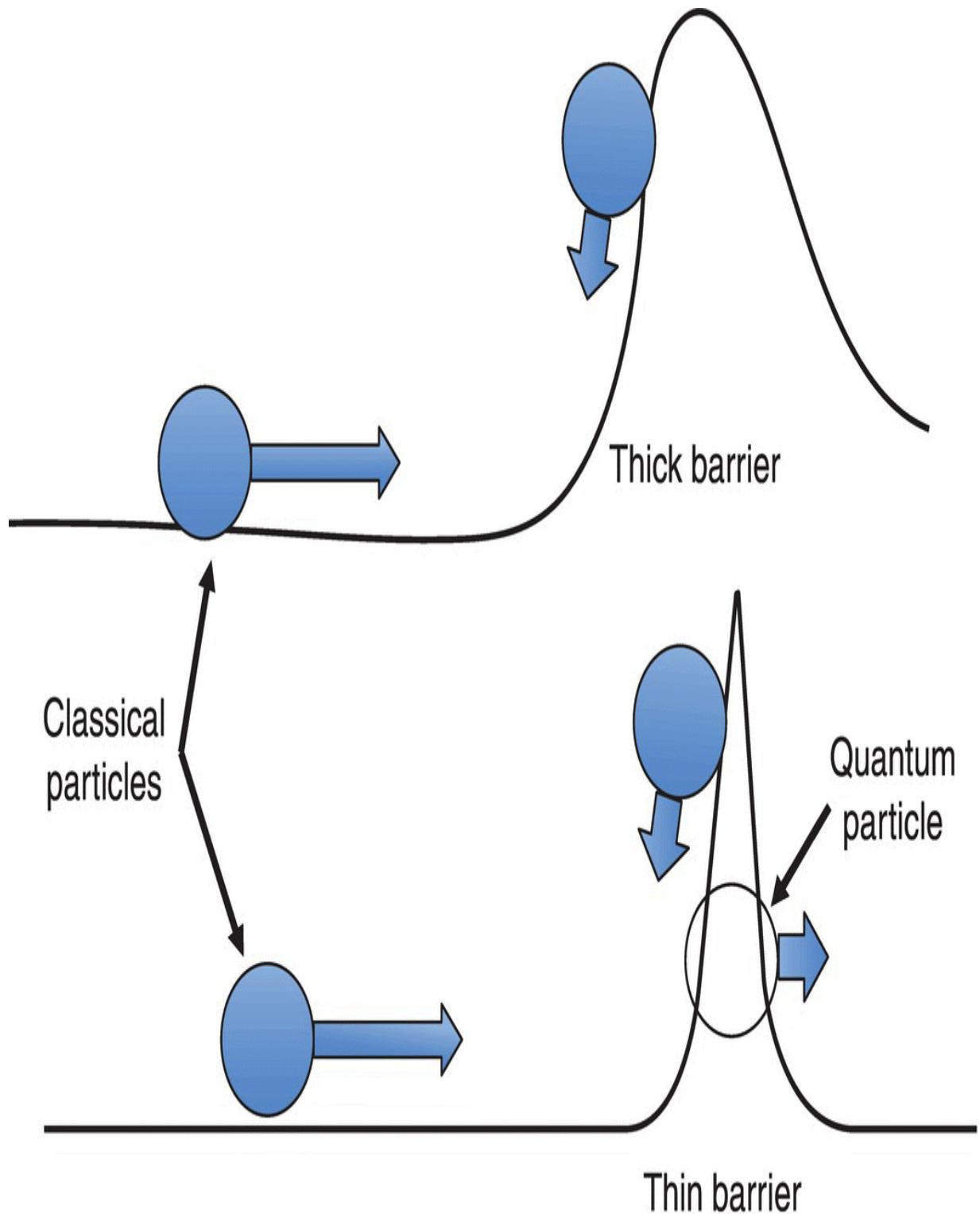

[Figure 5.12 A classical ball will cross the barrier only if its energy is high...](#)

[Figure 5.13 In quantum mechanics the probability of finding an electron is even...](#)

[Figure 5.14 A Zener diode has such a thin transition region \(A\), that electrons...](#)

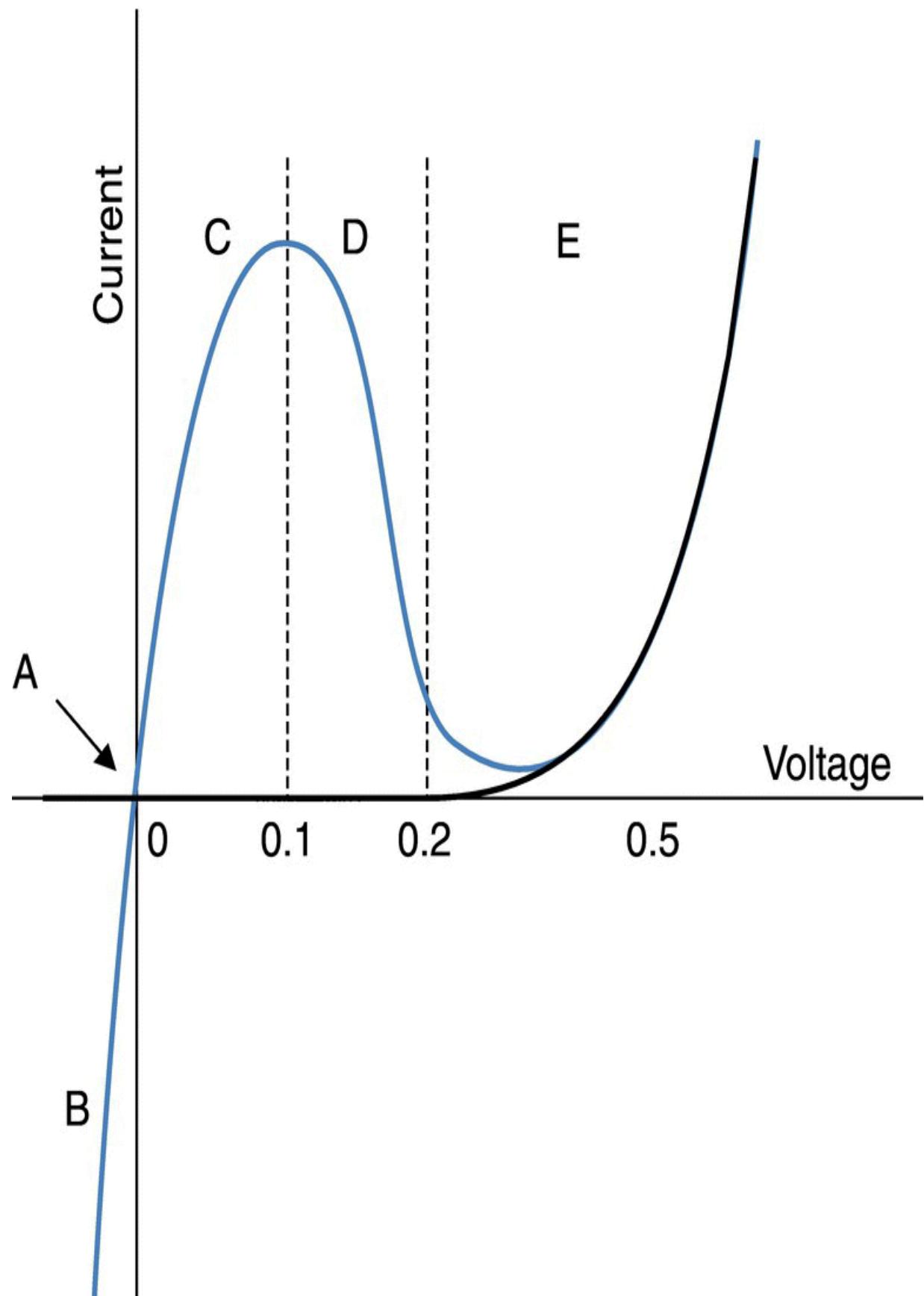

[Figure 5.15 The tunnel diode characteristics show a high reverse bias current...](#)

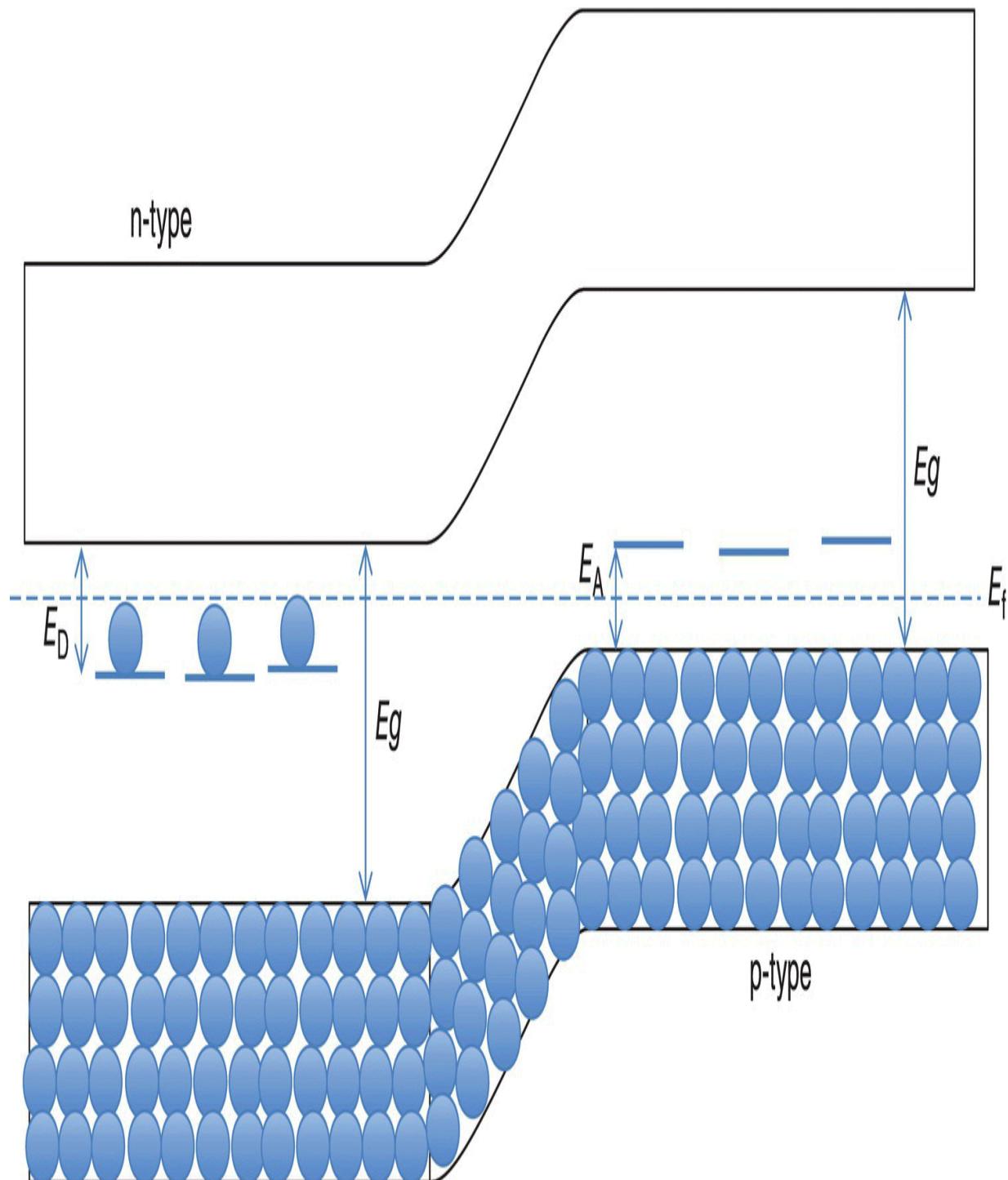

[Figure 5.16 The pn-junction at 0 K has all the levels below the Fermi level ...](#)

[Figure 5.17 The same pn-junction as in Figure 5.16 but now at 300 K it has even...](#)

[Figure 5.18 If the p-type semiconductor has half the concentration of impurities...](#)

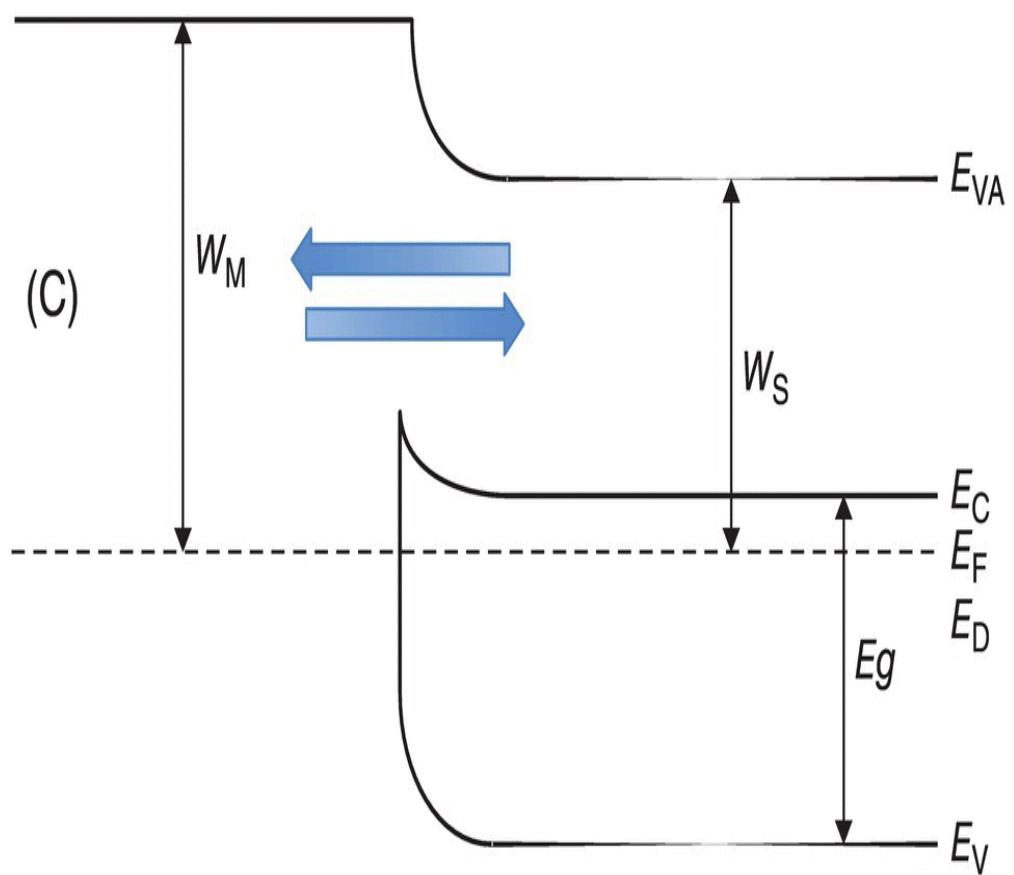

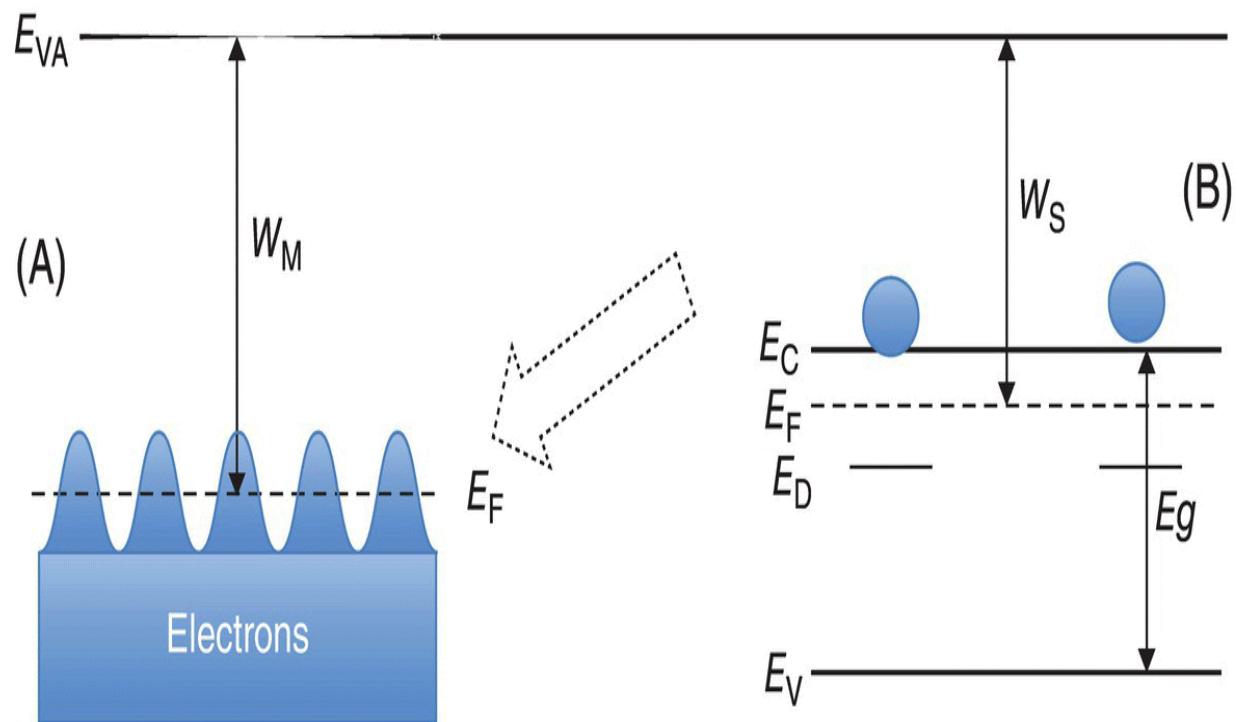

[Figure 5.19 The vacuum level  \$E\_{VA}\$  is the same for all materials. The Fermi level...](#)

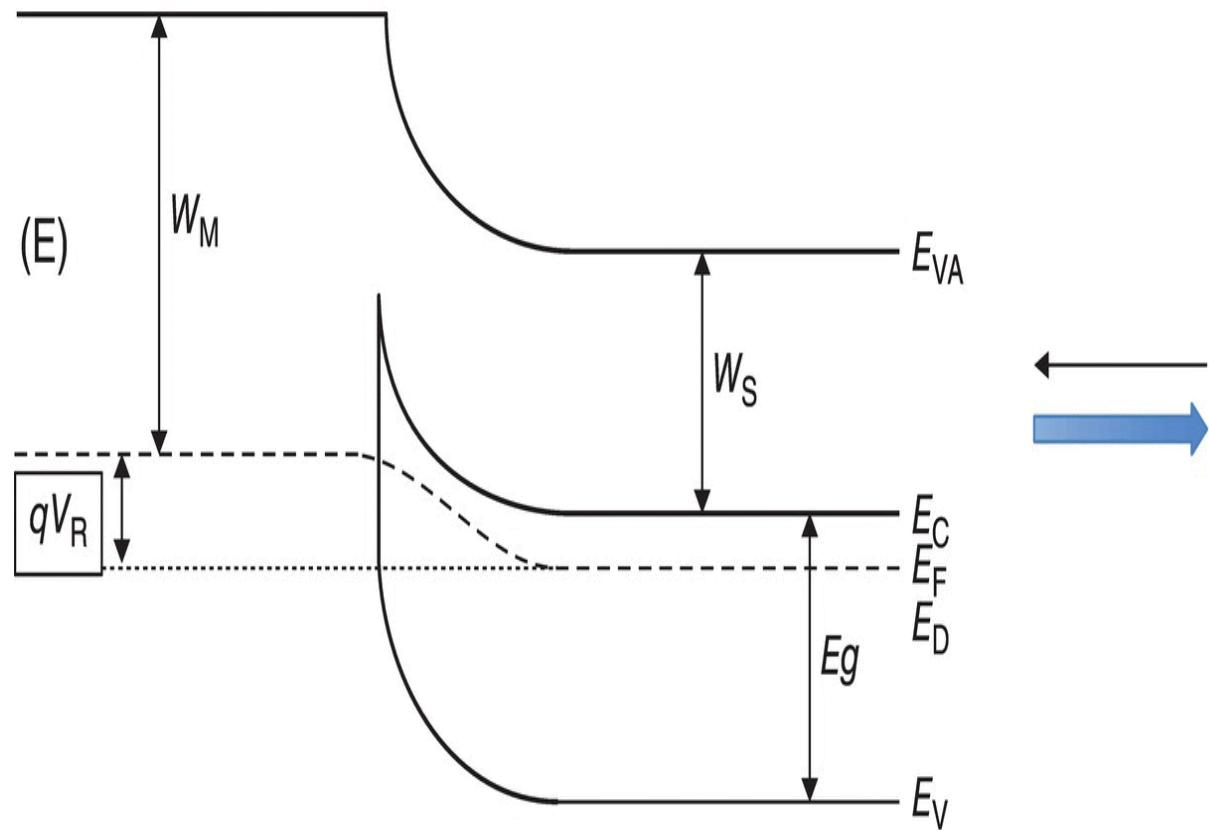

[Figure 5.20 The Shockley diode under the forward bias condition \(D\) the barrier...](#)

## Chapter 6

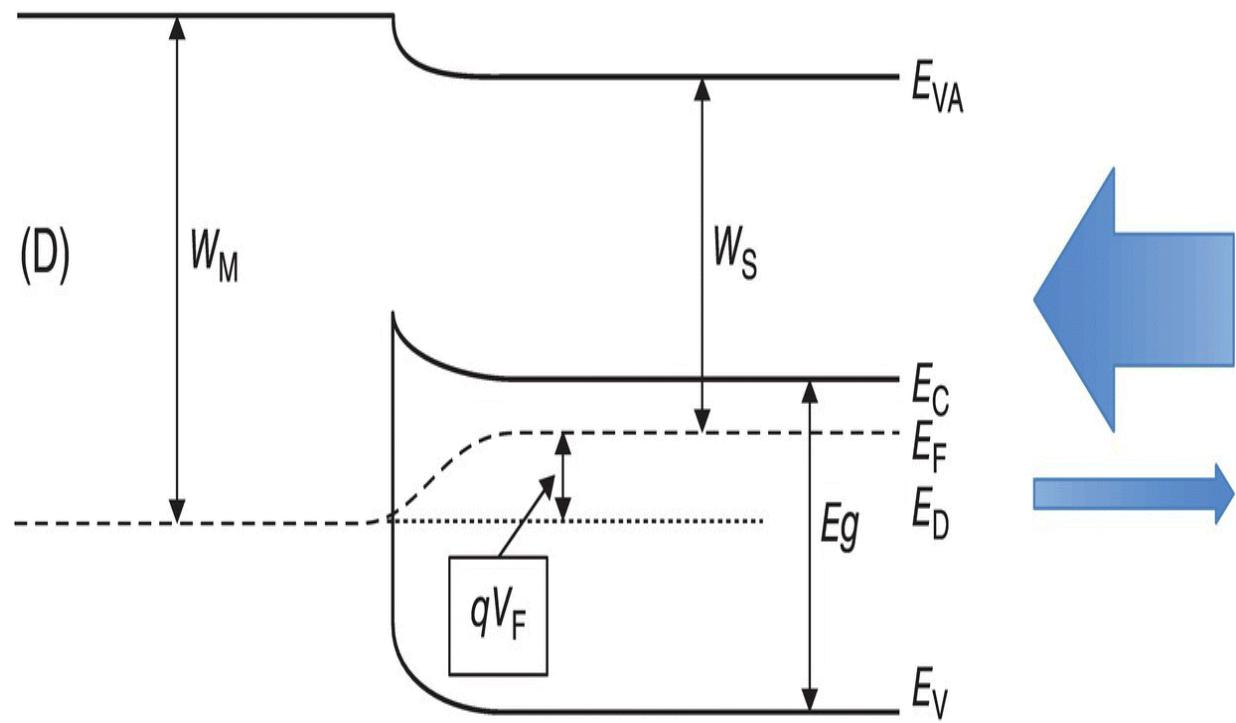

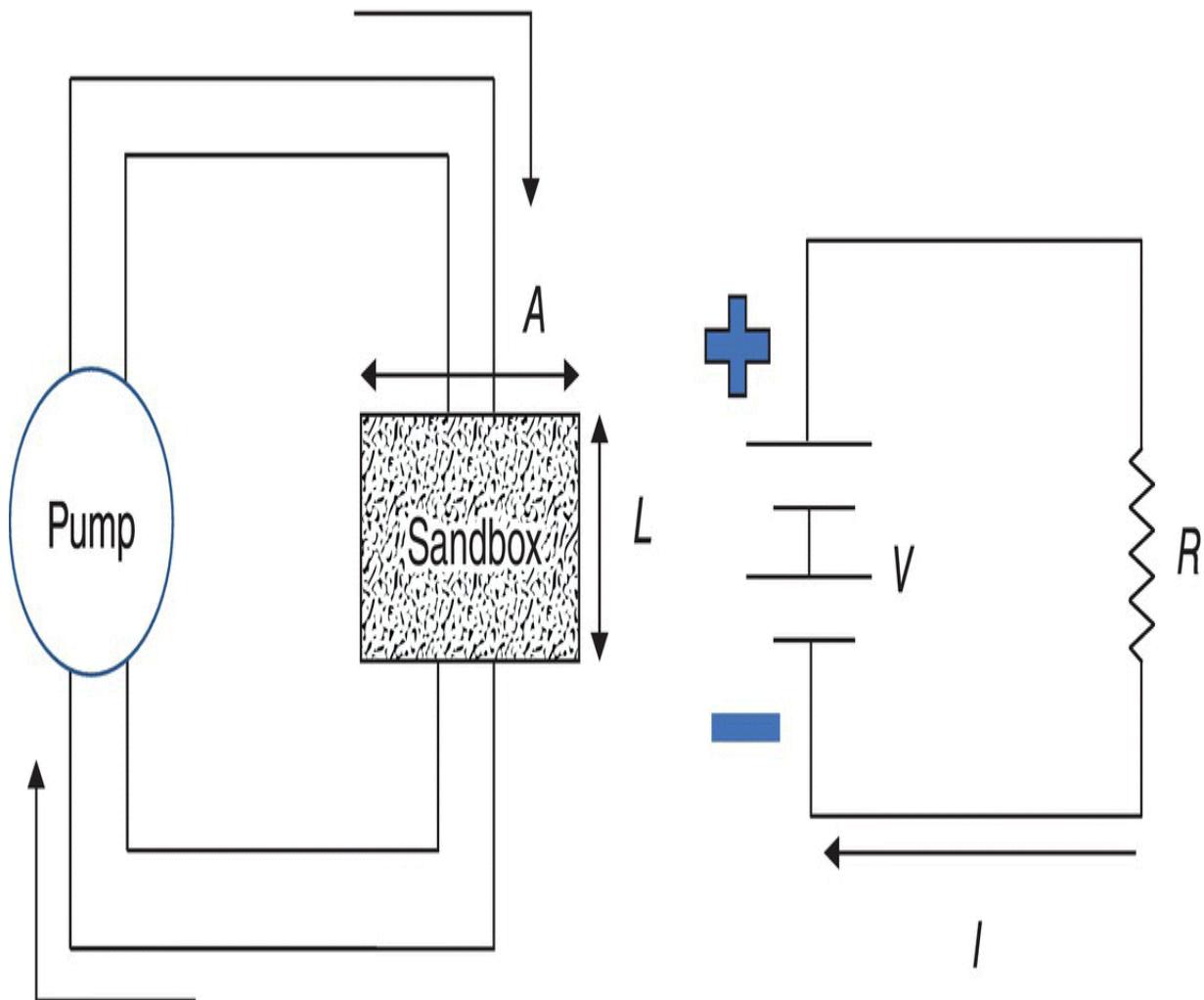

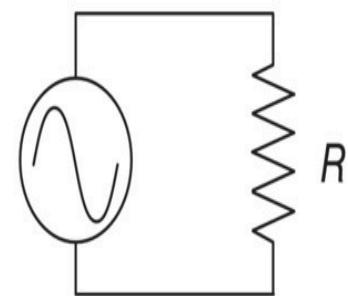

[Figure 6.1 A fluidic analogue of an electrical circuit with resistance to th...](#)

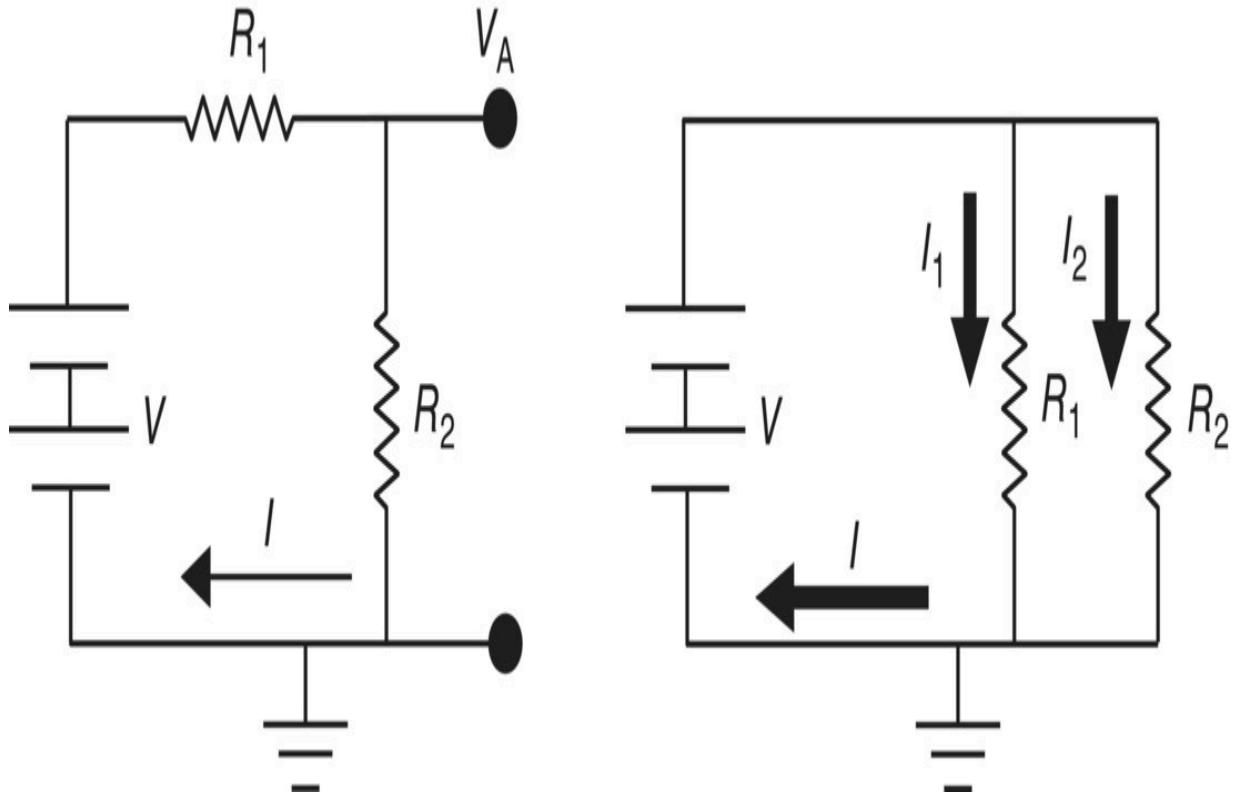

[Figure 6.2 Resistors in series \(left\) divides the voltage and in parallel \(r...](#)

[Figure 6.3 A flexible membrane stores water. Water flows almost instantaneou...](#)

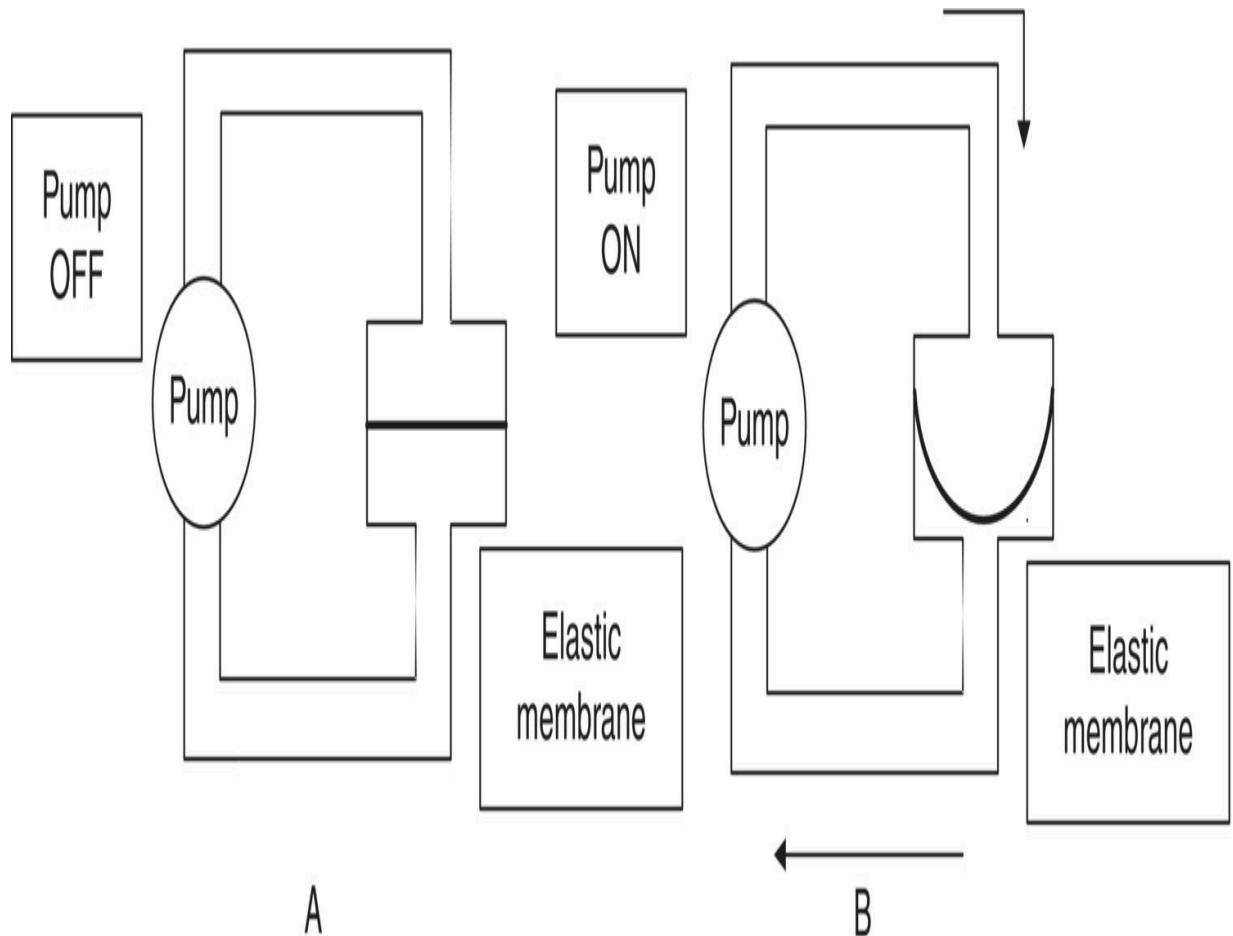

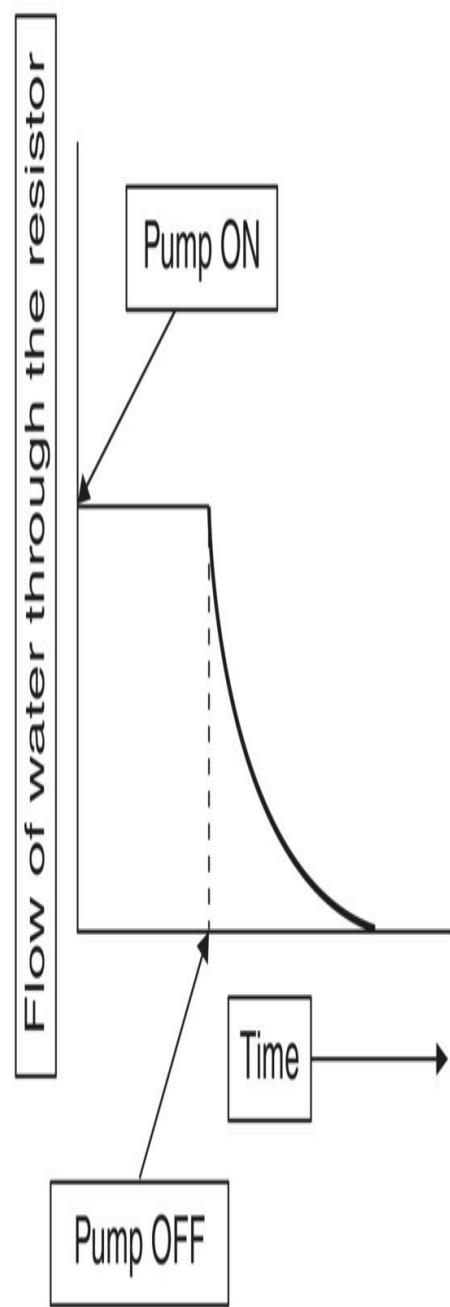

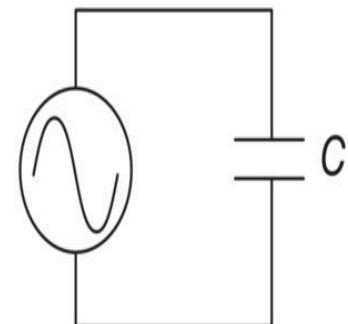

[Figure 6.4 When I turn the pump on, there is current through the sand box an...](#)

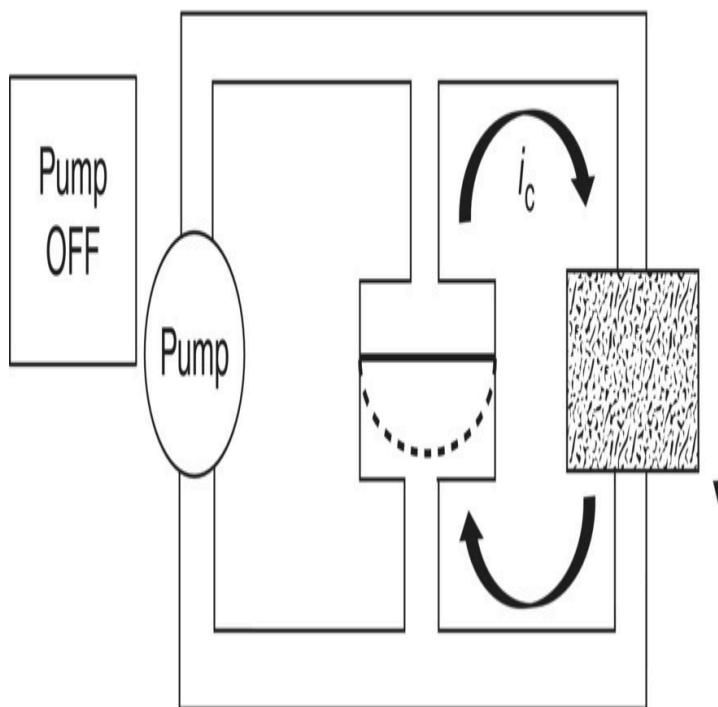

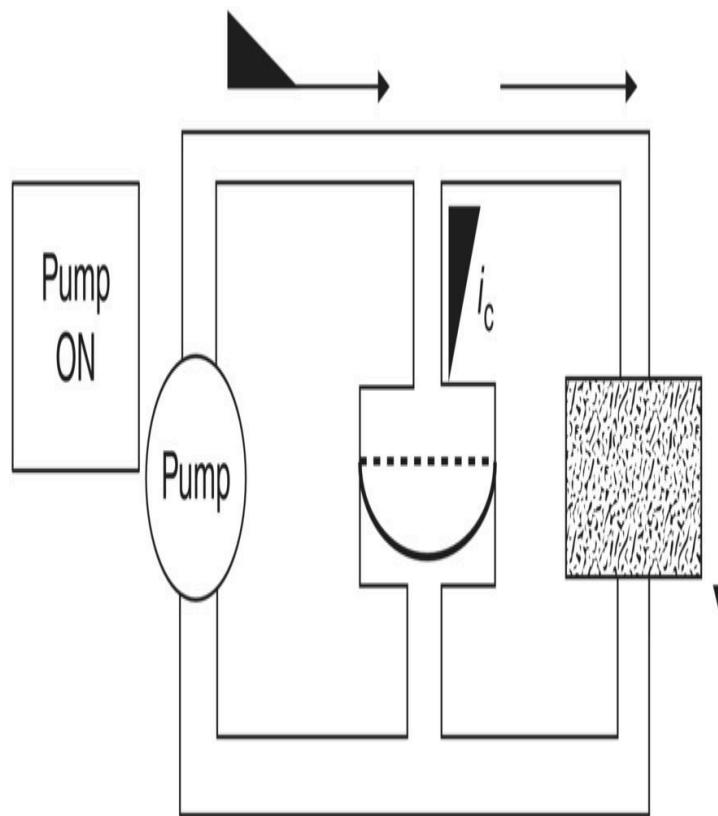

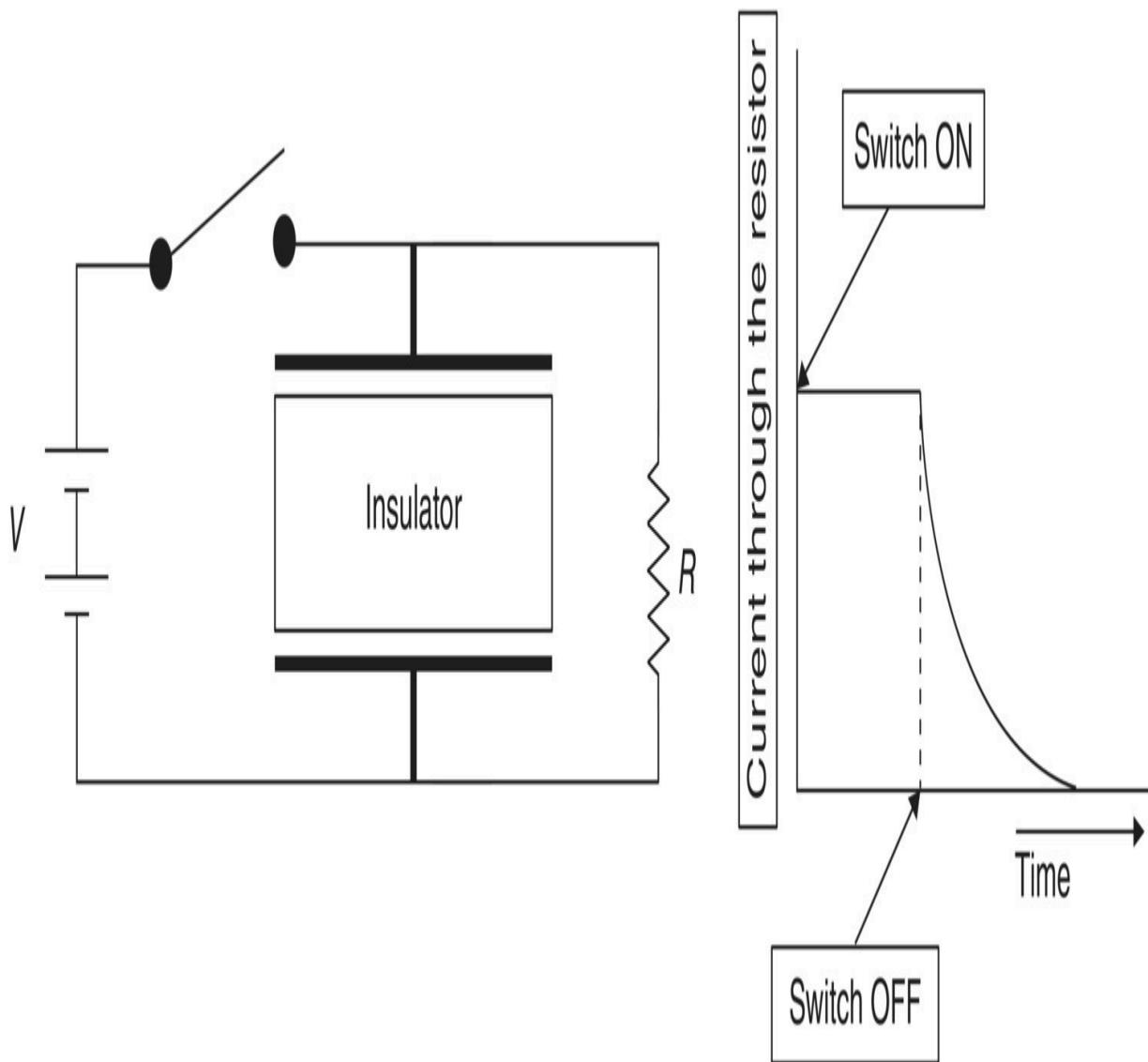

[Figure 6.5 A capacitor consists of two parallel plates separated by an insul...](#)

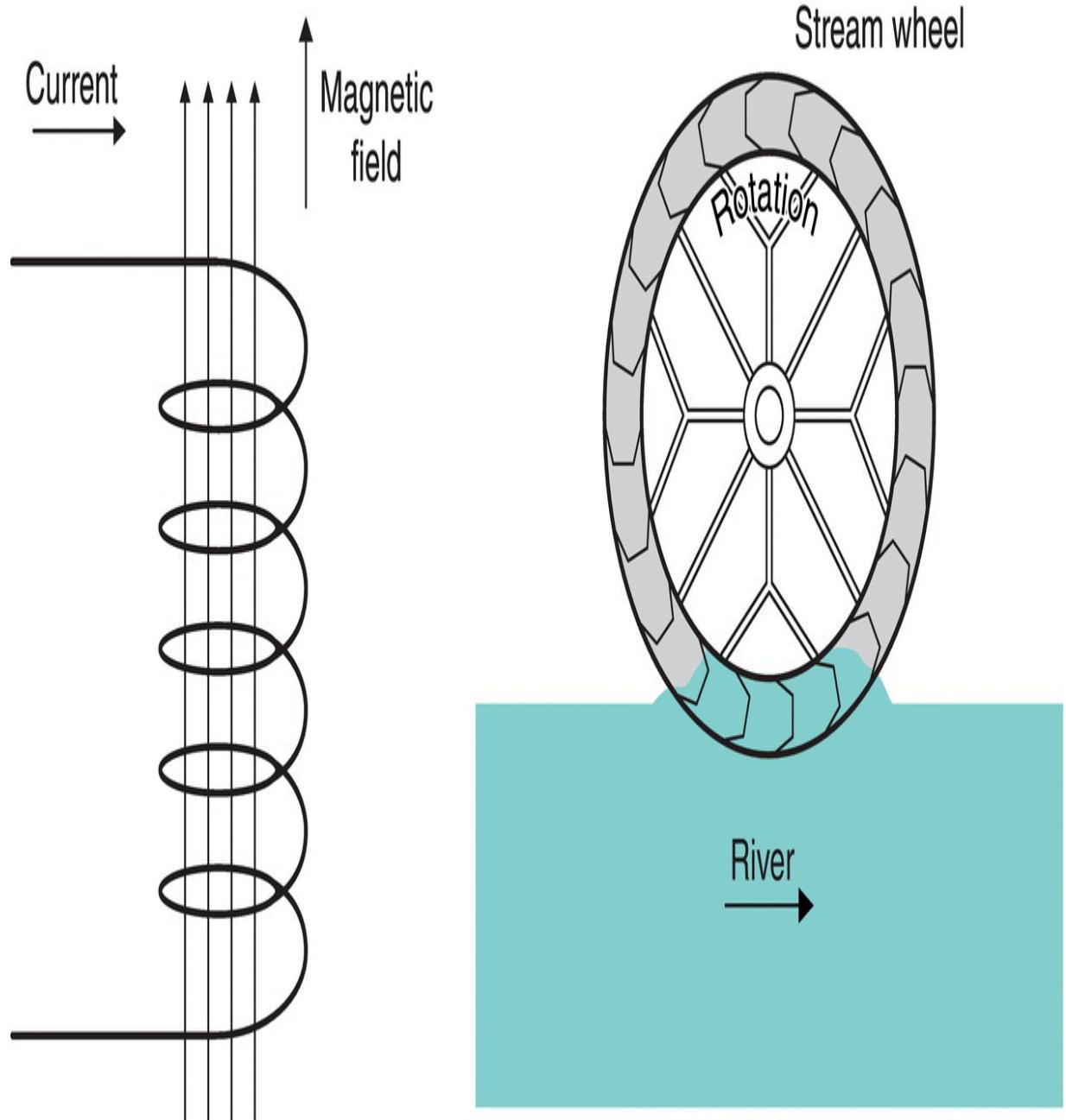

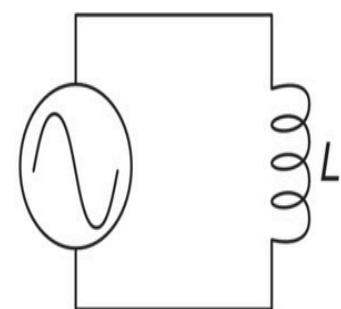

[Figure 6.6 An inductor stores electric energy in the form of a magnetic fiel...](#)

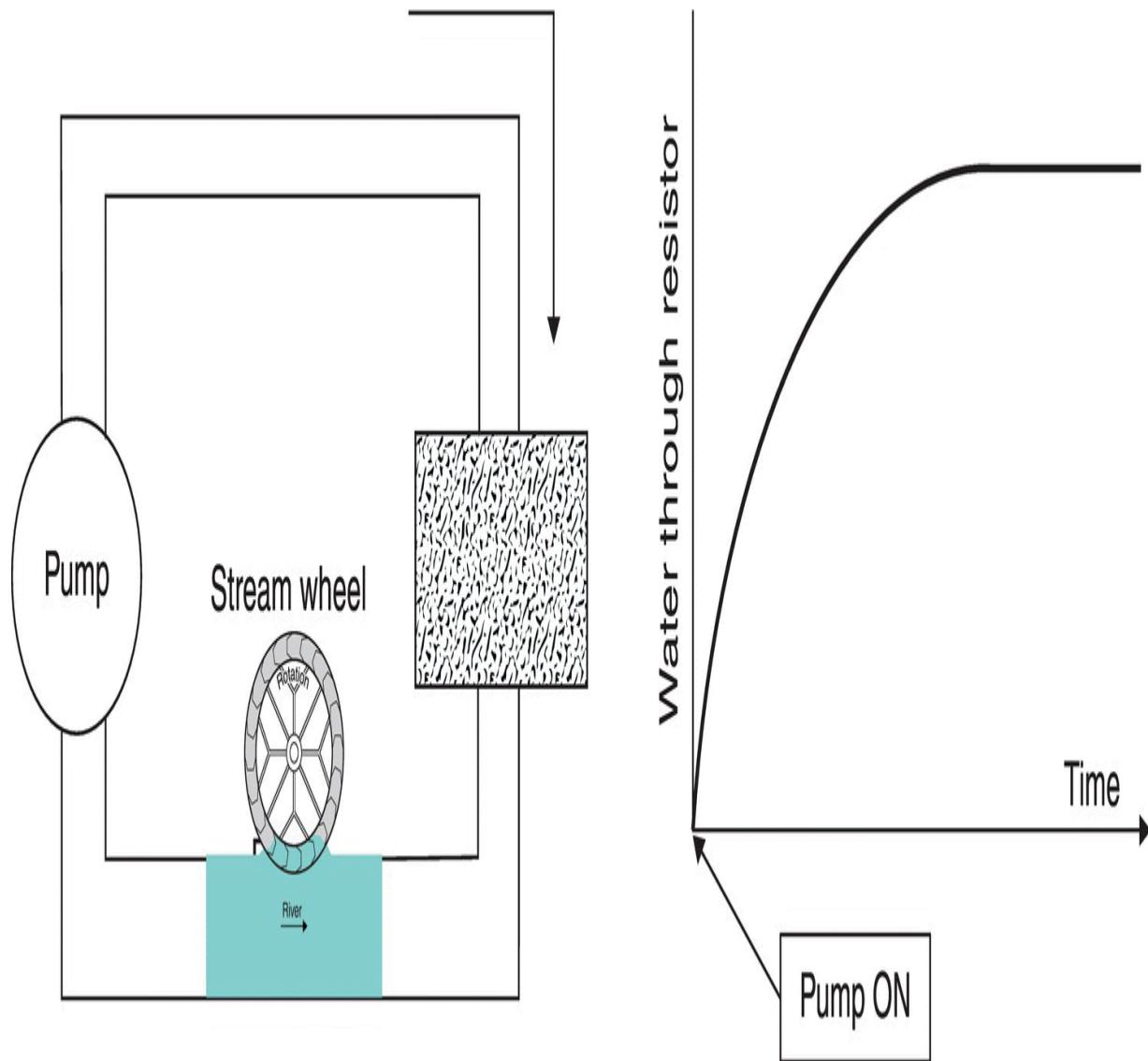

[Figure 6.7 When the pump is turned on, the water wheel starts moving, first ...](#)

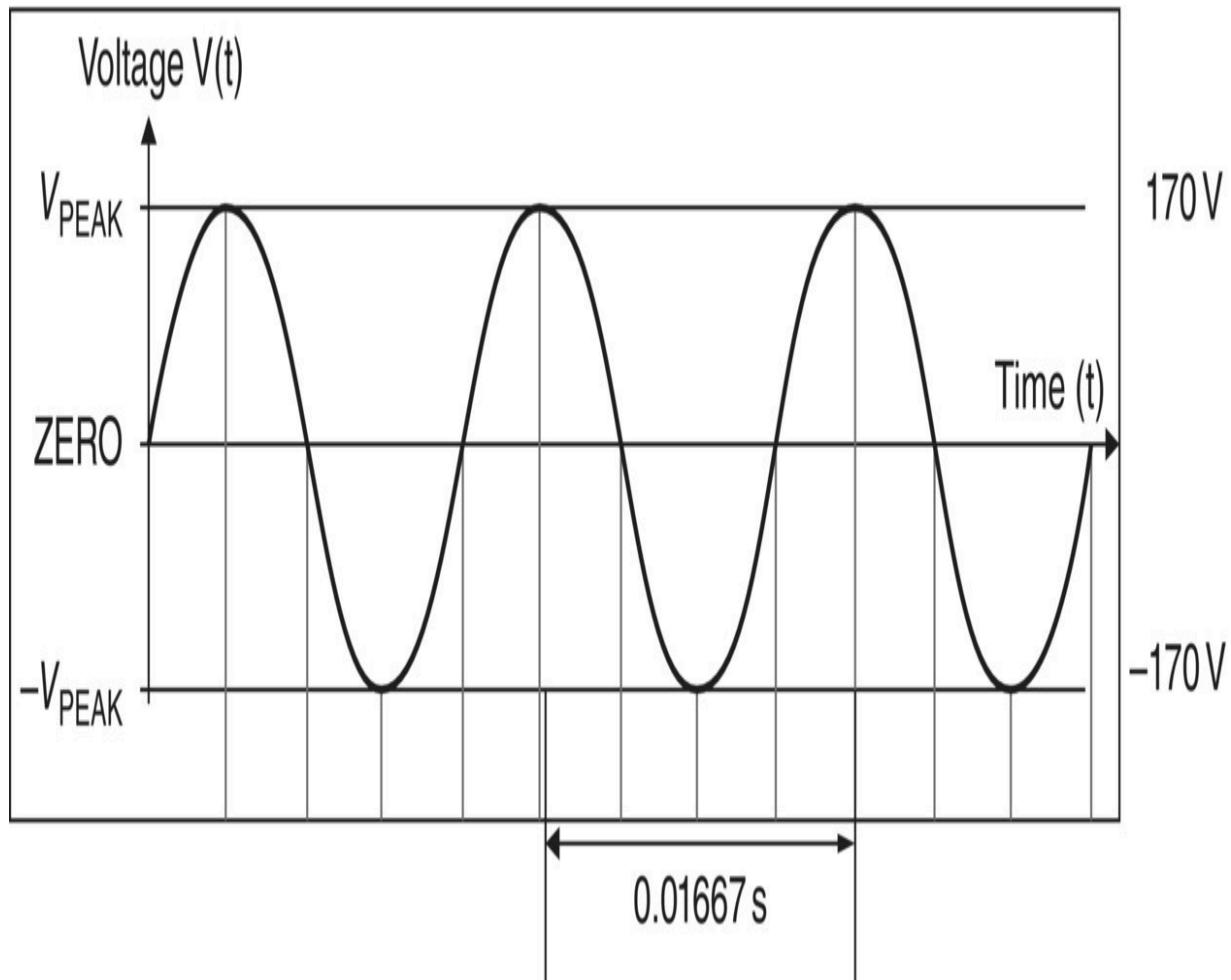

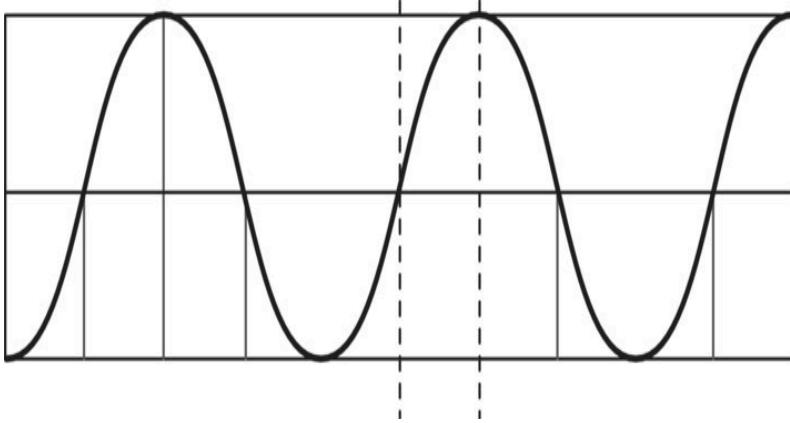

[Figure 6.8 The 120 V electrical oscillating voltage, AC, in the USA.](#)

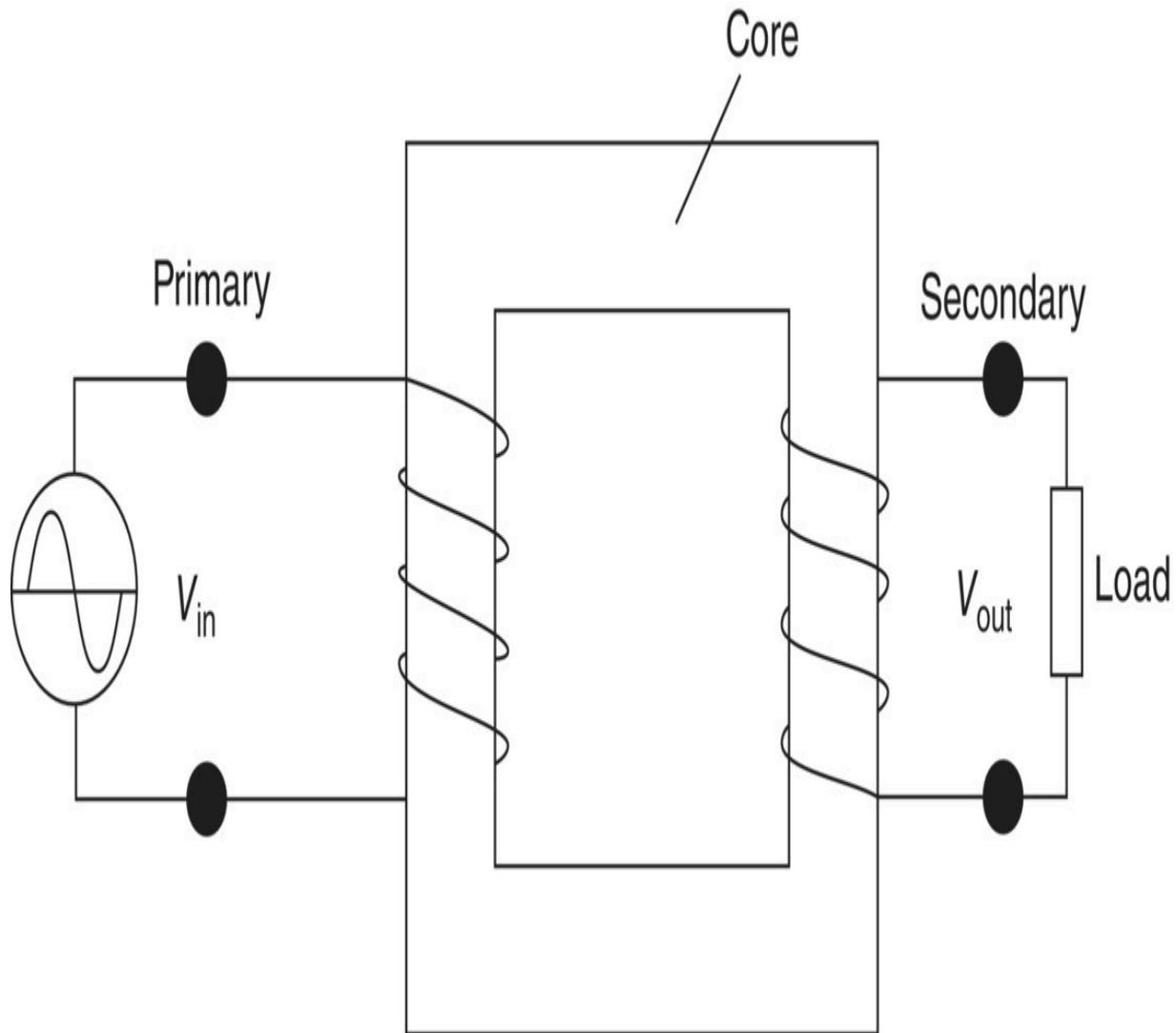

[Figure 6.9 A transformer consists of two coils sharing the same magnetic cor...](#)

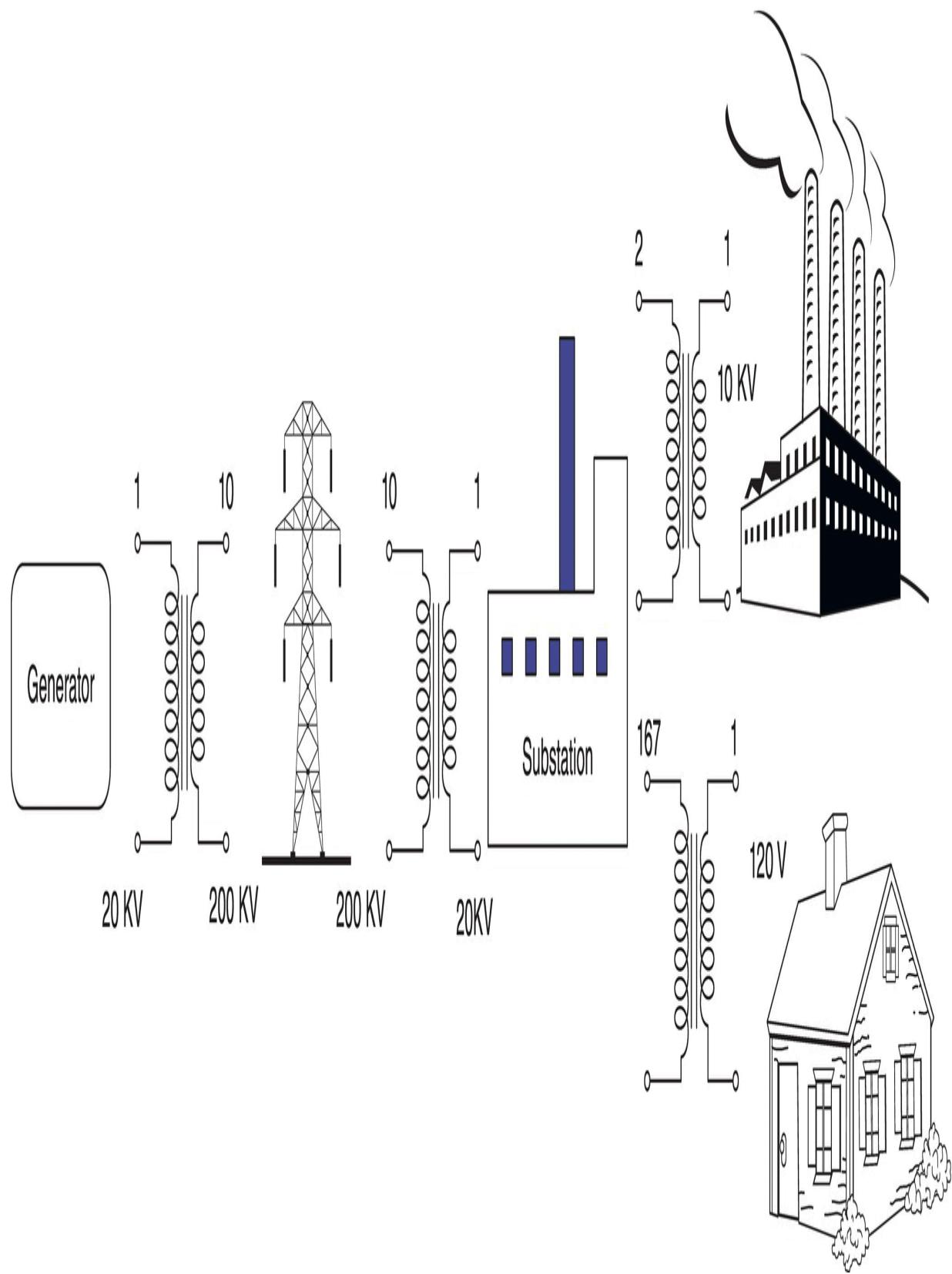

[Figure 6.10 Using transformers in an electrical distribution system we can e...](#)

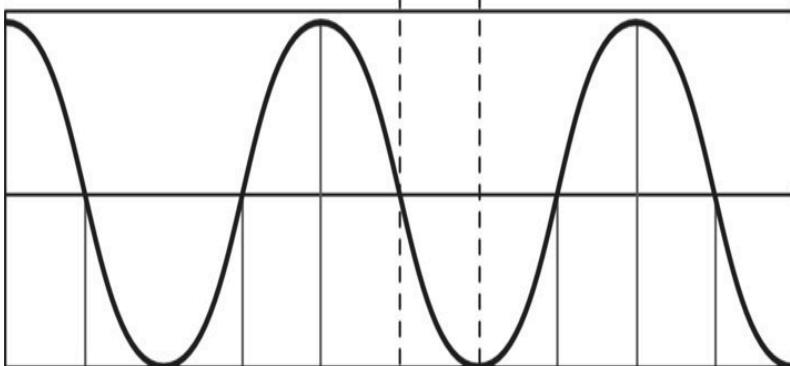

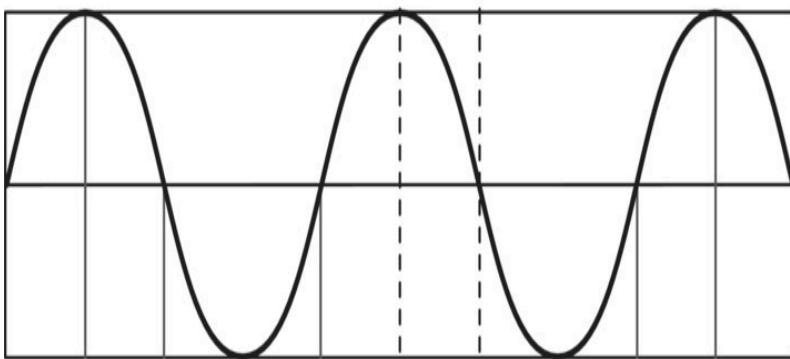

[Figure 6.11 The sinusoidal current through a resistor is in phase with the v...](#)

## Chapter 7

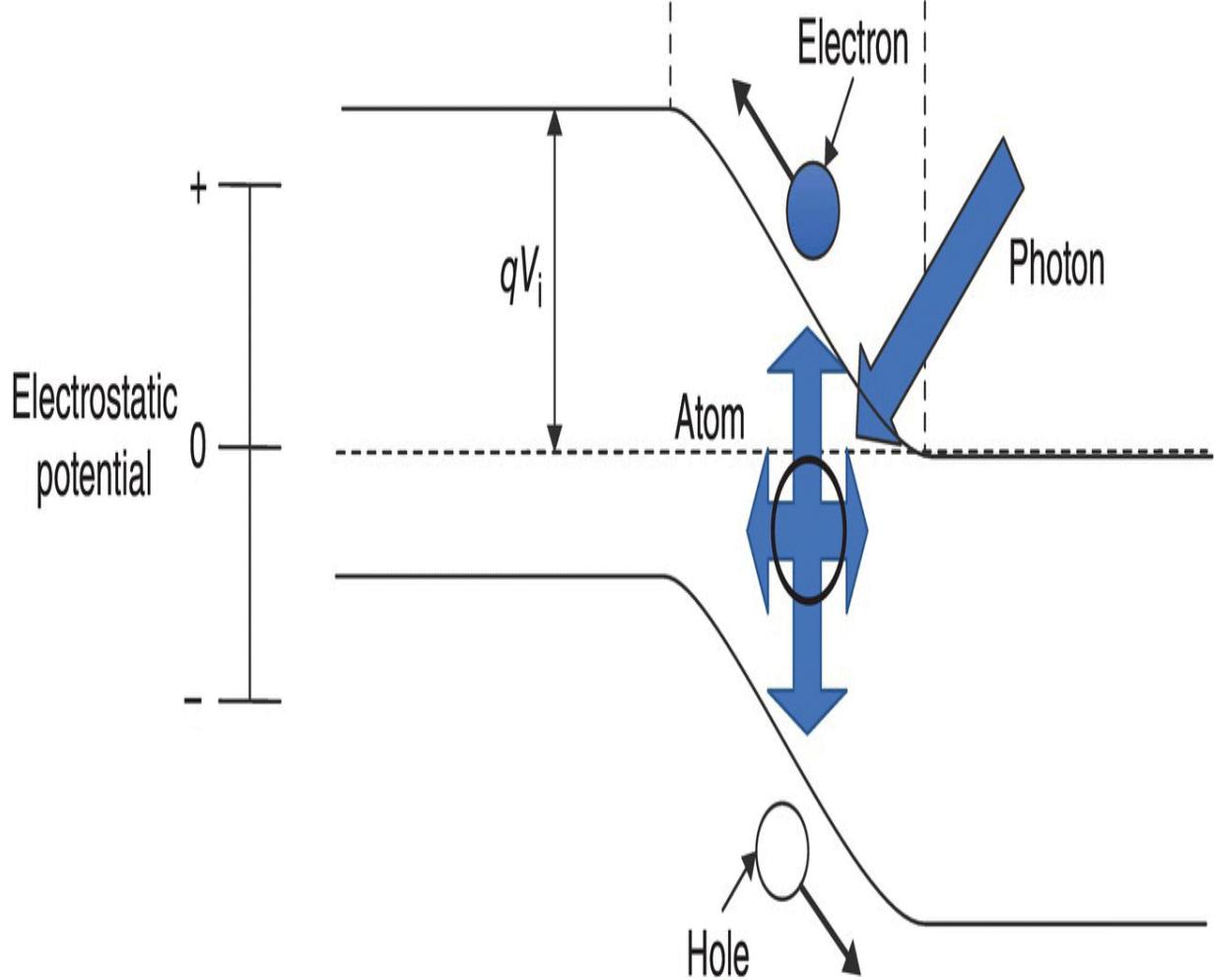

[Figure 7.1 When a photon strikes the transition region of a solar cell the e...](#)

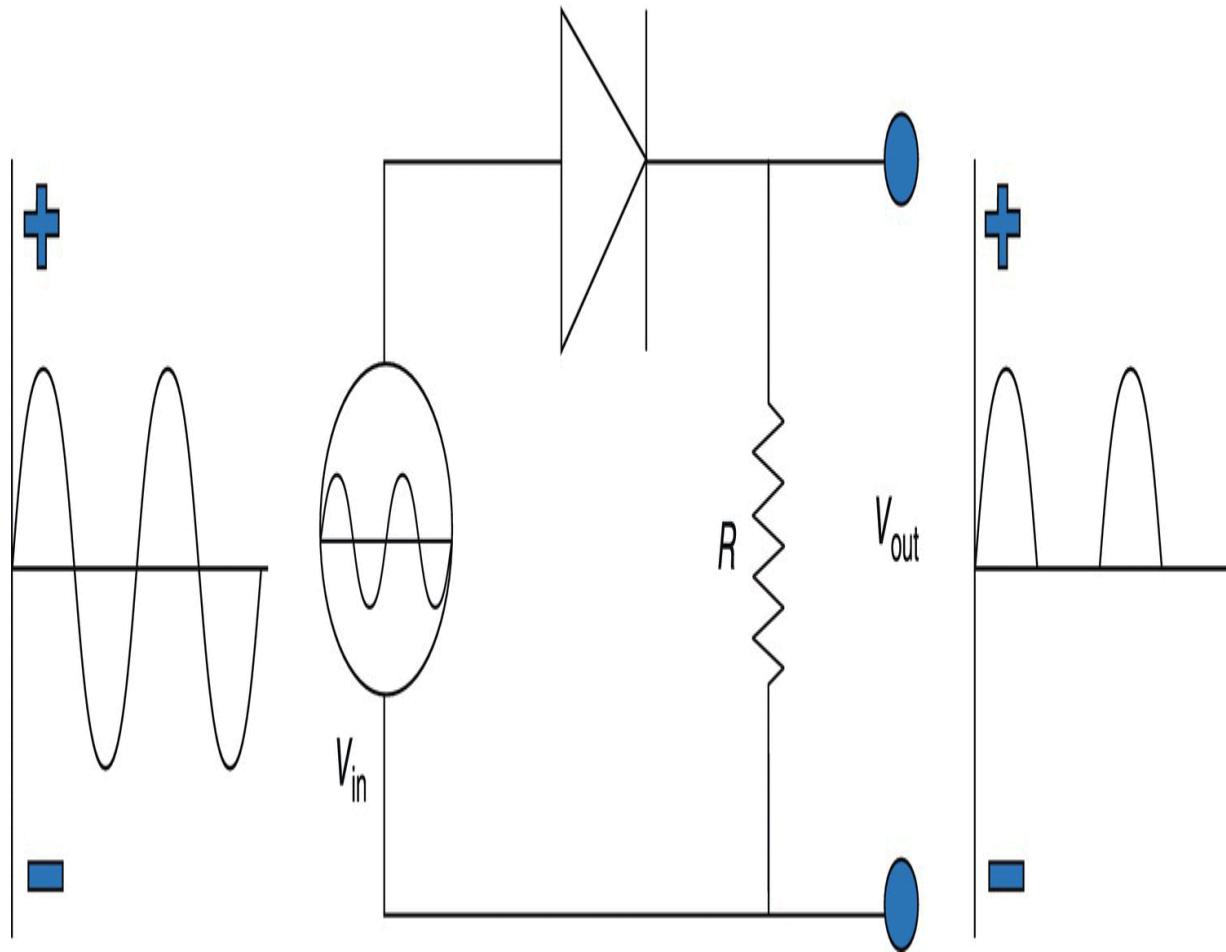

[Figure 7.2 A rectifier circuit only lets the positive swing of the current p...](#)

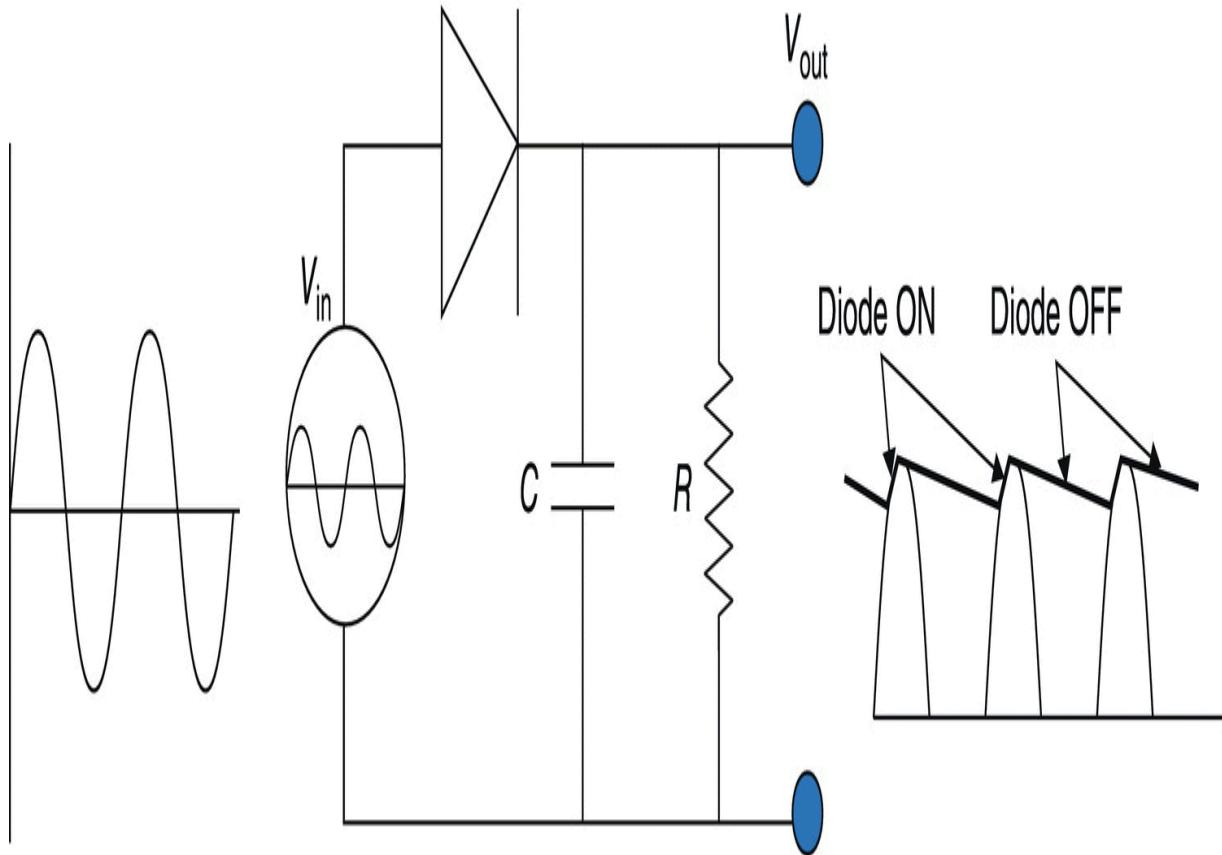

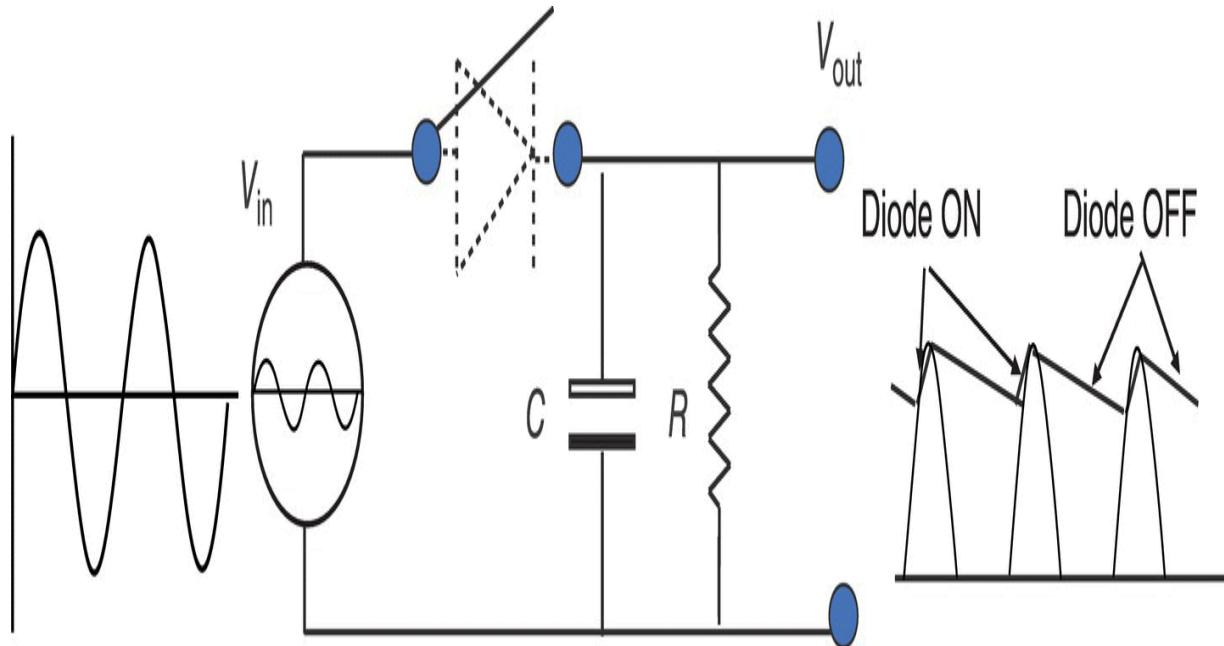

[Figure 7.3 A capacitor in parallel with a resistor stores charges during the...](#)

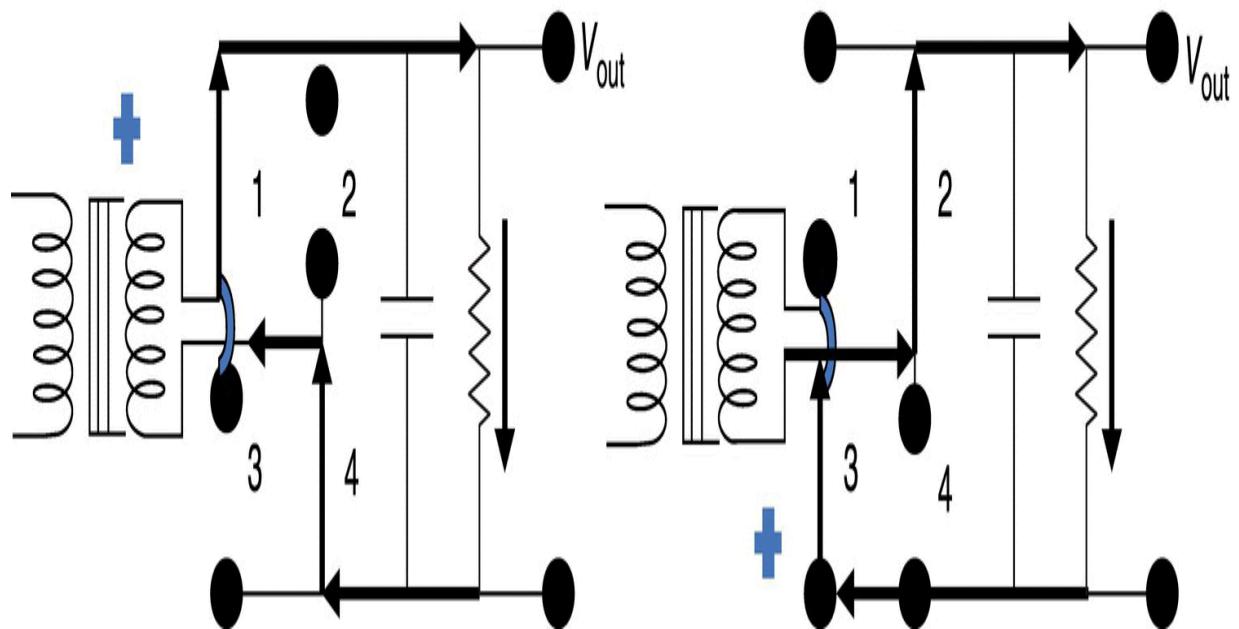

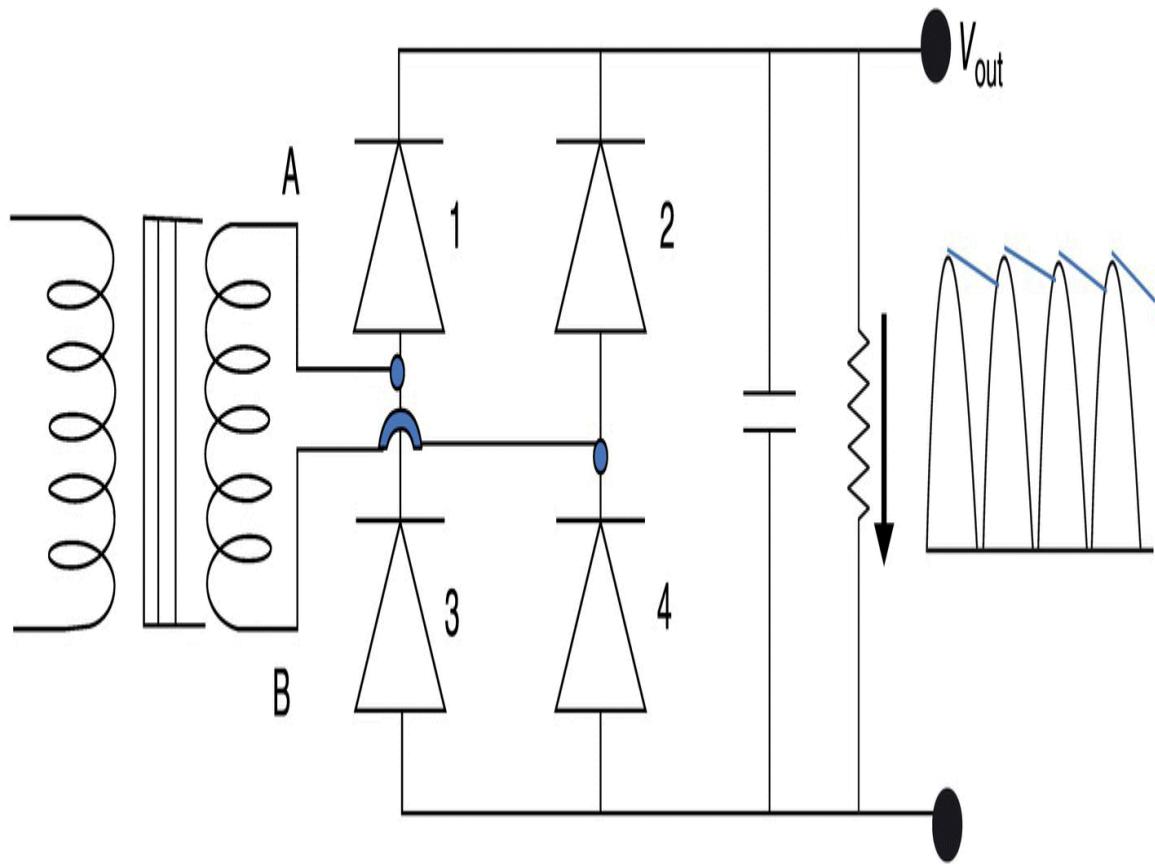

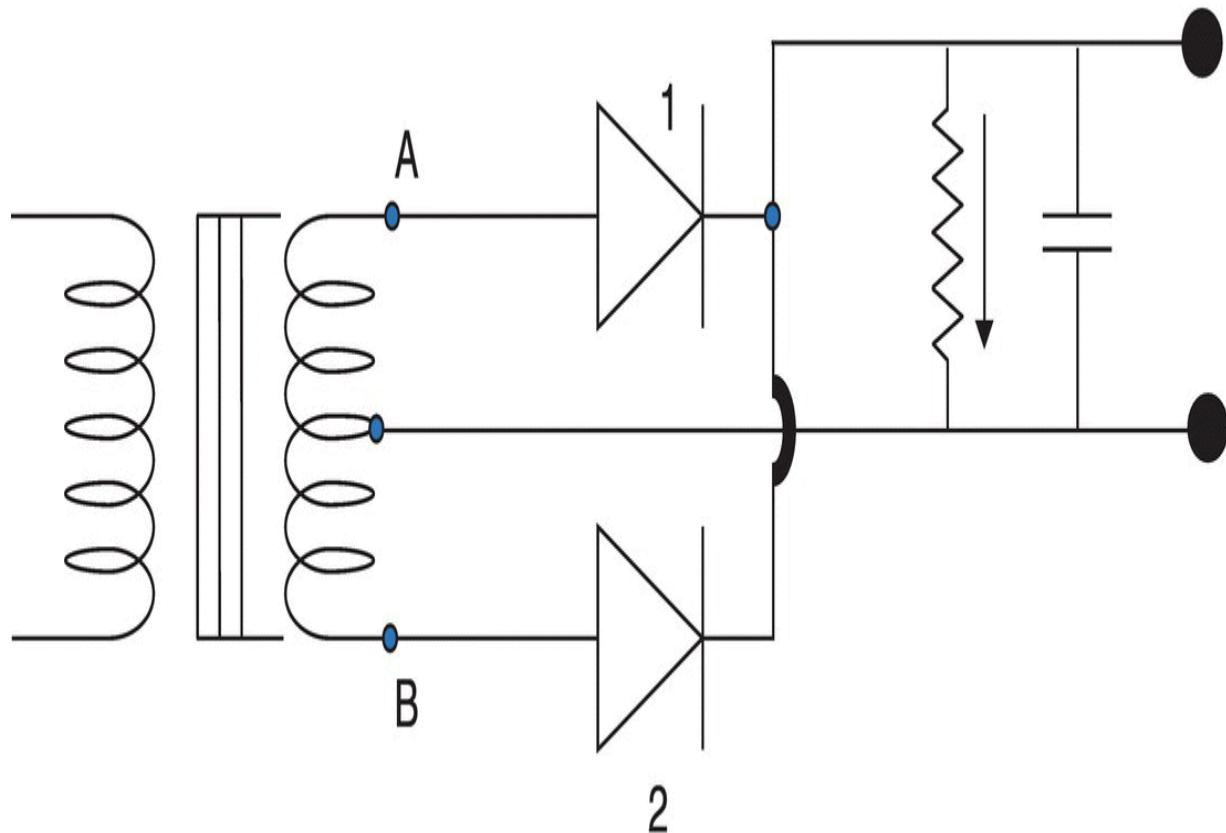

[Figure 7.4 A full-wave rectifier with a smoothing capacitor uses both positive and negative half-cycles to produce a DC output.](#)

[Figure 7.5 Full-wave rectification using the middle tap of a three-winding transformer.](#)

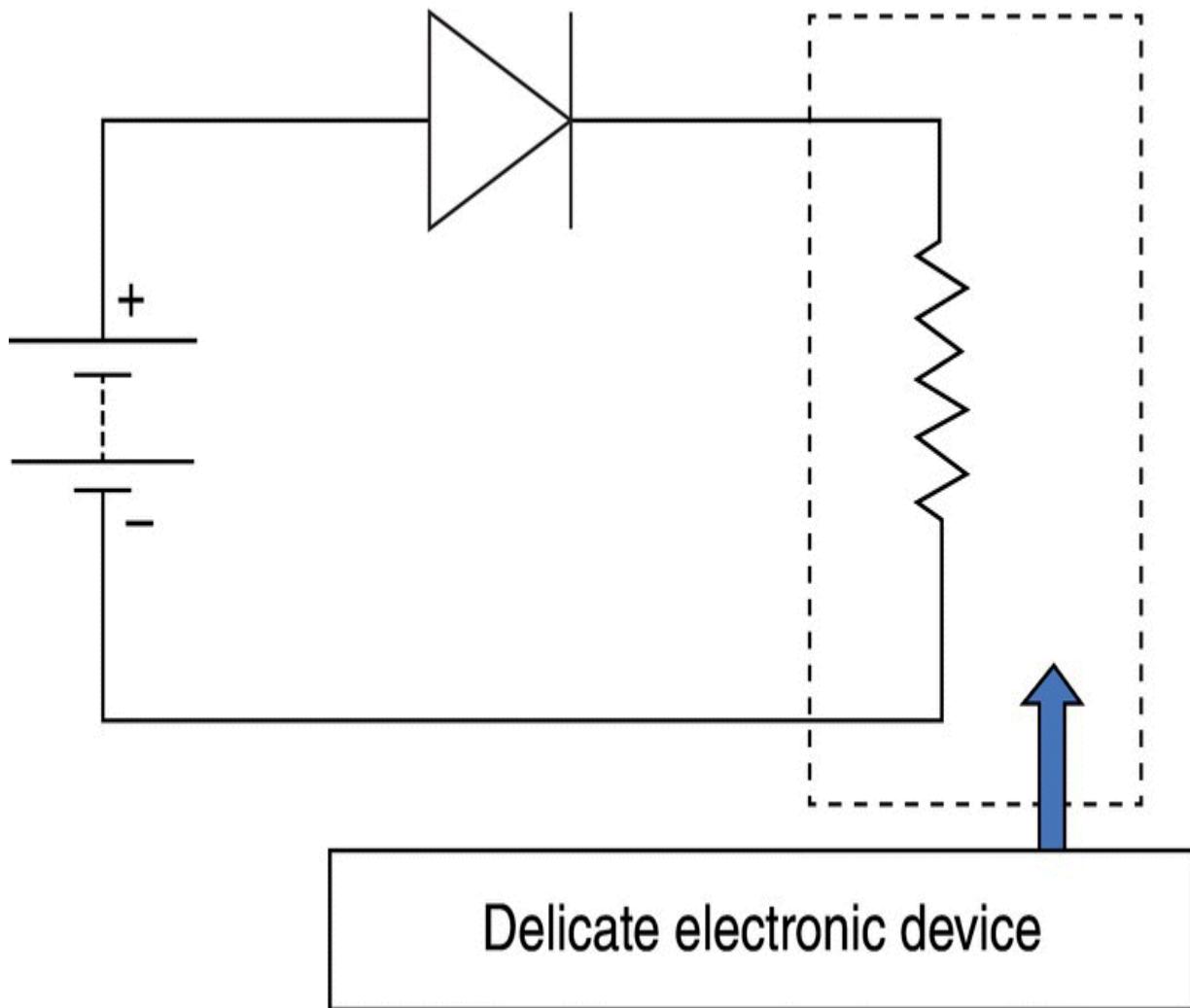

[Figure 7.6 A reverse current protection circuit prevents damage to the delicate diodes in a rectifier.](#)

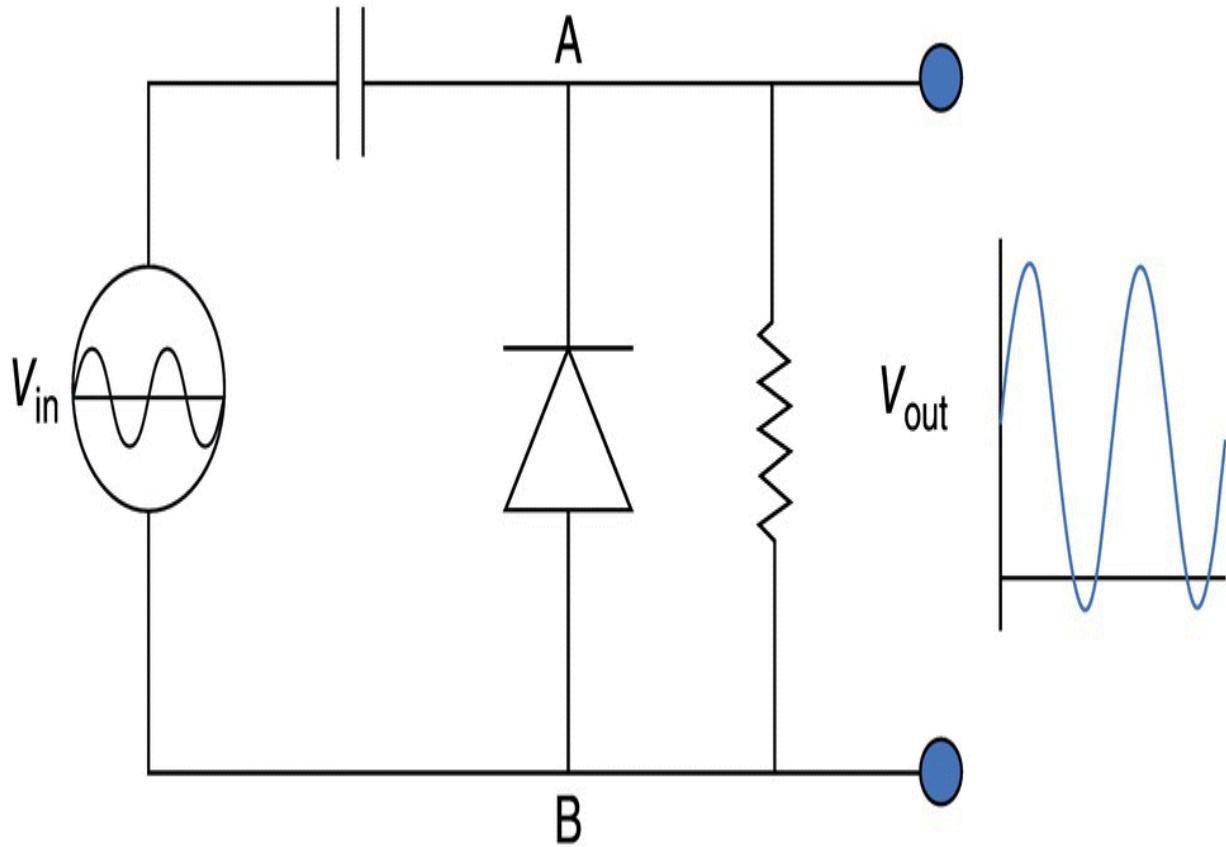

[Figure 7.7 A clamping circuit shifts the sinusoidal wave so that the entire waveform is above the zero line.](#)

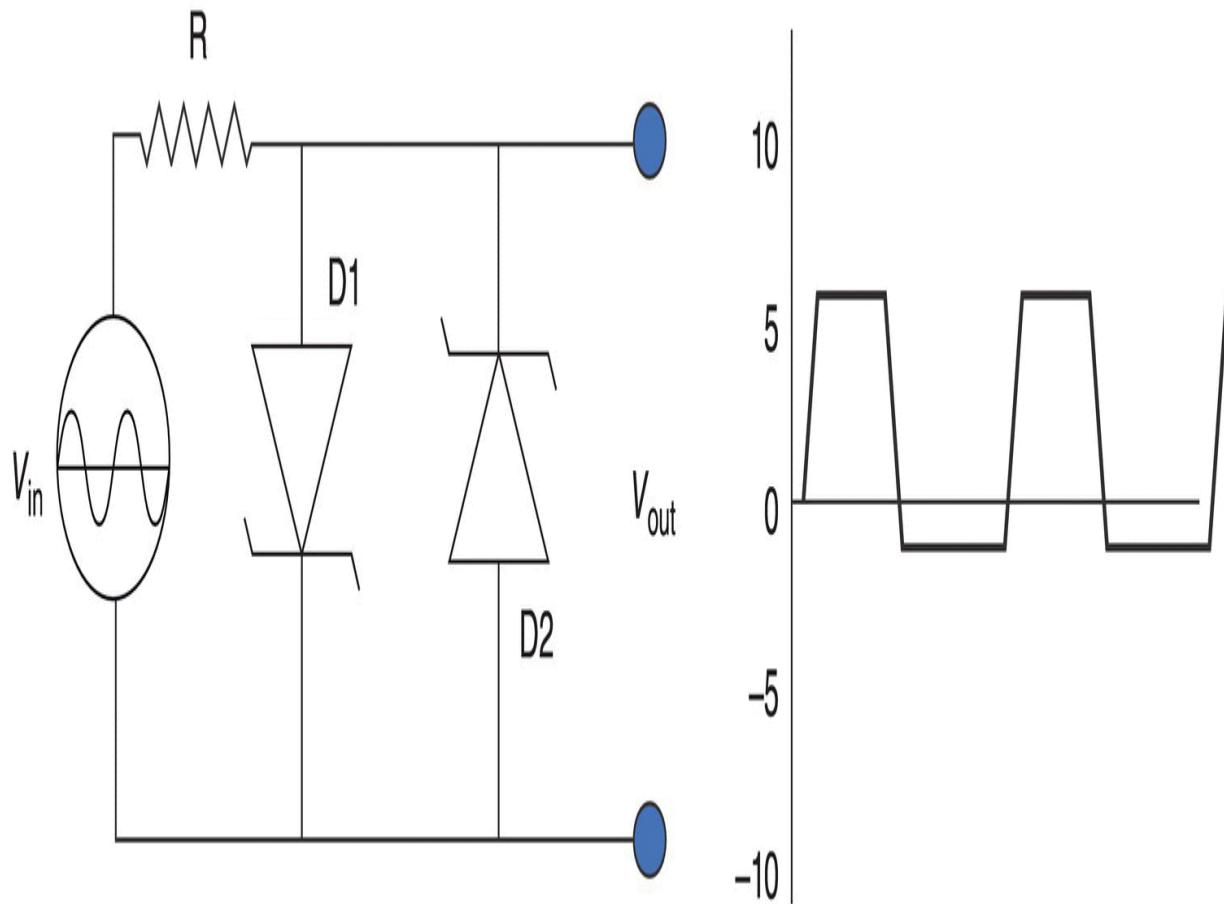

[Figure 7.8 A voltage clipper prevents the output voltage going over a specific maximum value.](#)

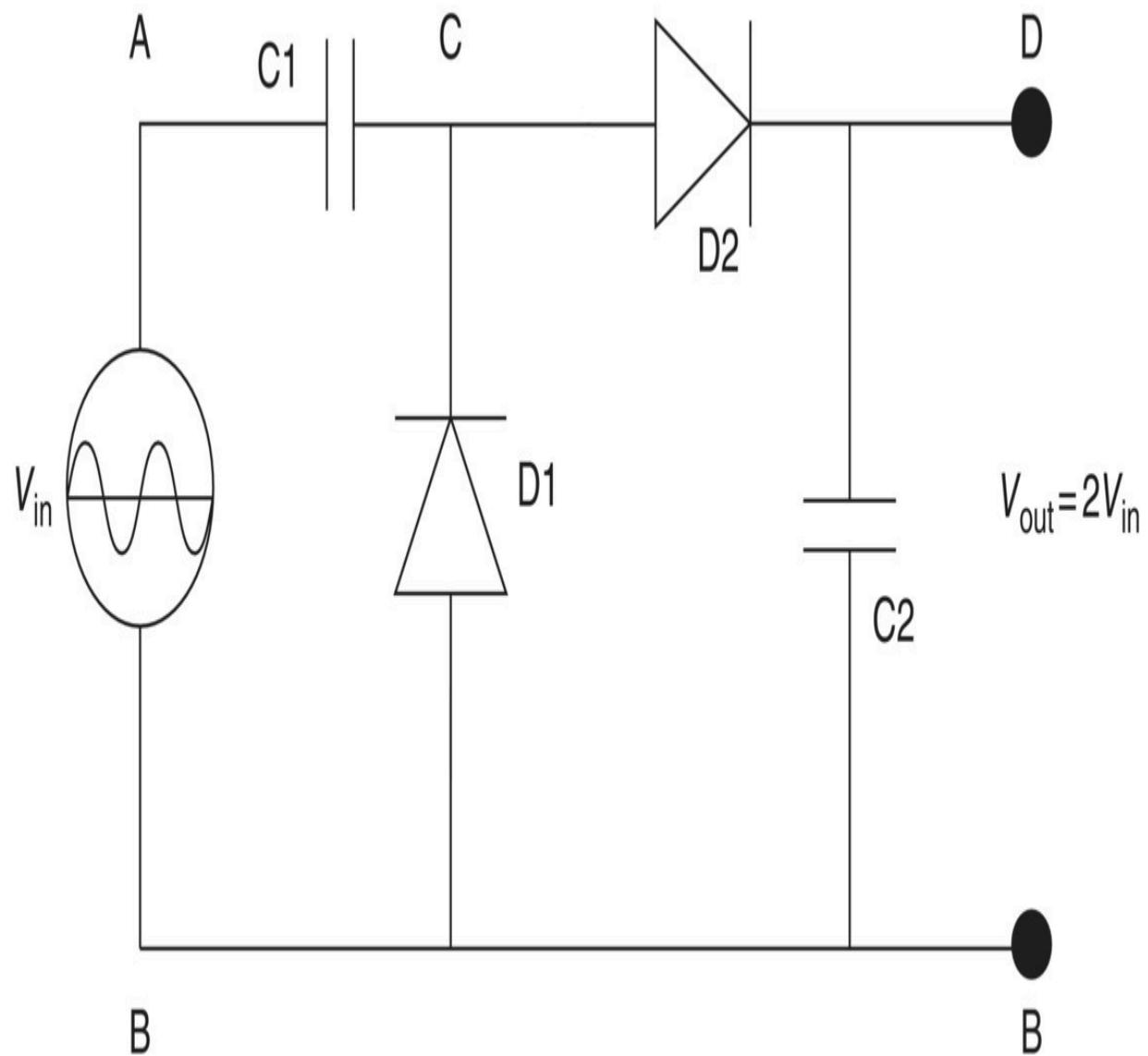

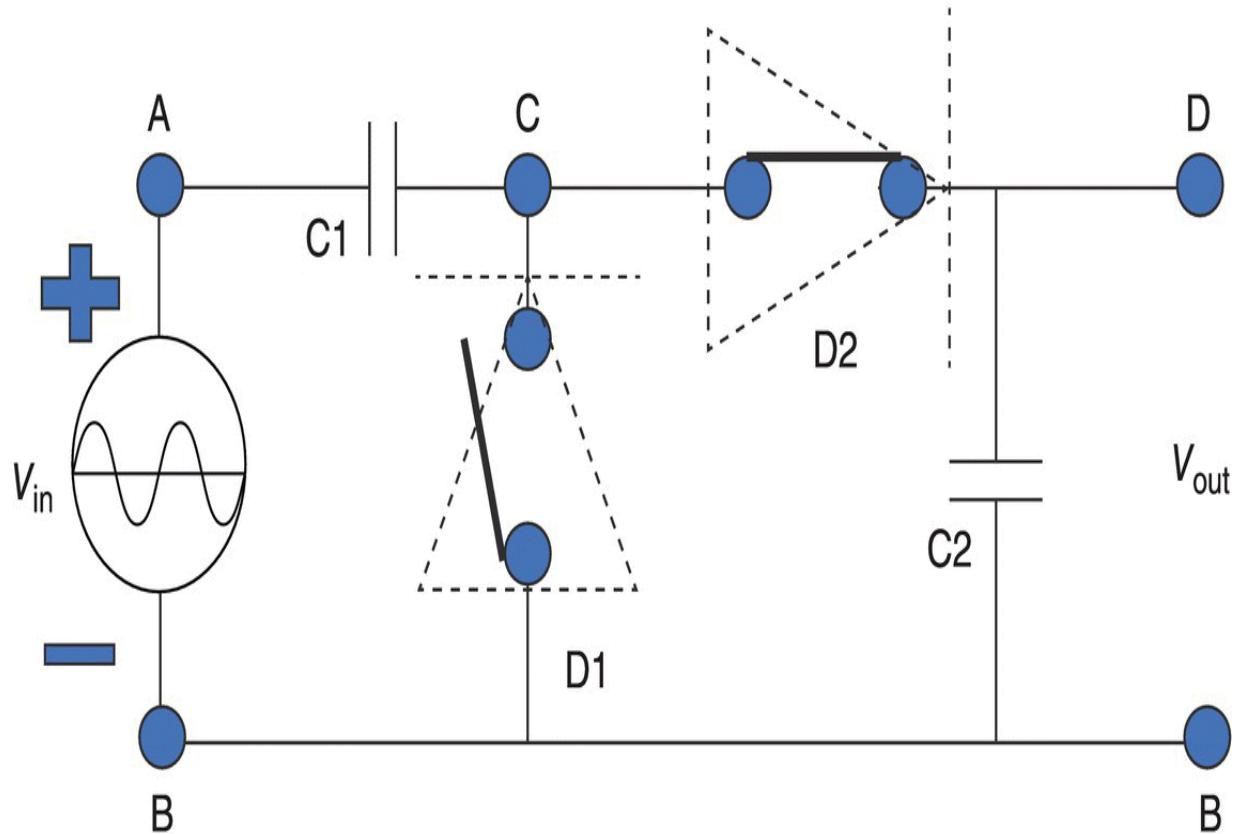

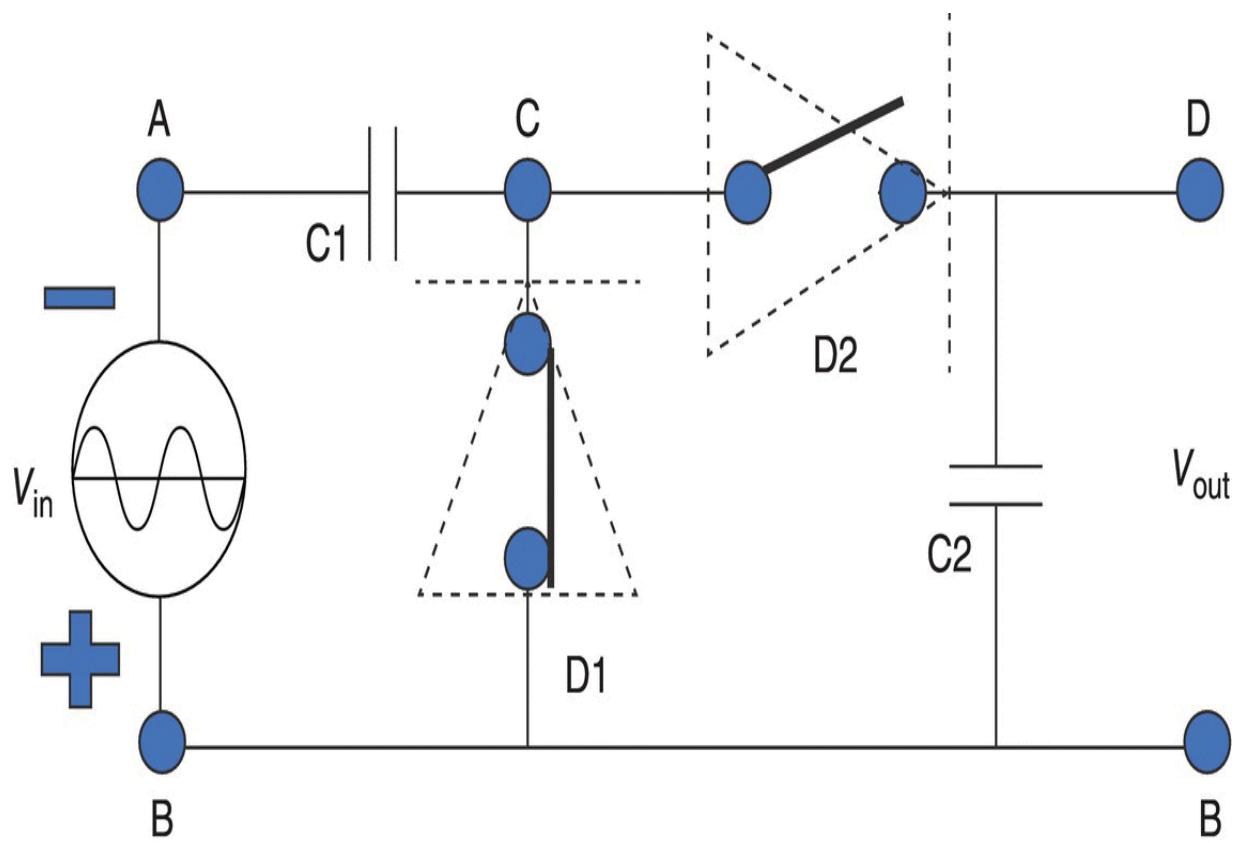

[Figure 7.9 A half-wave voltage doubler circuit results in an output voltage that is twice the input voltage.](#)

[Figure 7.10 A simplified equivalent circuit for a voltage doubler.](#)

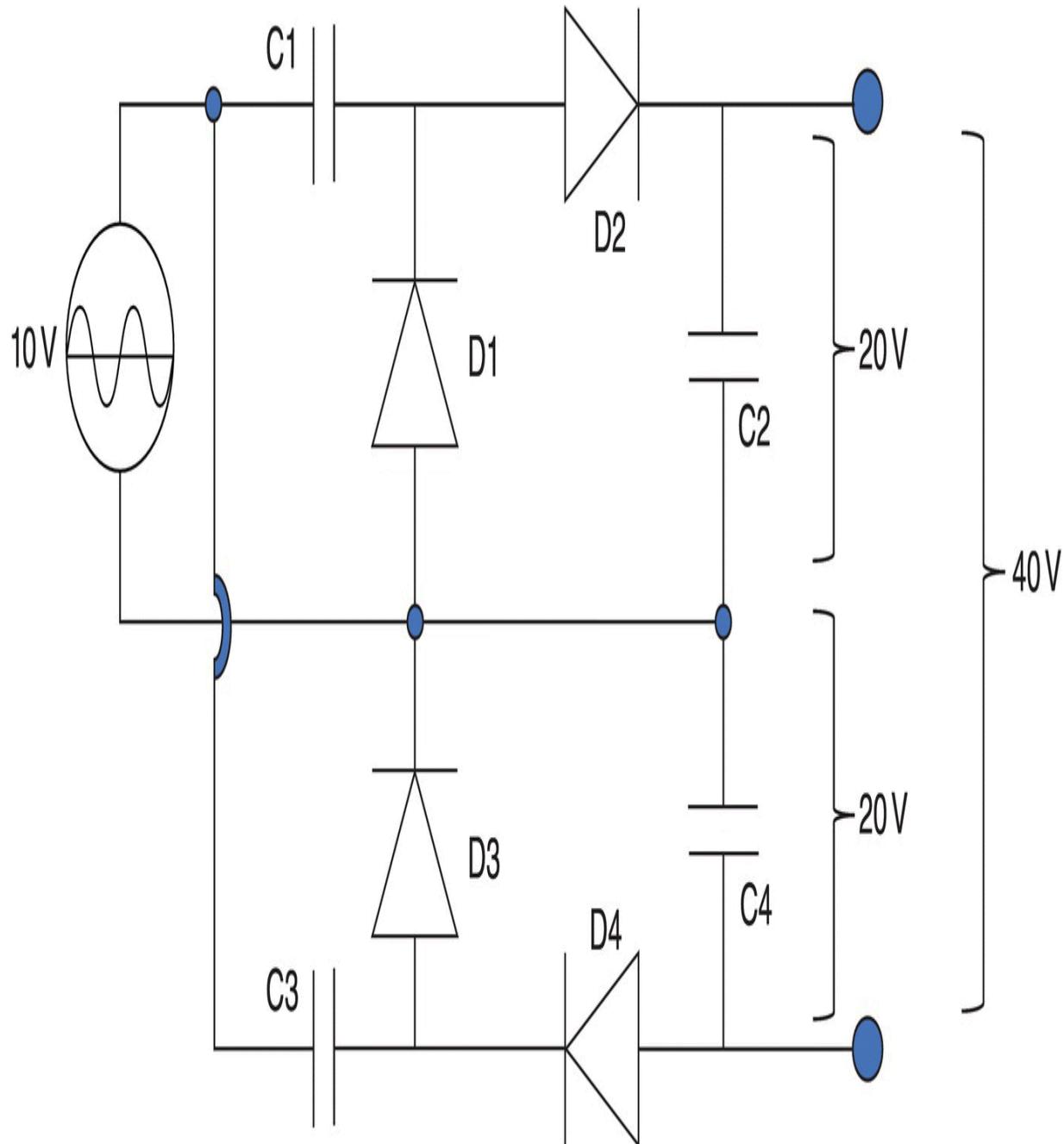

[Figure 7.11 A circuit that makes the output voltage four times as high as the input voltage.](#)

[Figure 7.12 Diodes are used to bypass damaged solar cell panels.](#)

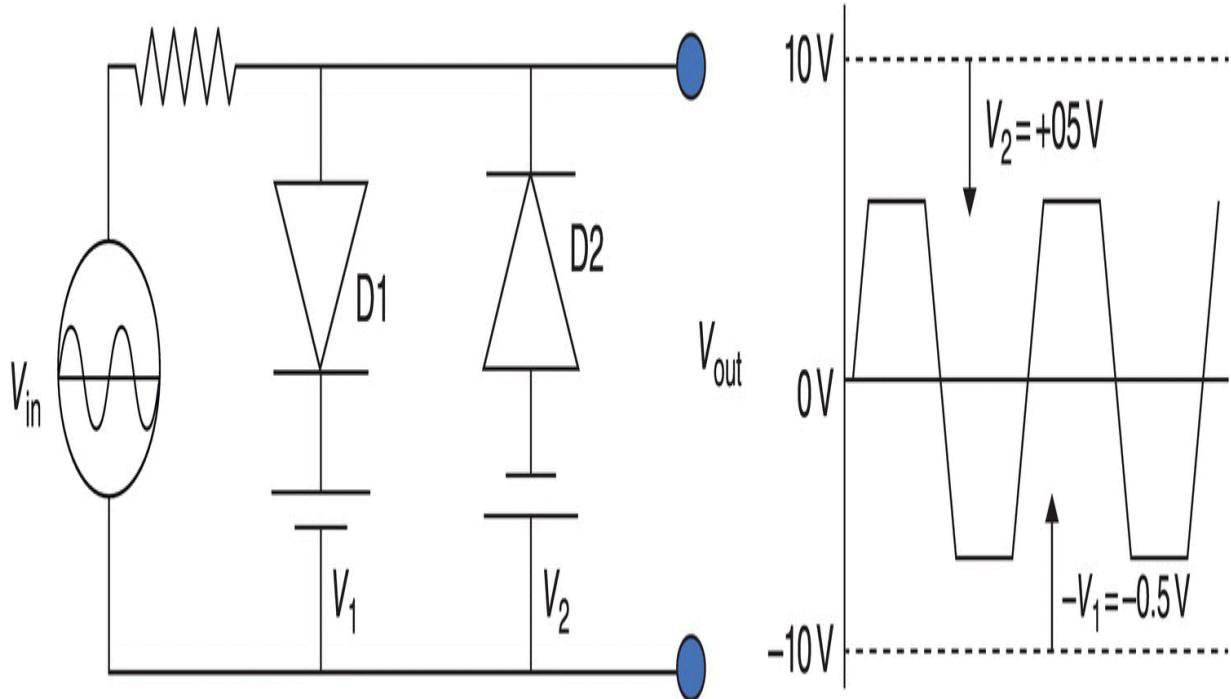

[Figure 7.13 A voltage clipper using Zener diodes can clip the voltage depending on the input voltage.](#)

[Figure 7.14 An equivalent diode rectifier circuit when the diode is reversed.](#)

## Chapter 8

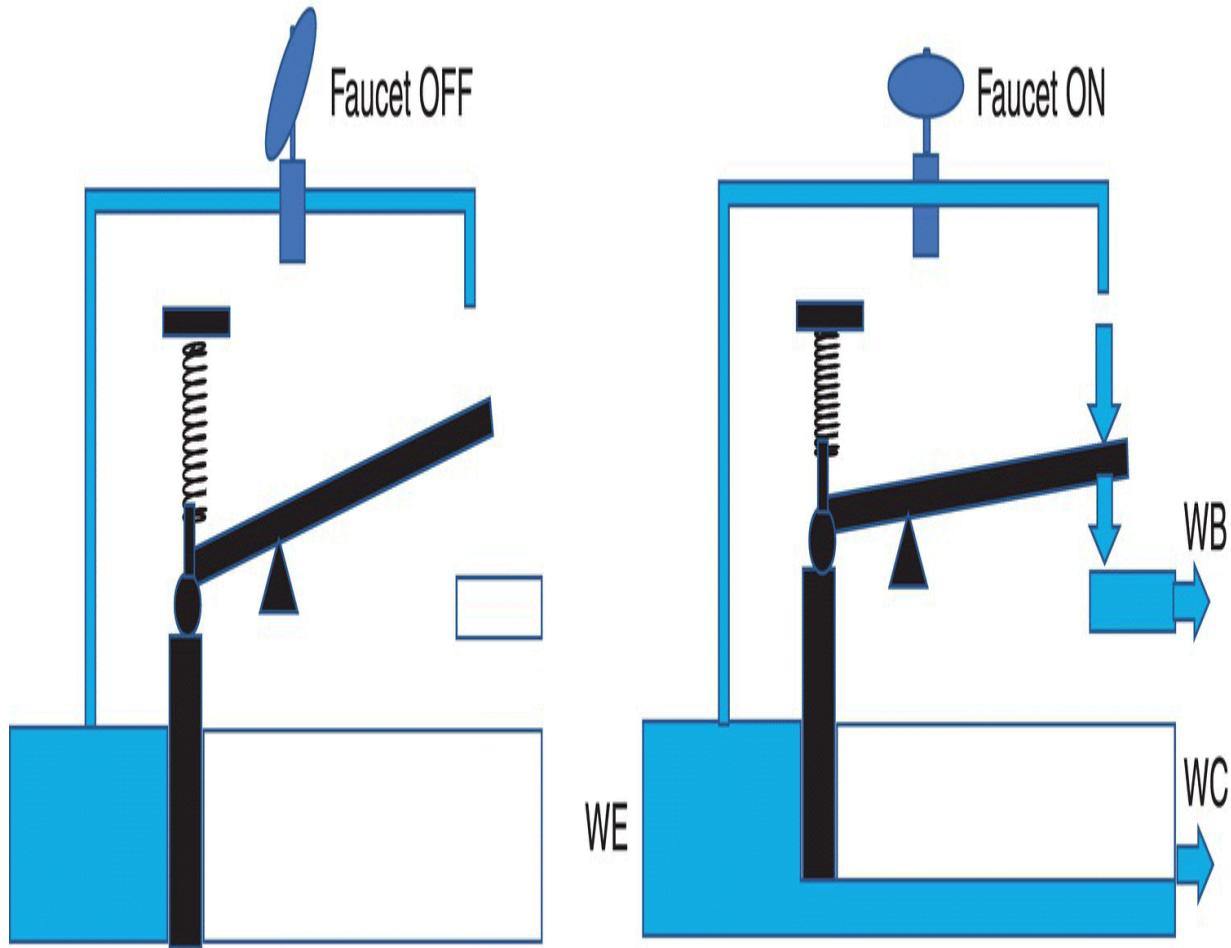

[Figure 8.1 A small water flow on the upper pipe controls a much larger flow through a nozzle.](#)

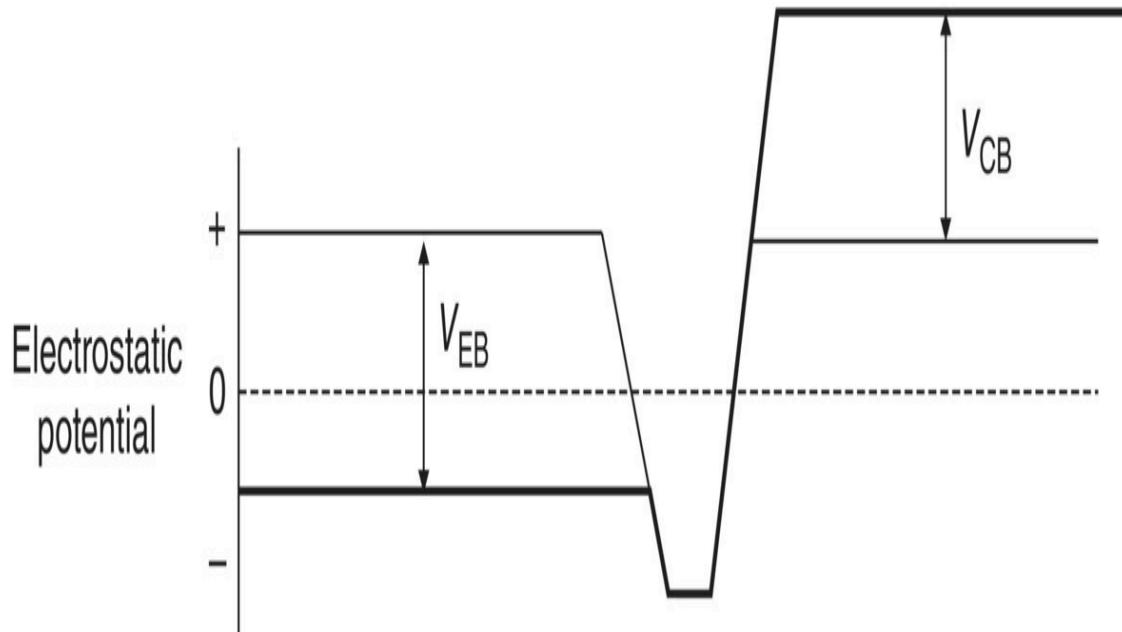

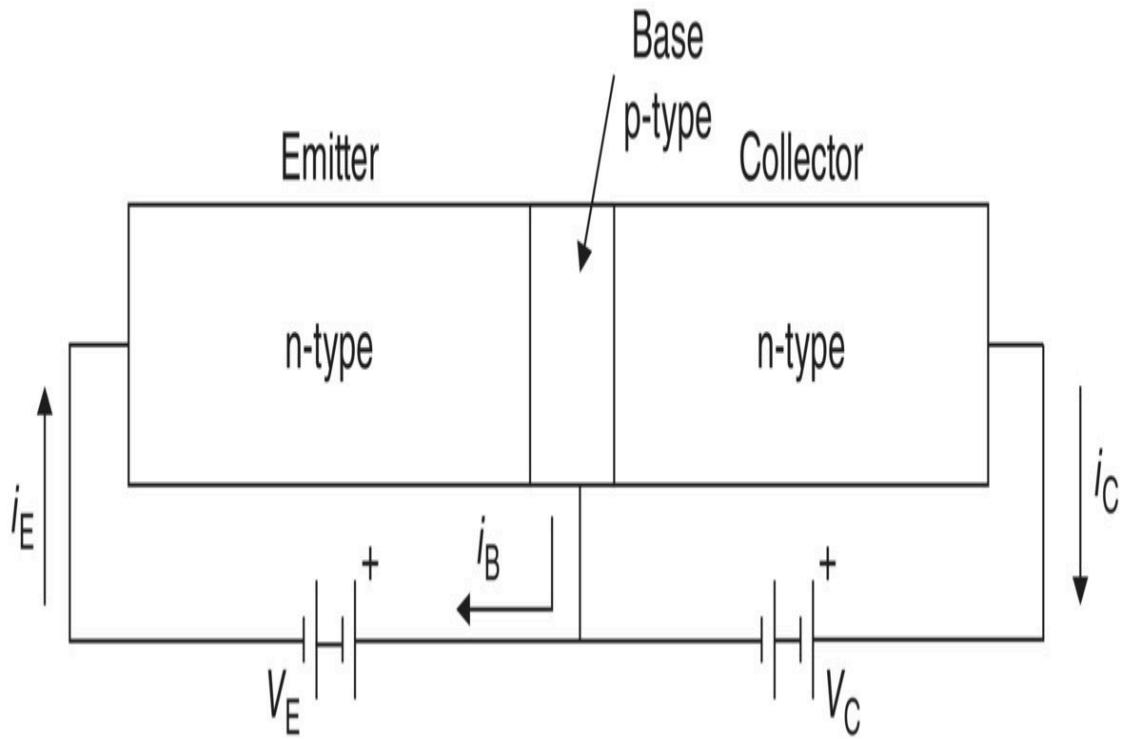

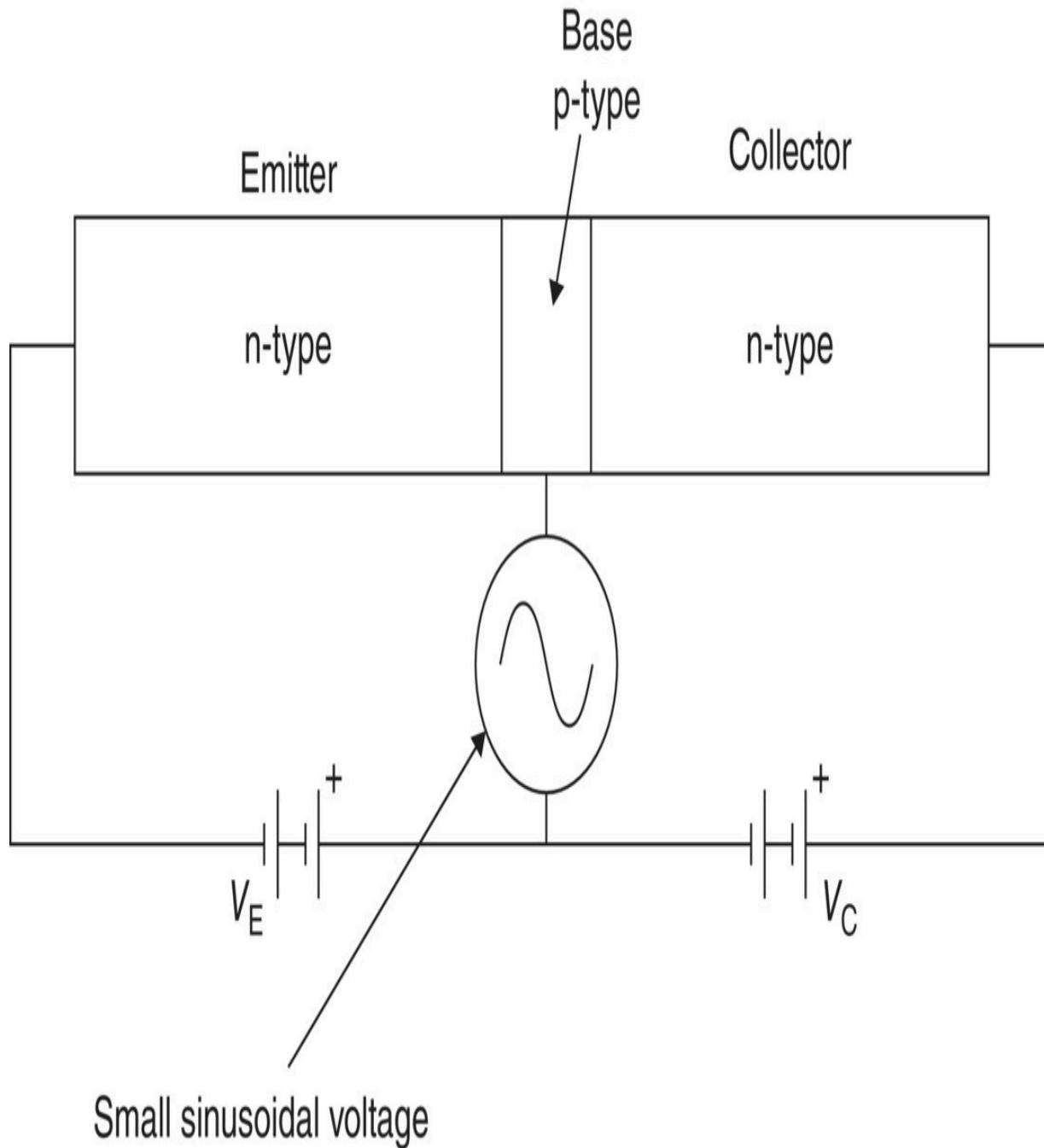

[Figure 8.2 The structure of an npn-transistor consists of a narrow p-type section between two n-type sections.](#)

[Figure 8.3 When we apply external voltages to an npn-transistor the internal electric fields are reversed.](#)

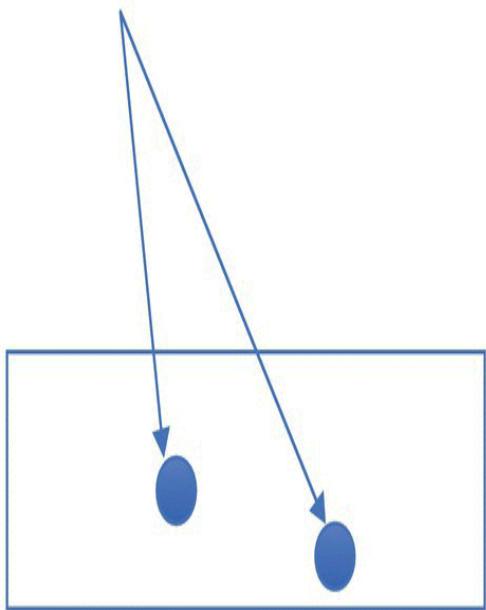

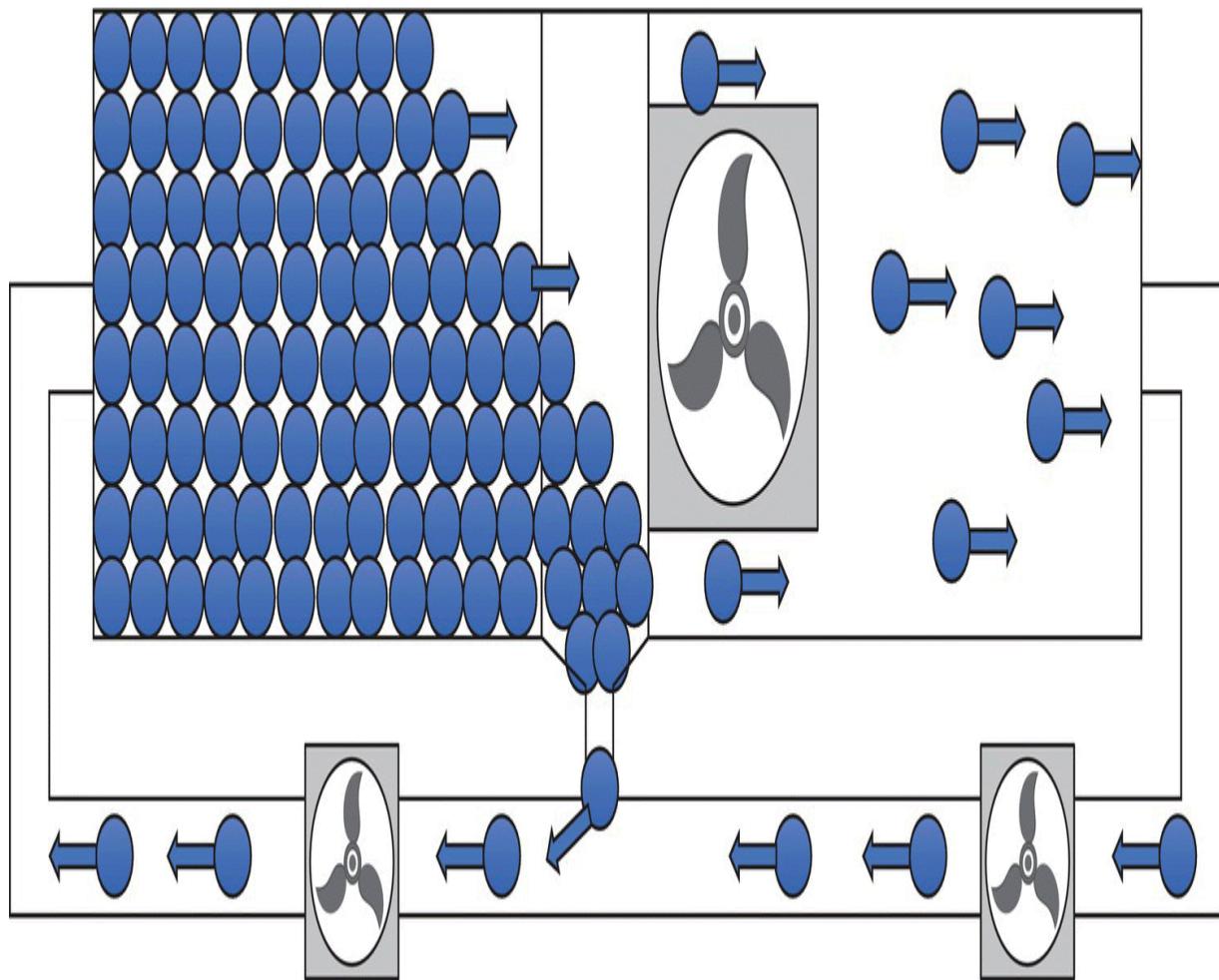

[Figure 8.4 Some balls fall from a box full of ping-pong balls \(electrons\) onto a metal plate.](#)

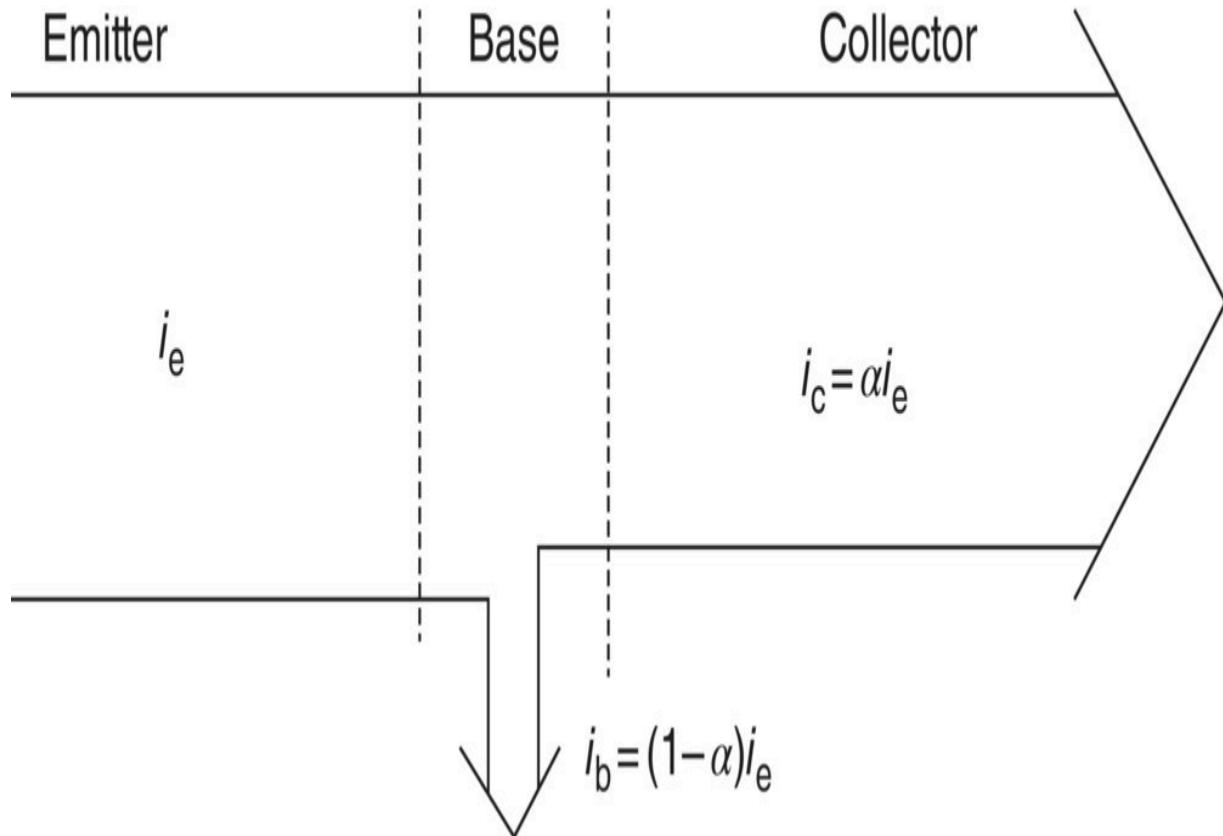

Figure 8.5 The collector current,  $I_C$ , is proportional to the emitter current,...

Figure 8.6 Adding a sinusoidal signal to the base of a transistor properly b...

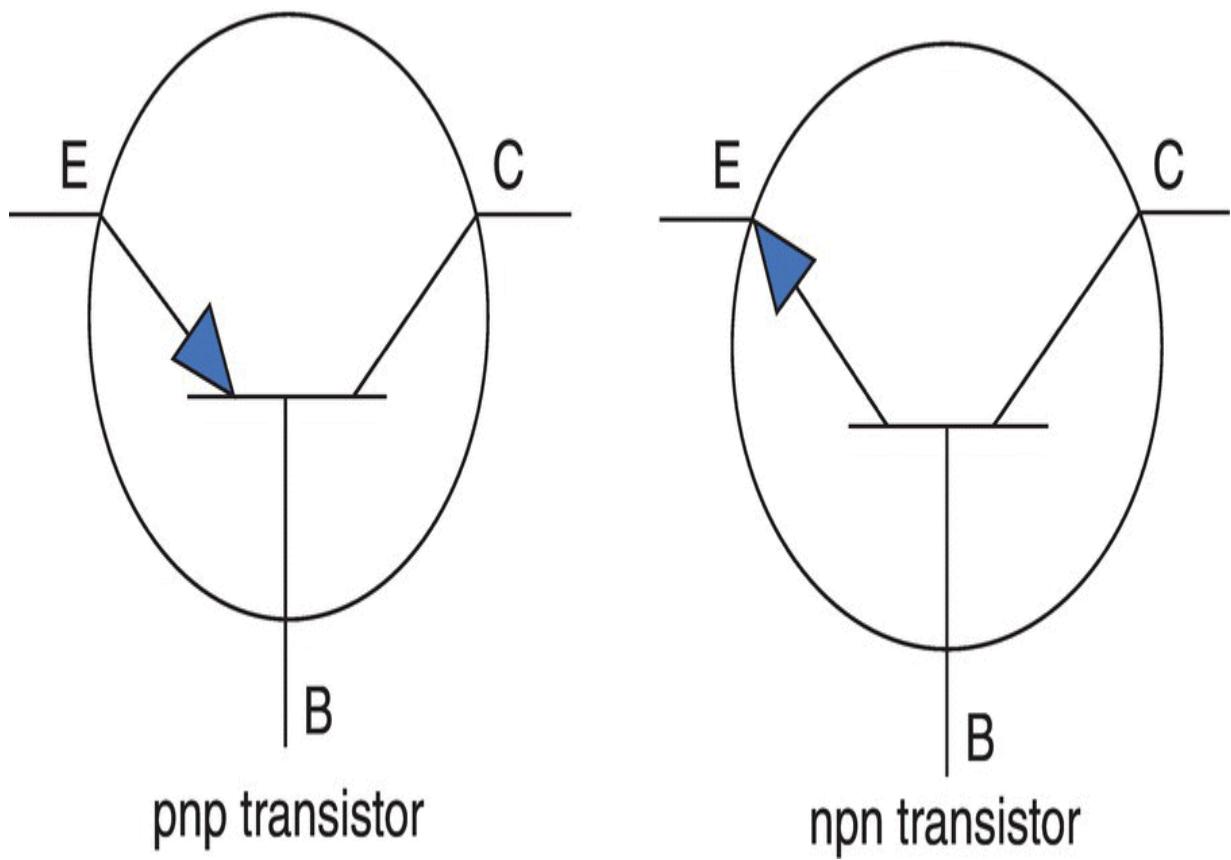

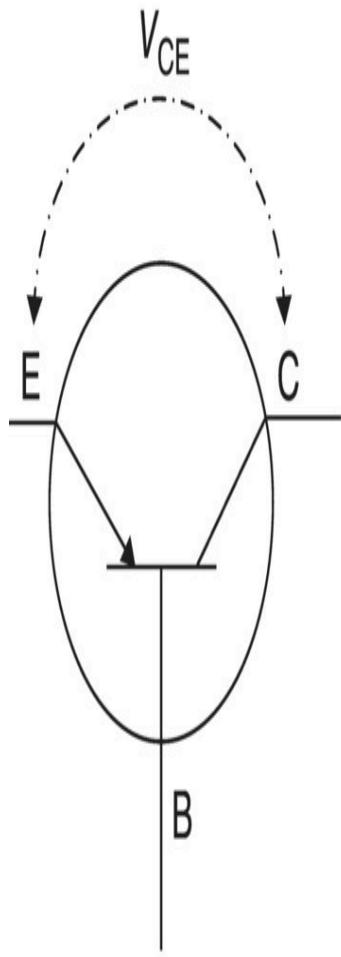

Figure 8.7 Symbols for pnp- and npn-transistors. The arrows show the directi...

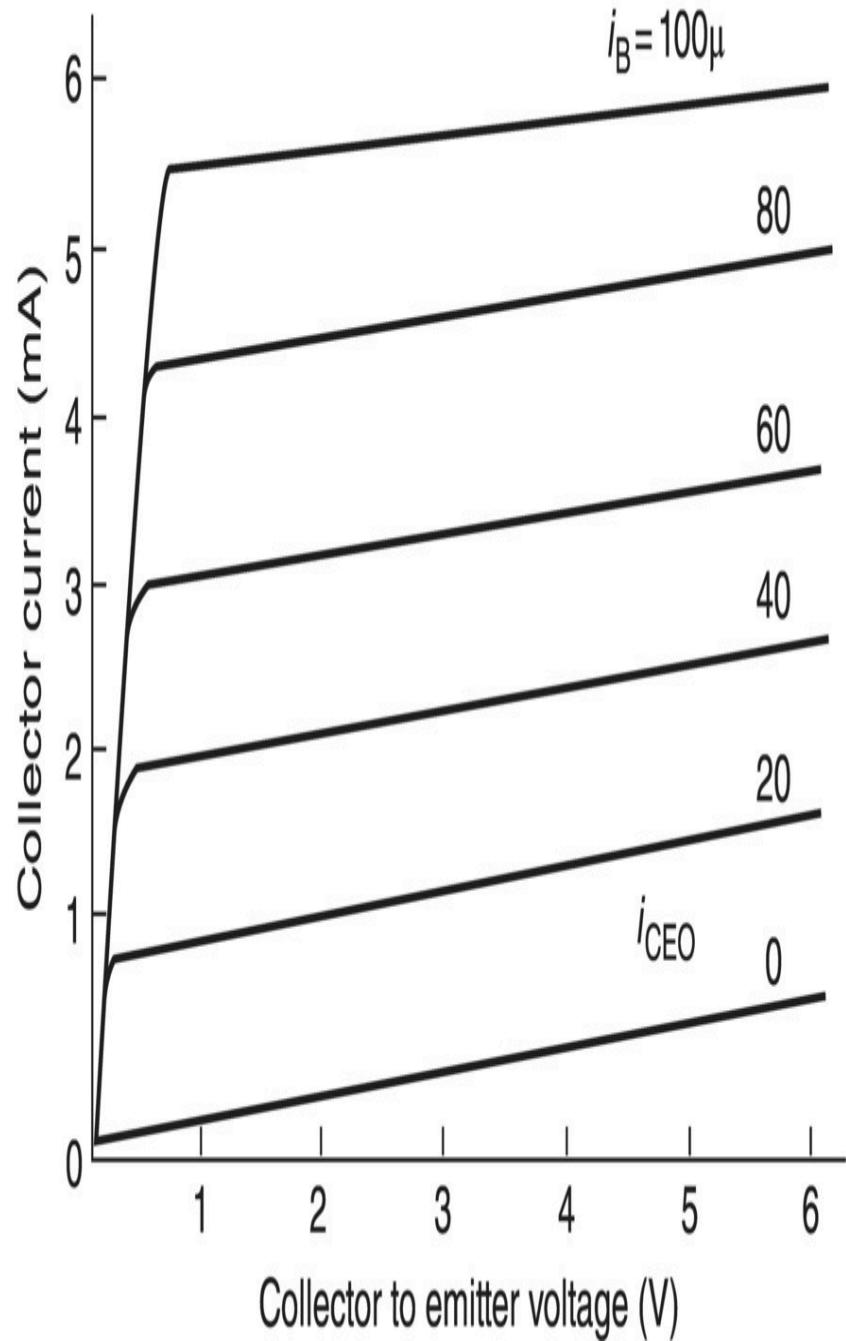

Figure 8.8 Transistor performance is graphically given by the collector curr...

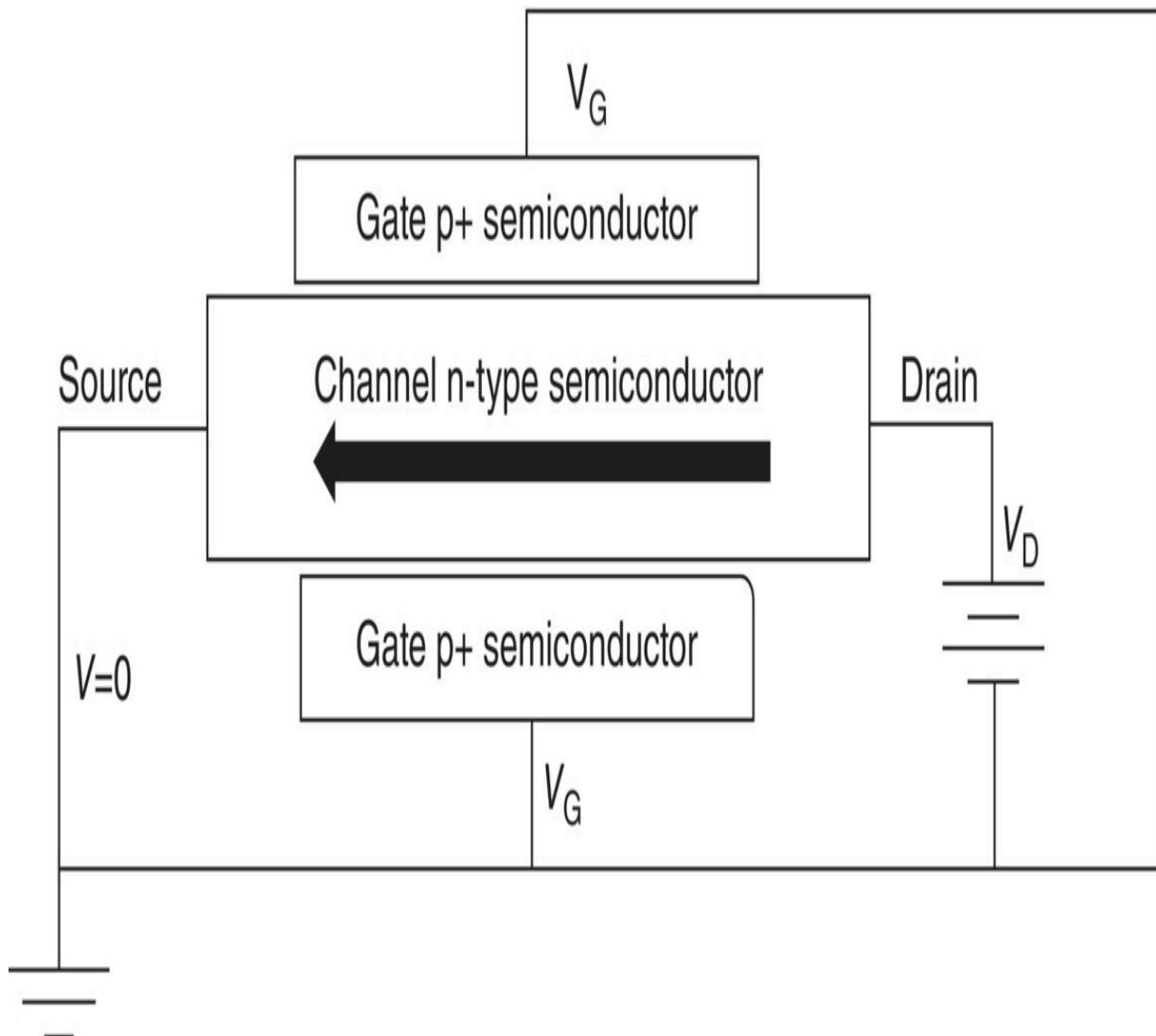

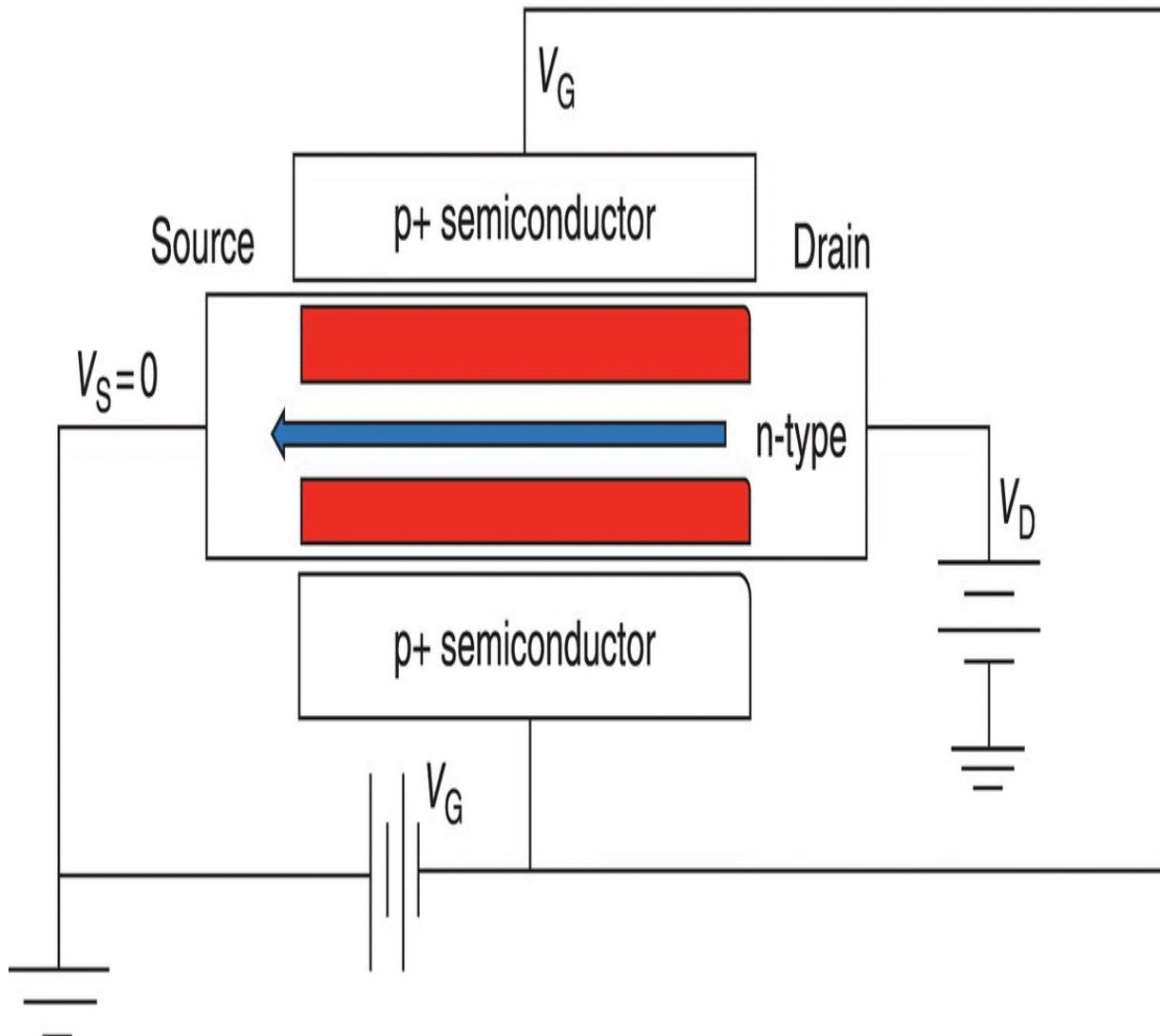

Figure 8.9 The structure of an n-type JFET consists of one type of semicondu...

Figure 8.10 A JFET with a positive voltage at the gates creates two depletio...

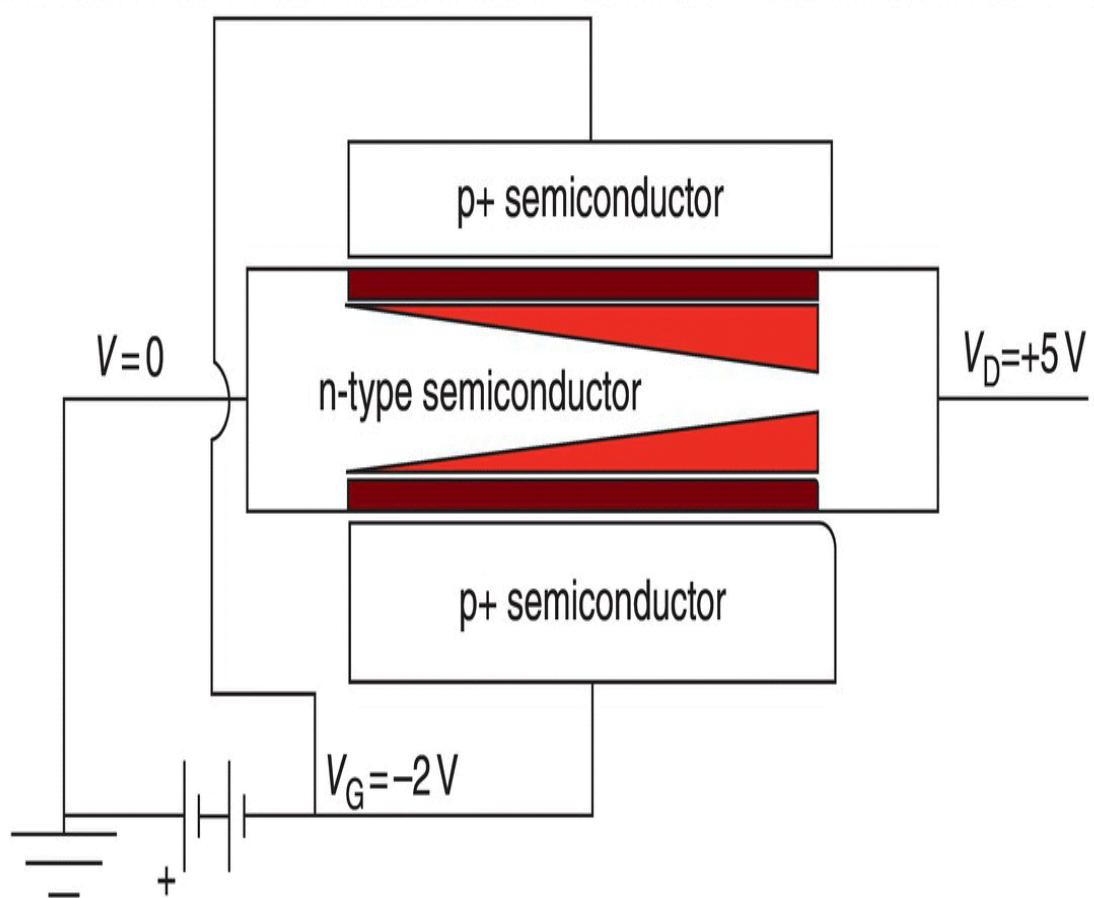

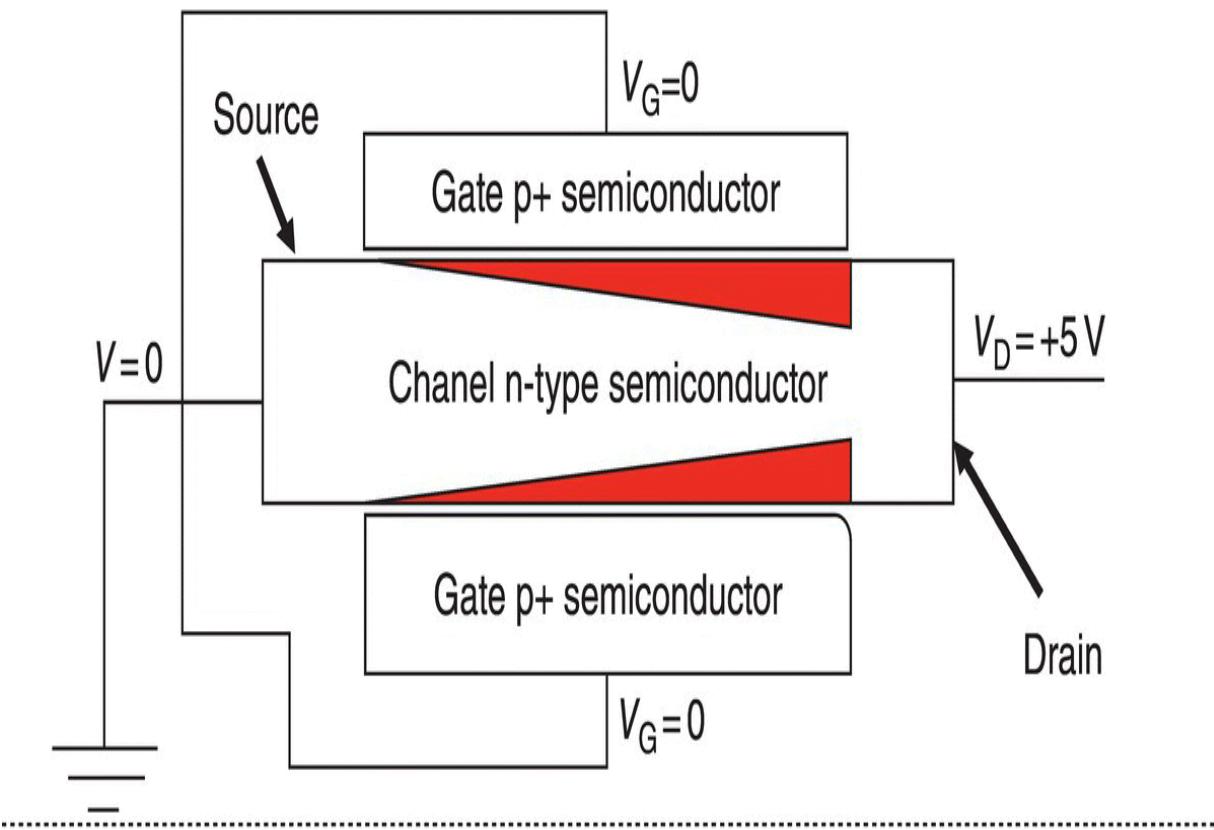

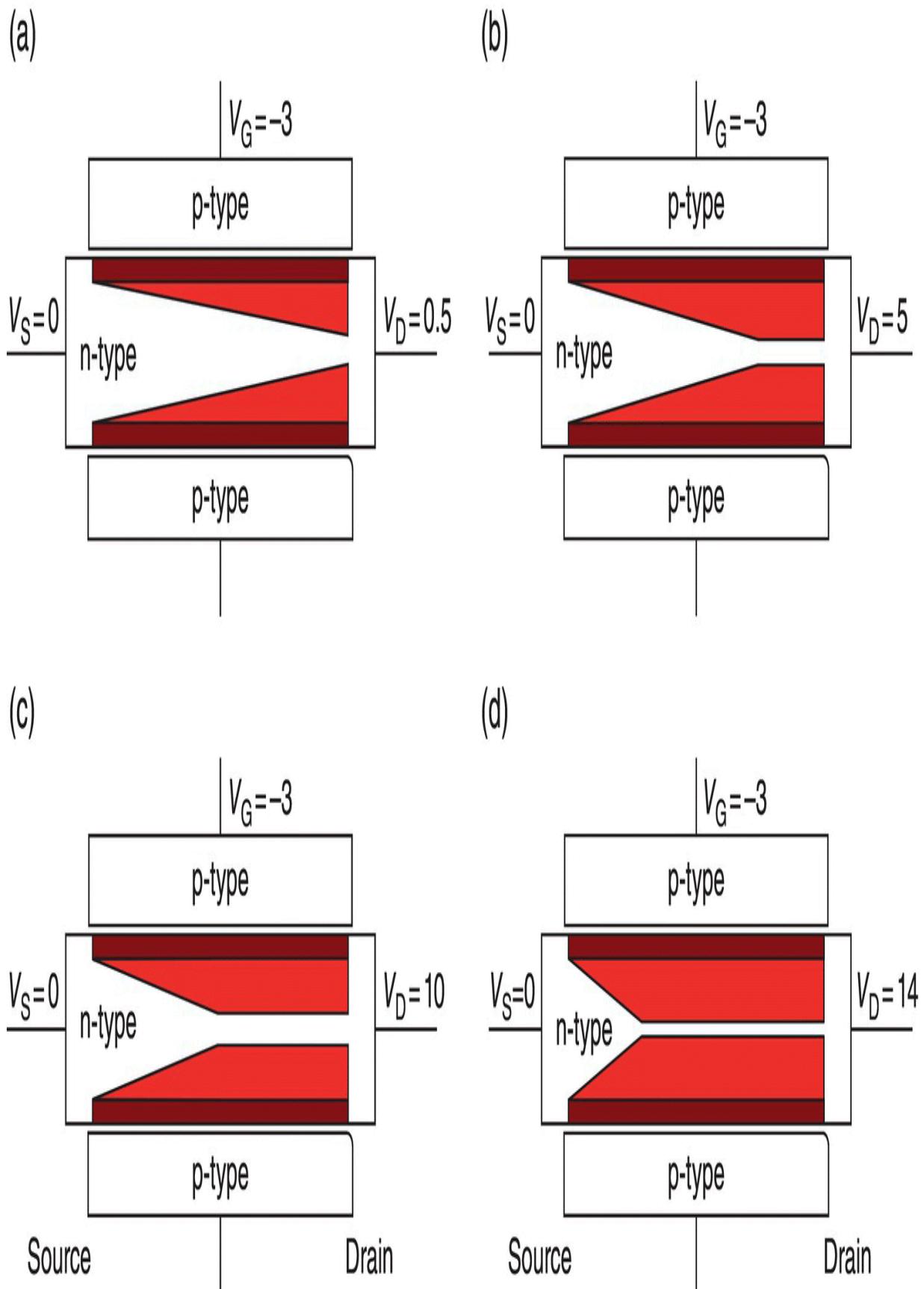

Figure 8.11 The voltage between the drain and the gate is different to that ...

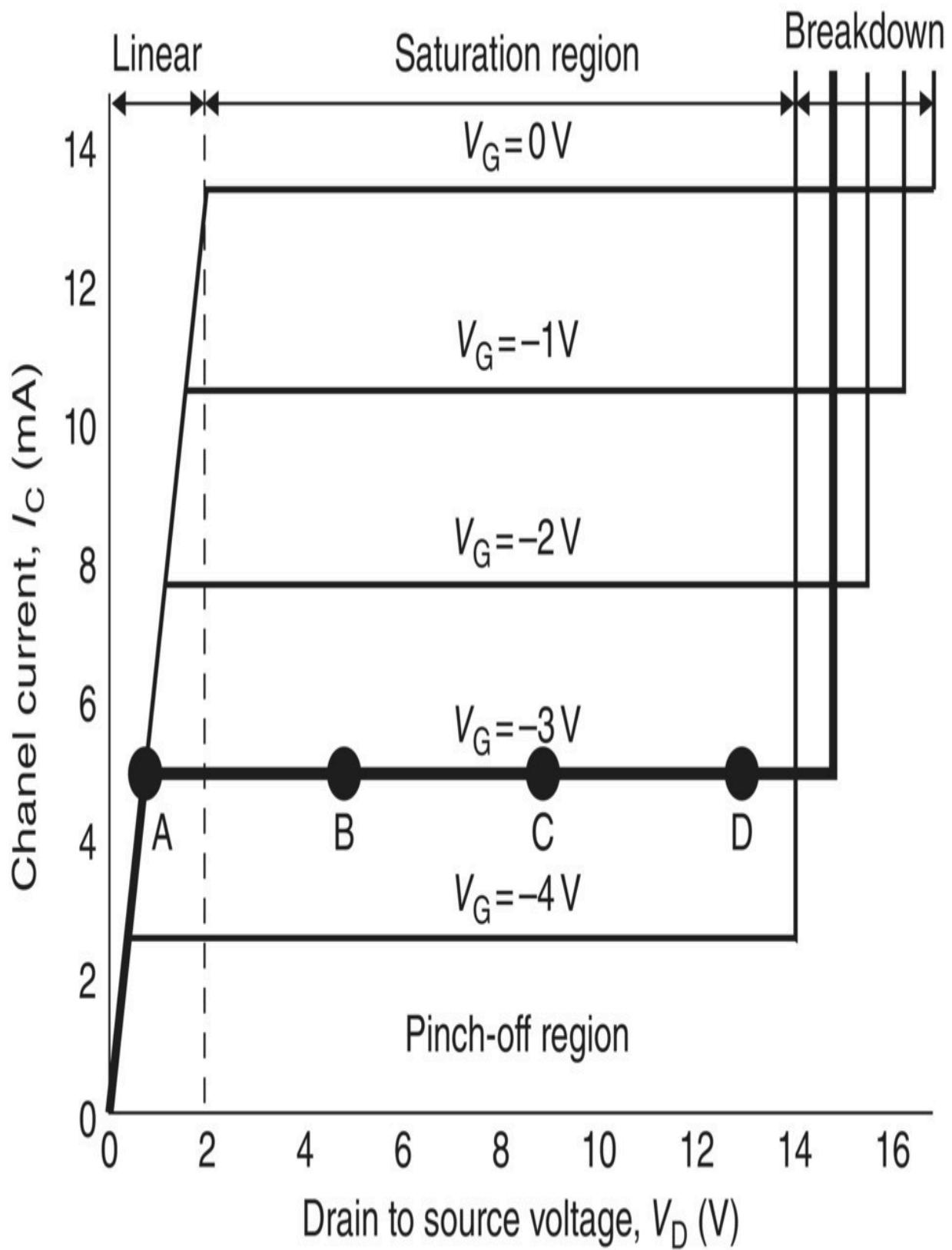

Figure 8.12 The idealized characteristics of a pnp JFET show three distinct ...

Figure 8.13 The pinch-off voltage grows and moves closer to the source as th...

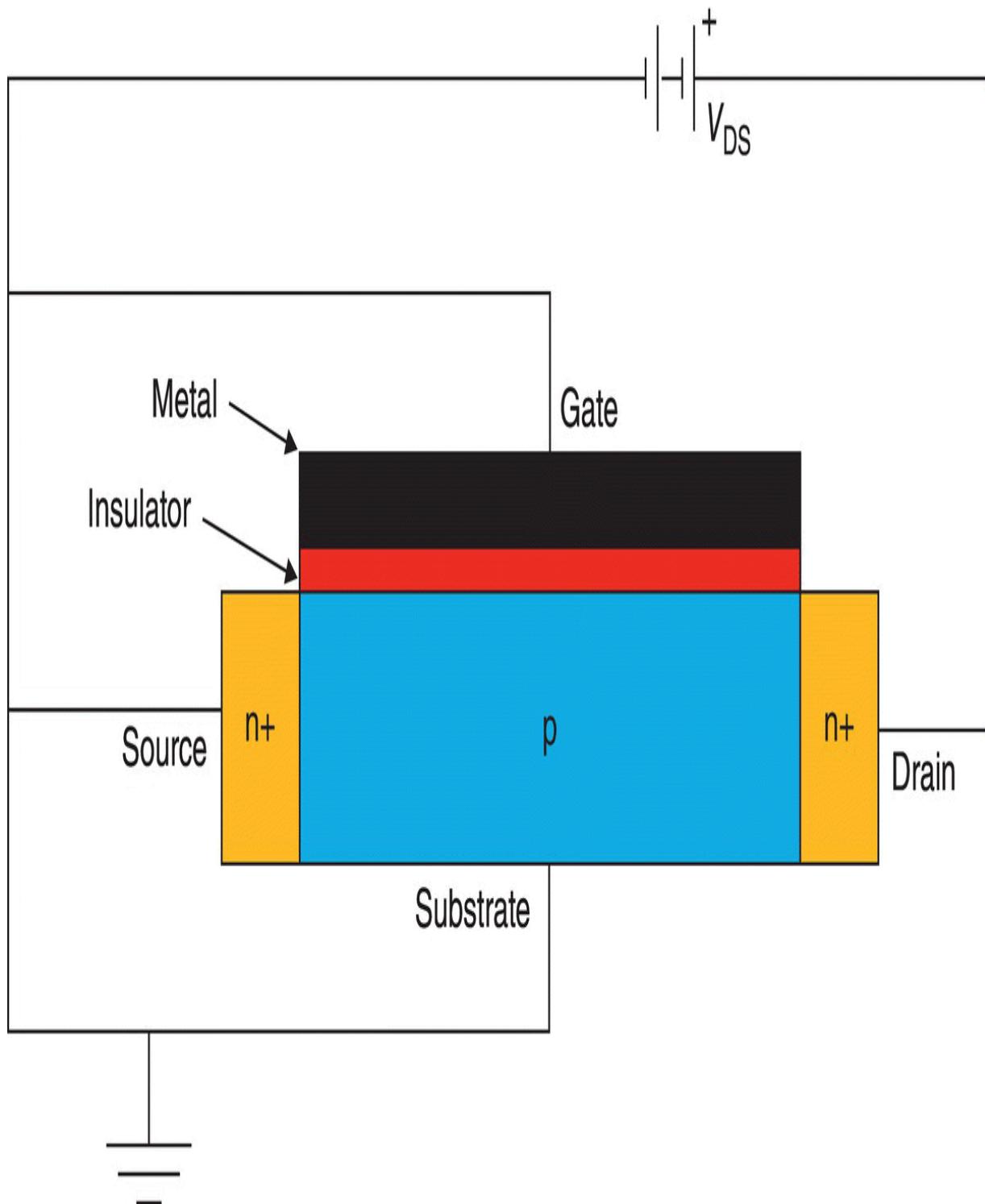

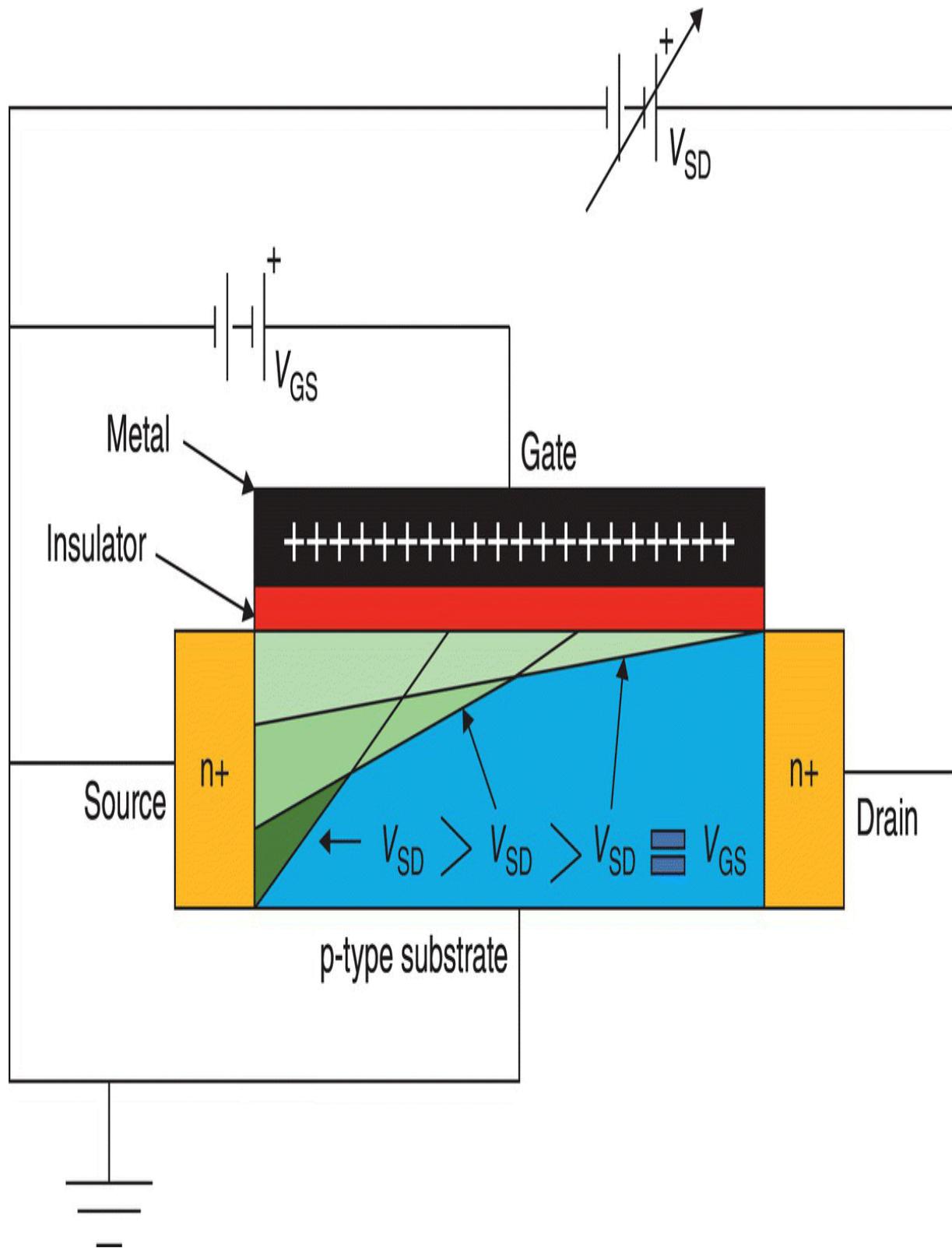

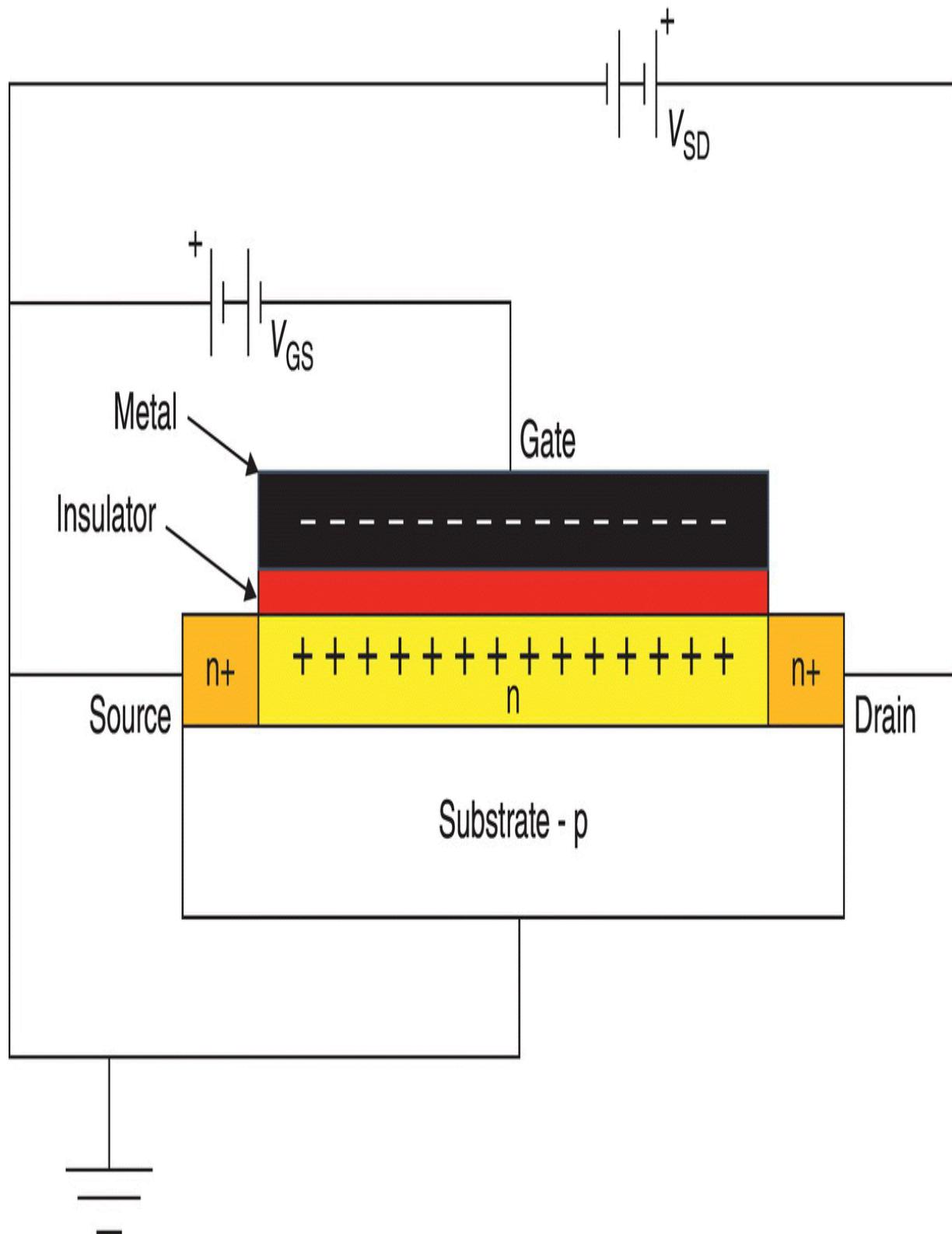

Figure 8.14 In a MOSFET one of the two semiconductor gates in a JFET is repl...

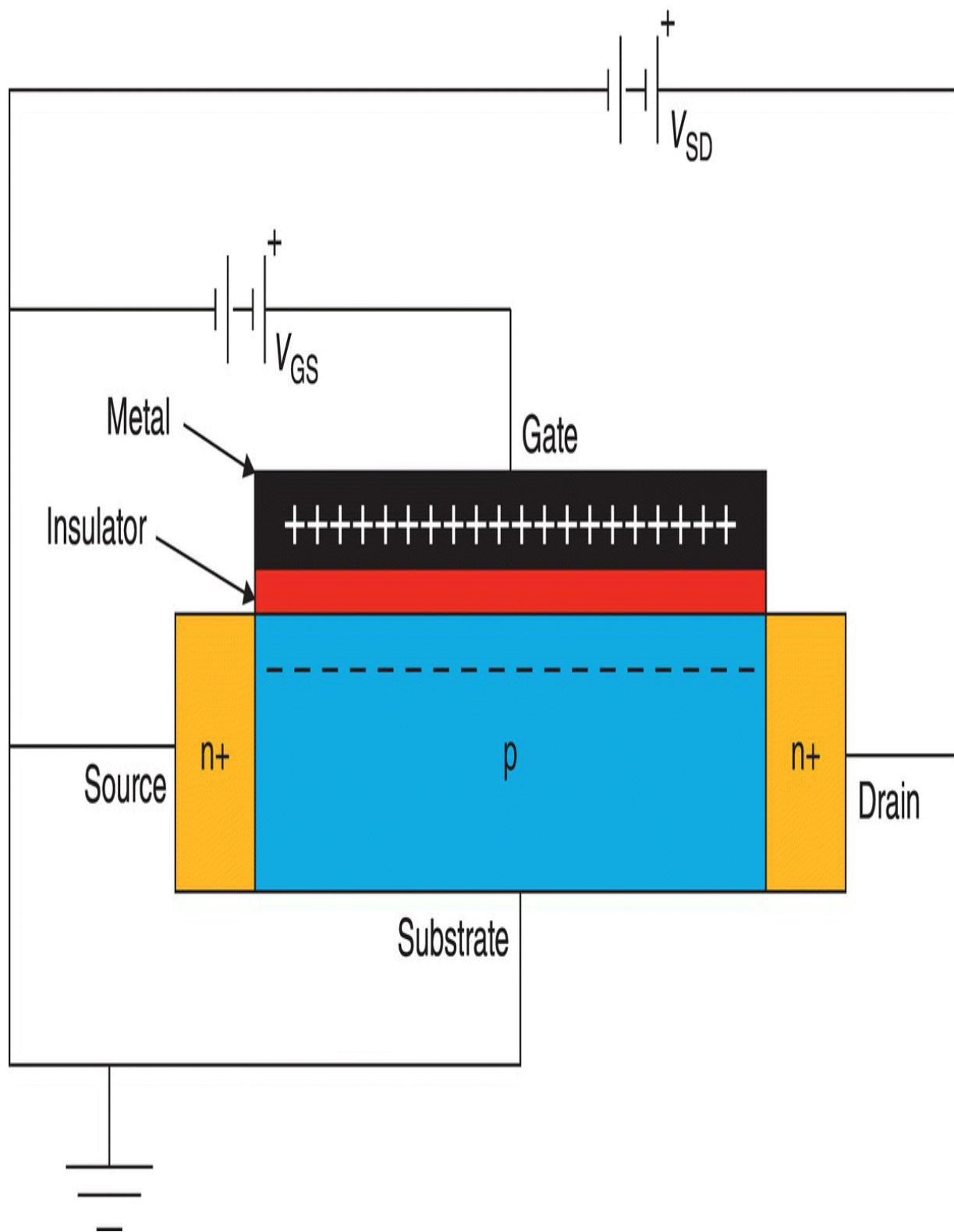

Figure 8.15 If the gate of a p-type MOSFET is positive, electrons are attrac...

Figure 8.16 A MOSFET showing the region with electrons in the channel under ...

Figure 8.17 Idealized source to drain current as a function of the drain vol...

Figure 8.18 In a depletion mode MOSFET the channel is made more resistive by...

Figure 8.19 The relationships of the variety of transistors discussed in thi...

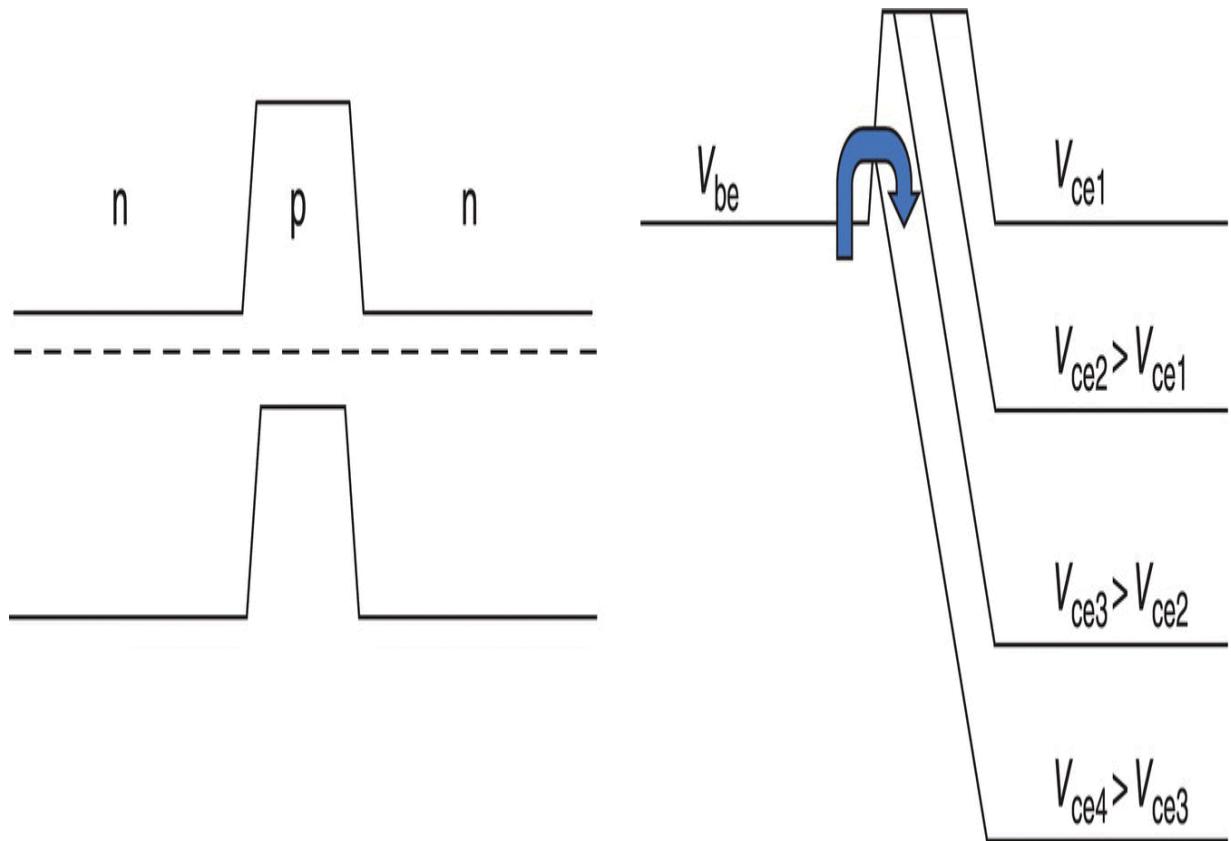

[Figure 8.20 The energy bands in an npn-transistor \(left\) and what happens to...](#)

Chapter 9

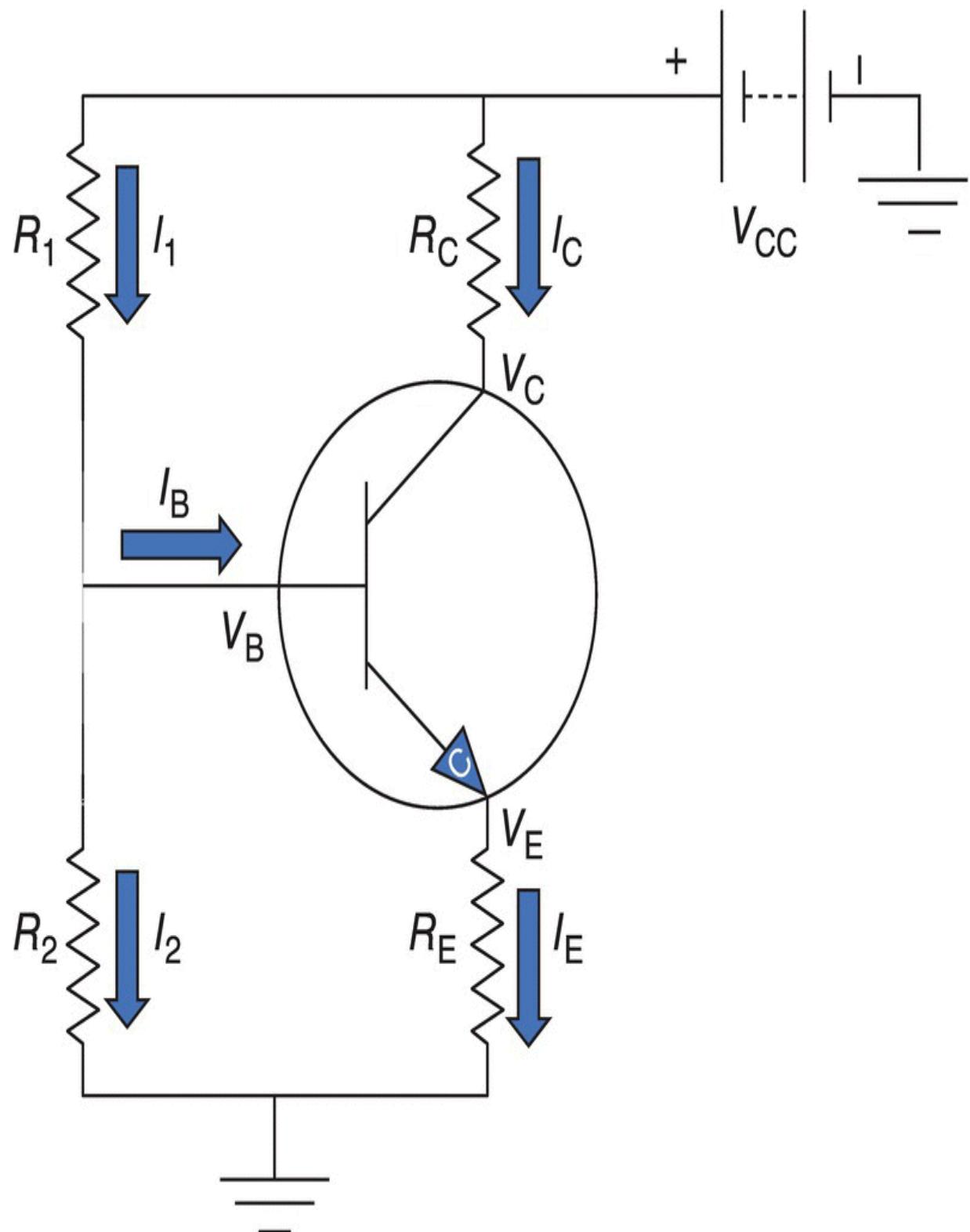

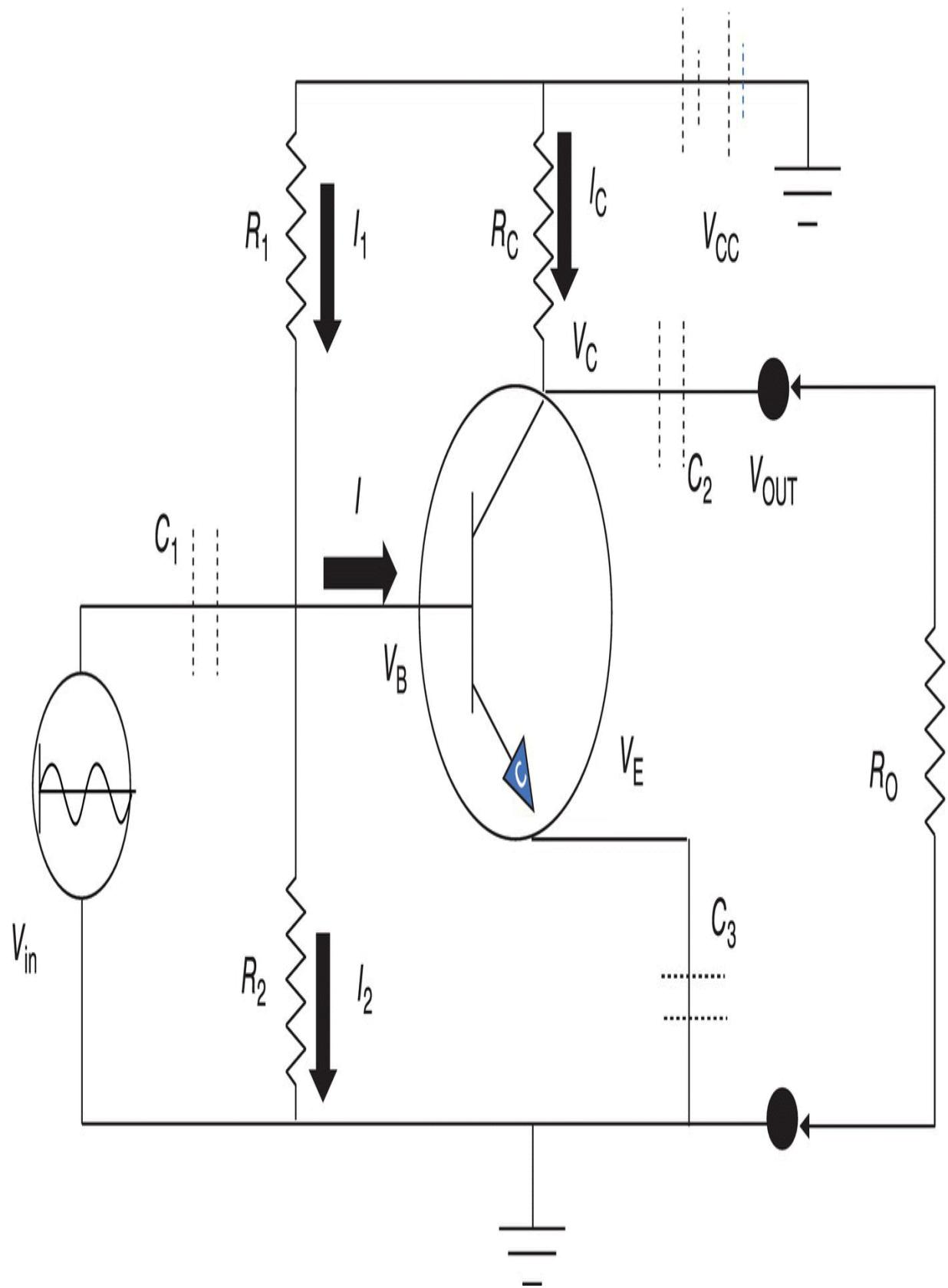

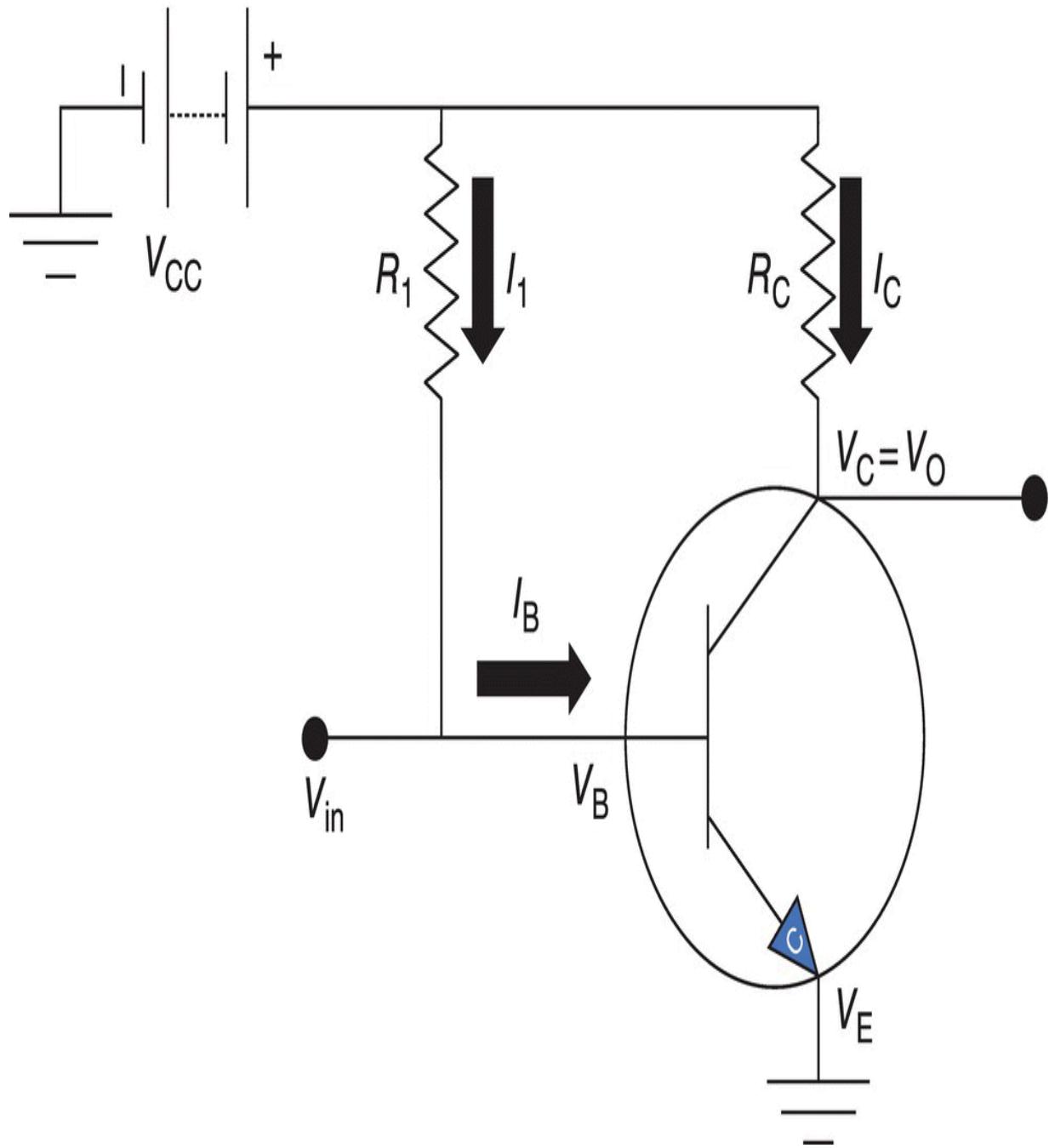

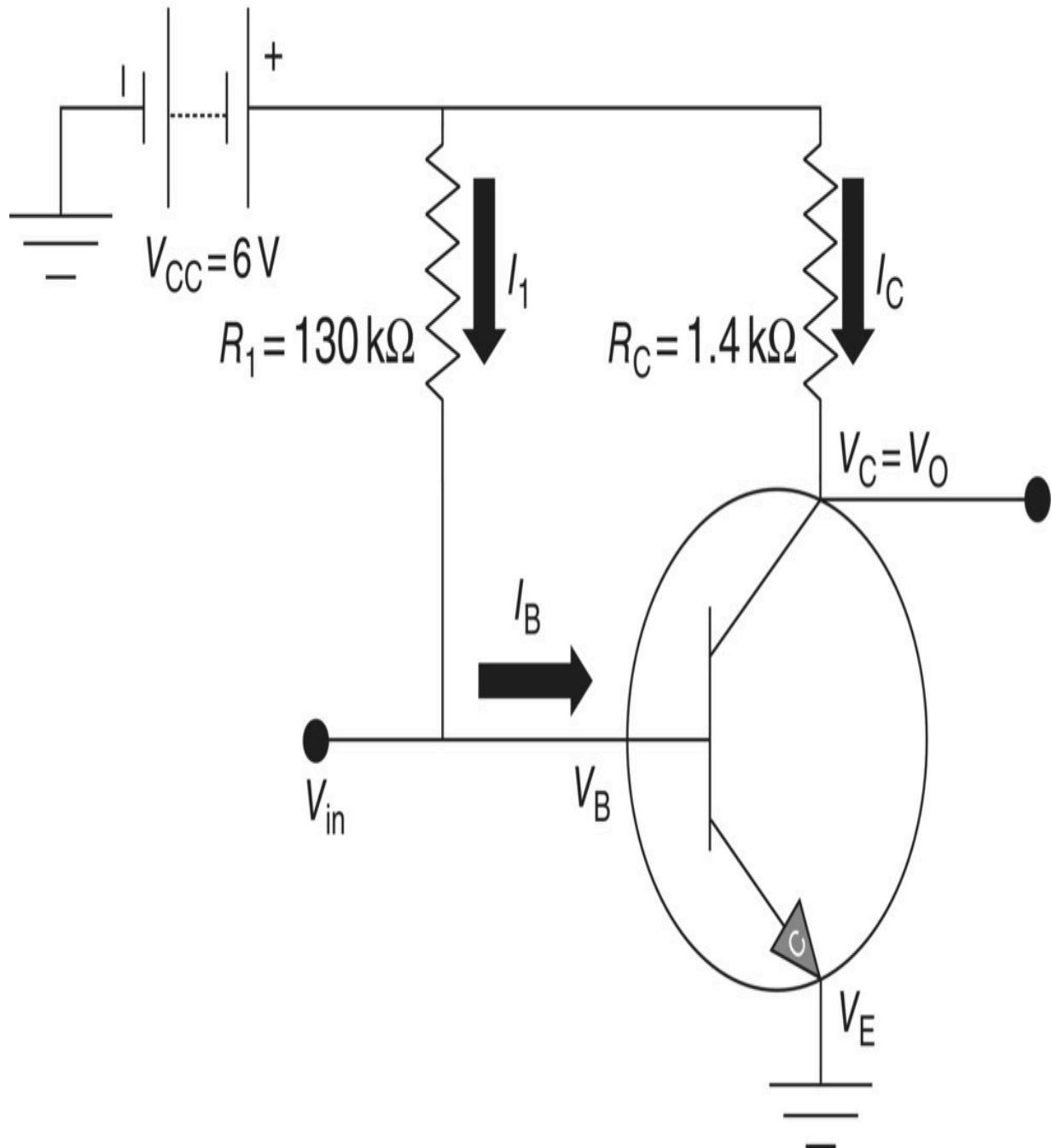

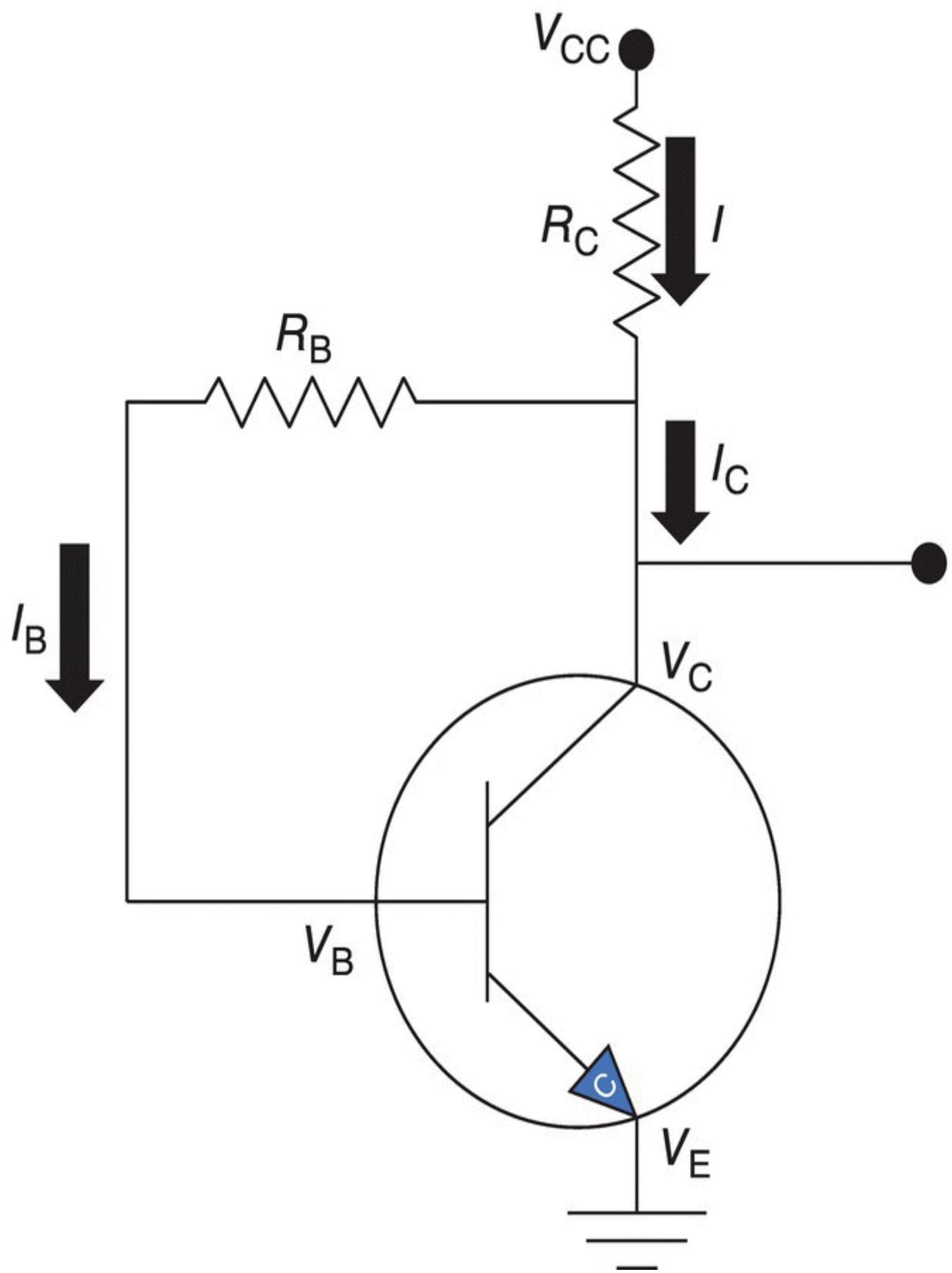

[Figure 9.1 The emitter feedback bias circuit has the highest stability as th...](#)

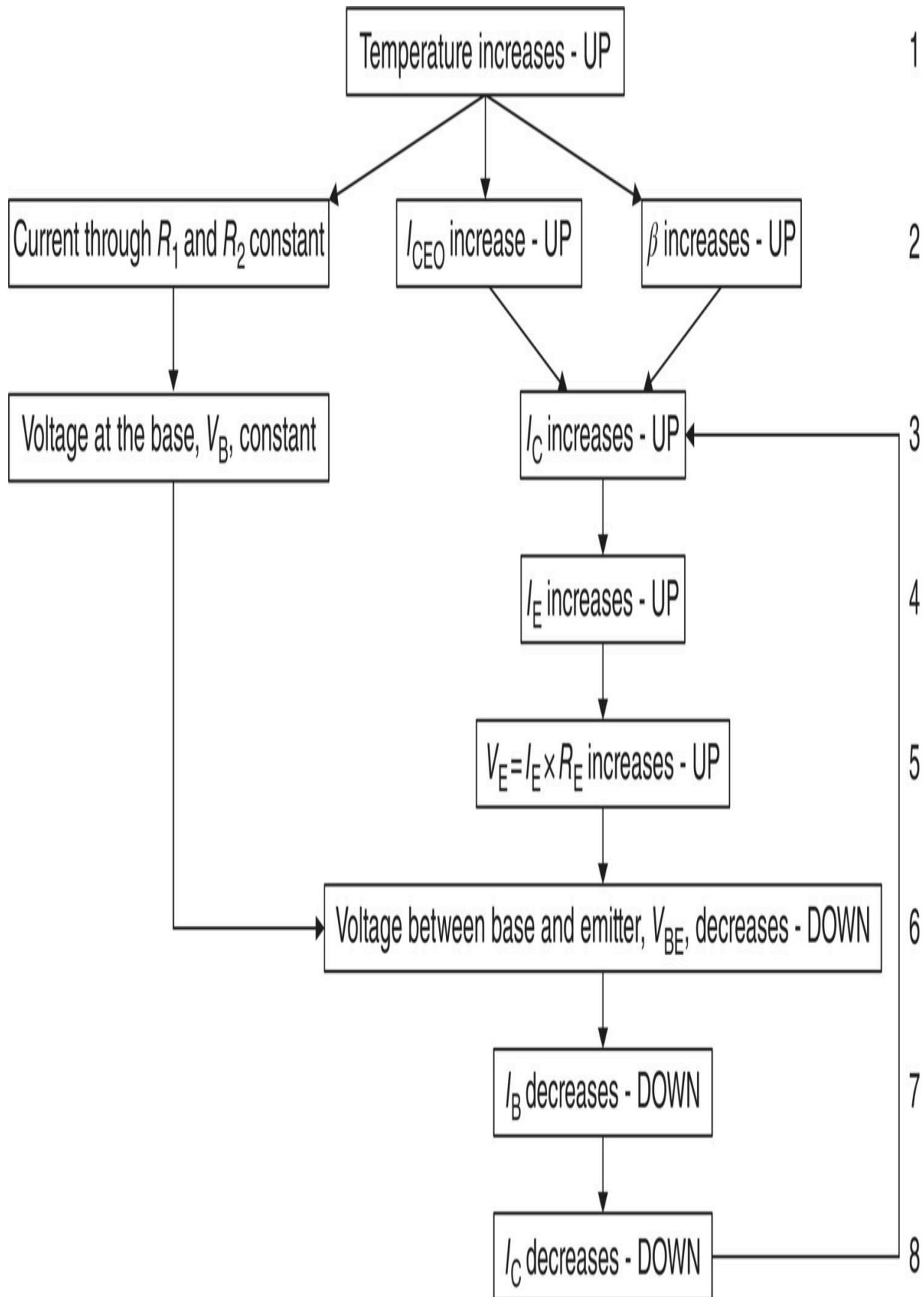

[Figure 9.2 This flow diagram shows how the emitter negative feedback stabili...](#)

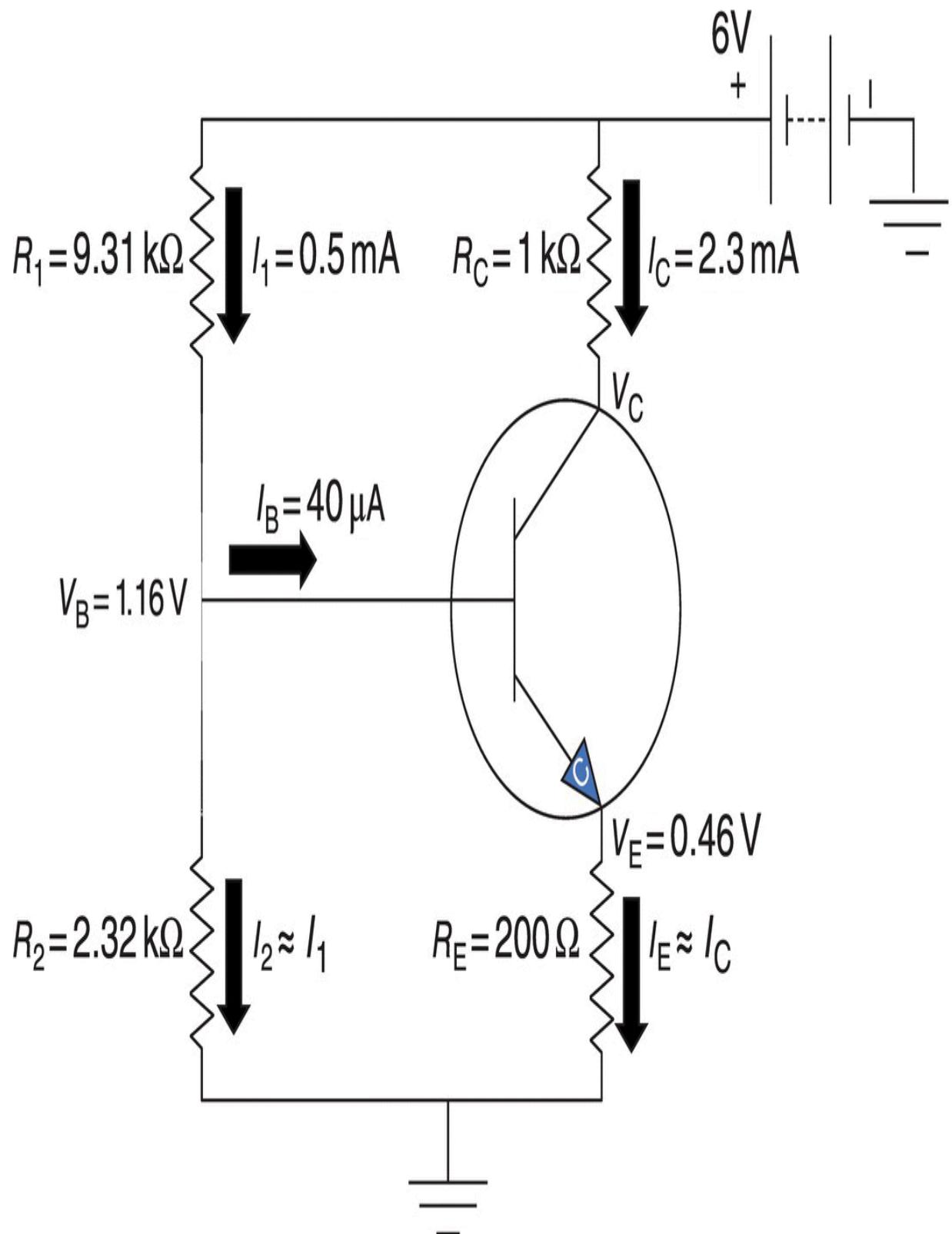

[Figure 9.3 Emitter feedback bias circuit with the resistor values we need to...](#)

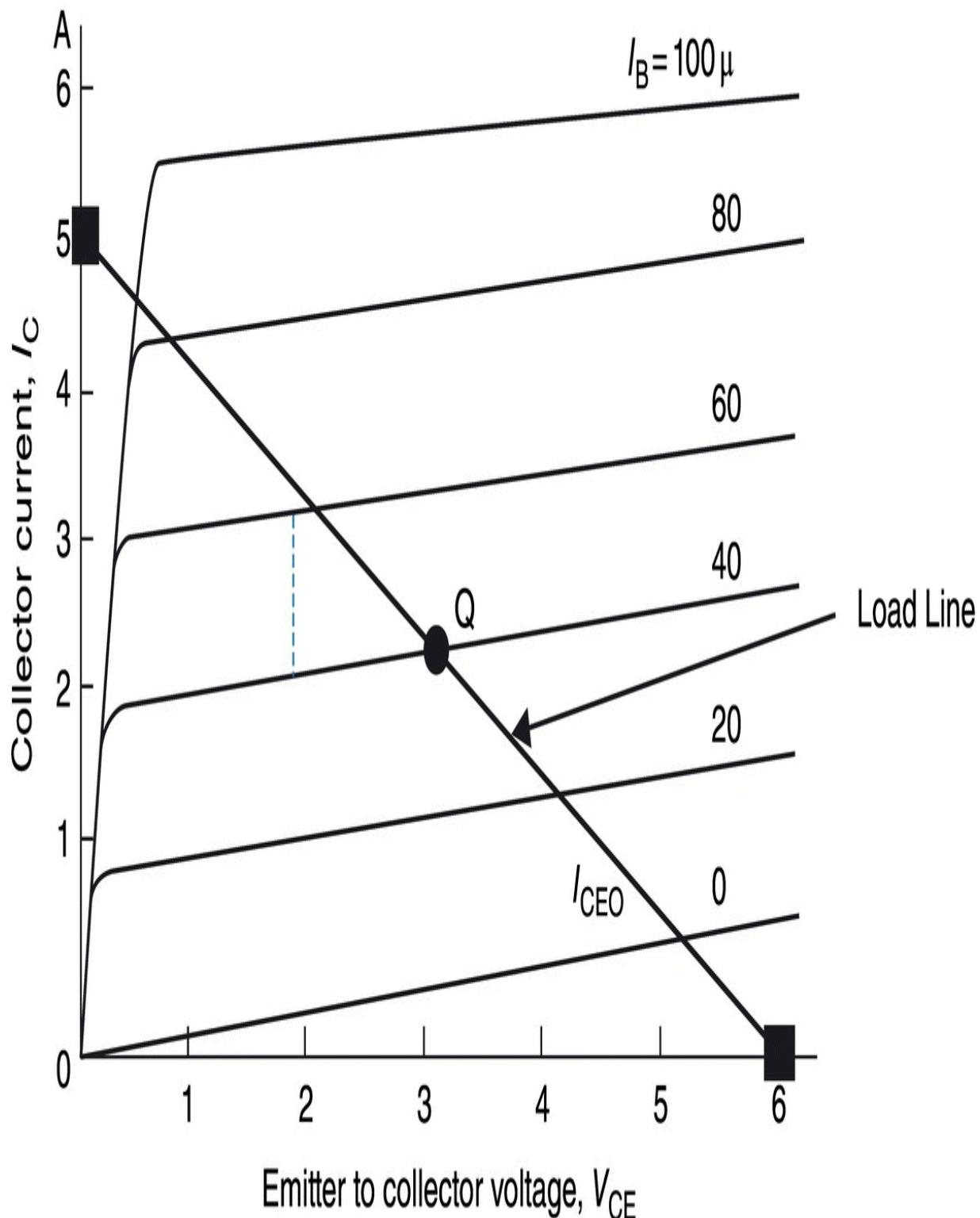

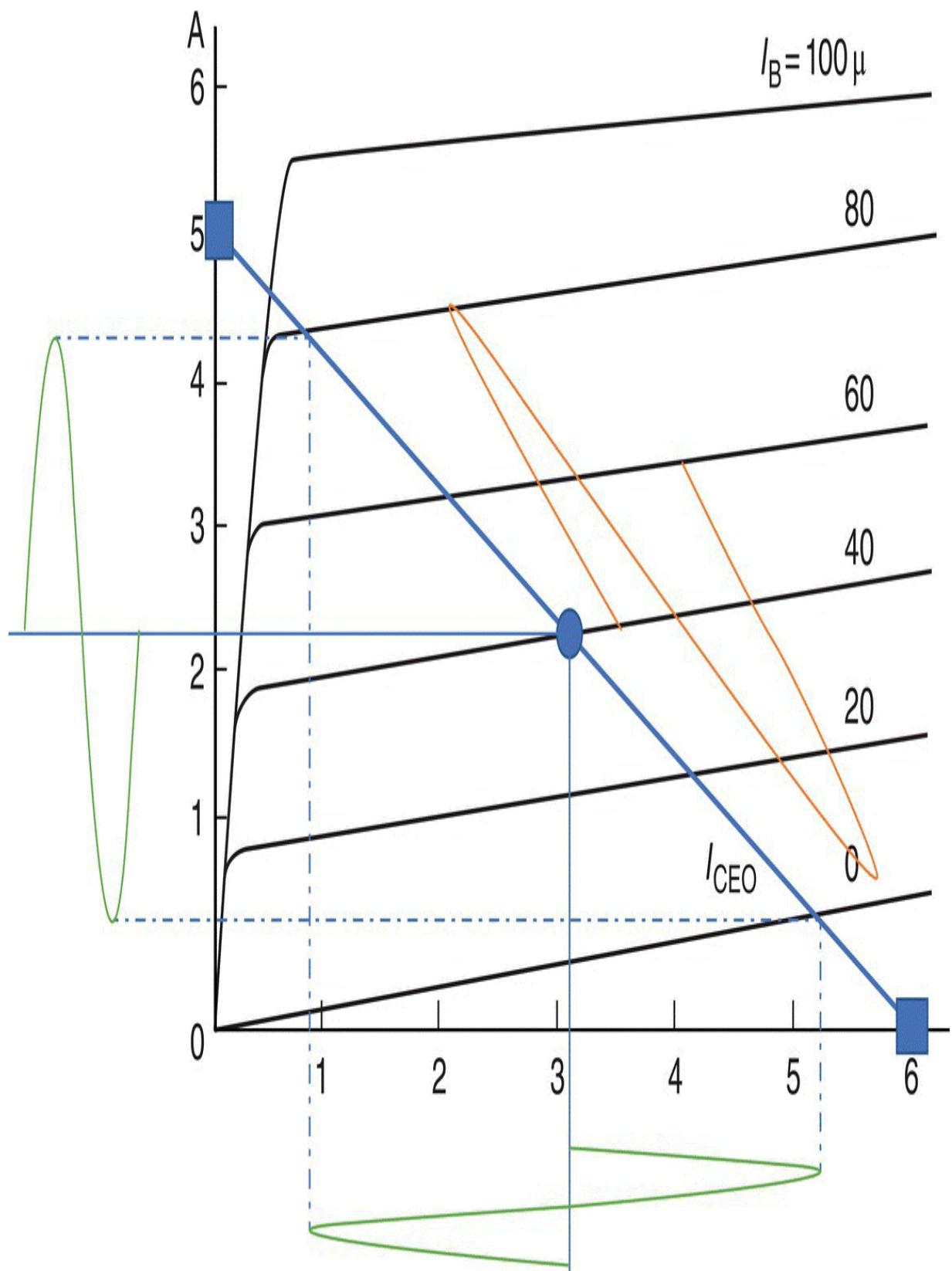

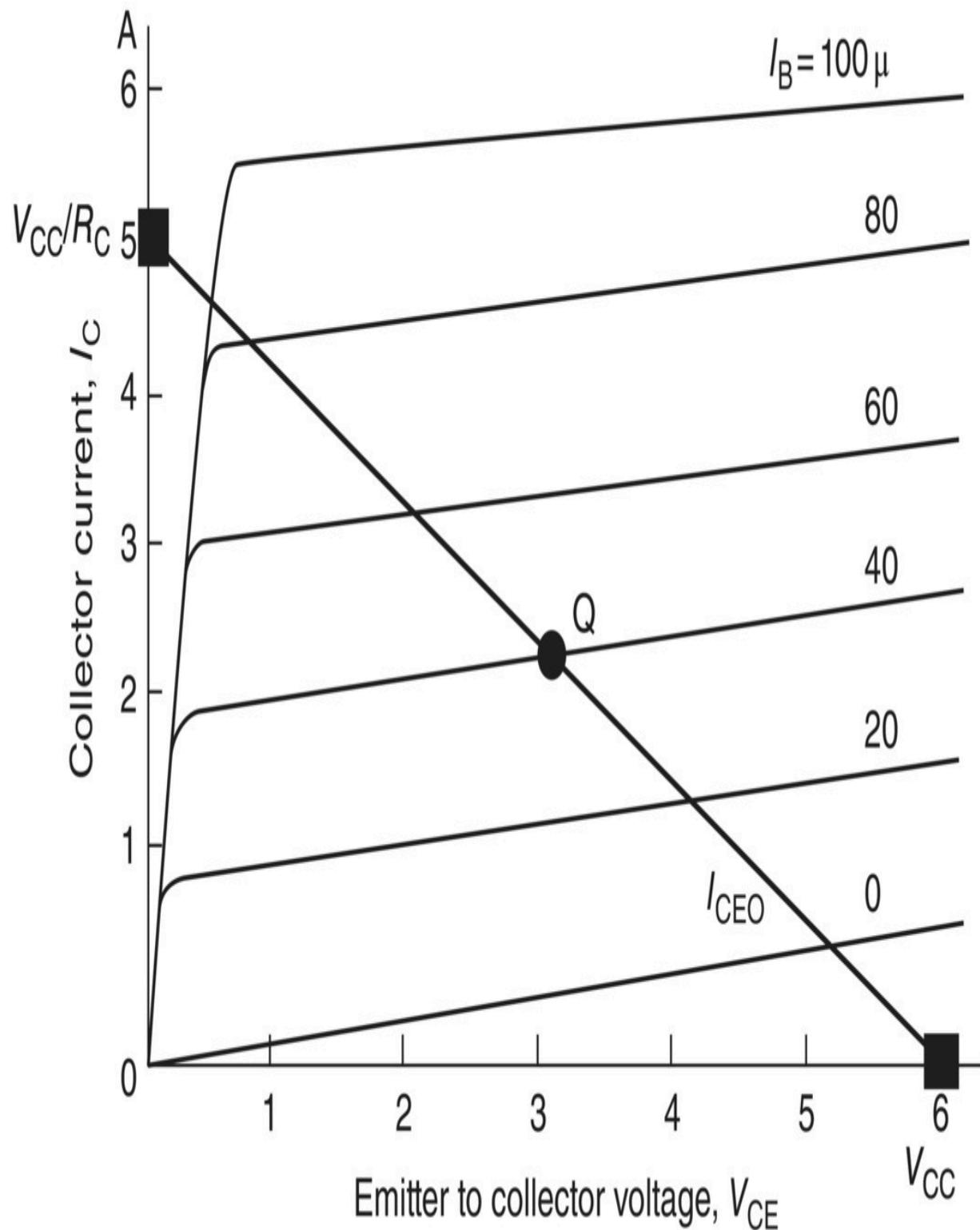

[Figure 9.4 The load line that determines the output voltage-current relation...](#)

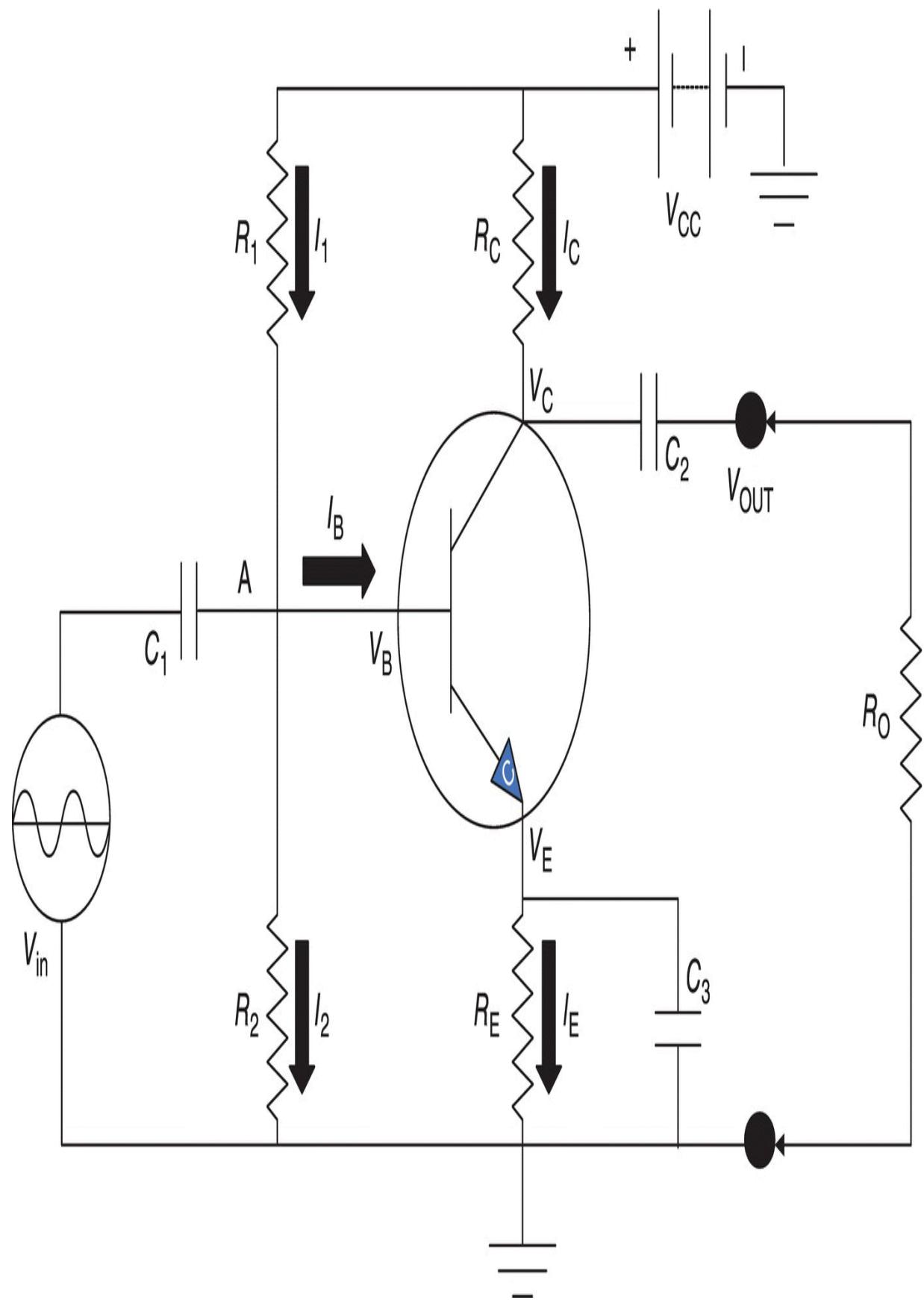

[Figure 9.5 By adding a sinusoidal signal using capacitors we can modulate th...](#)

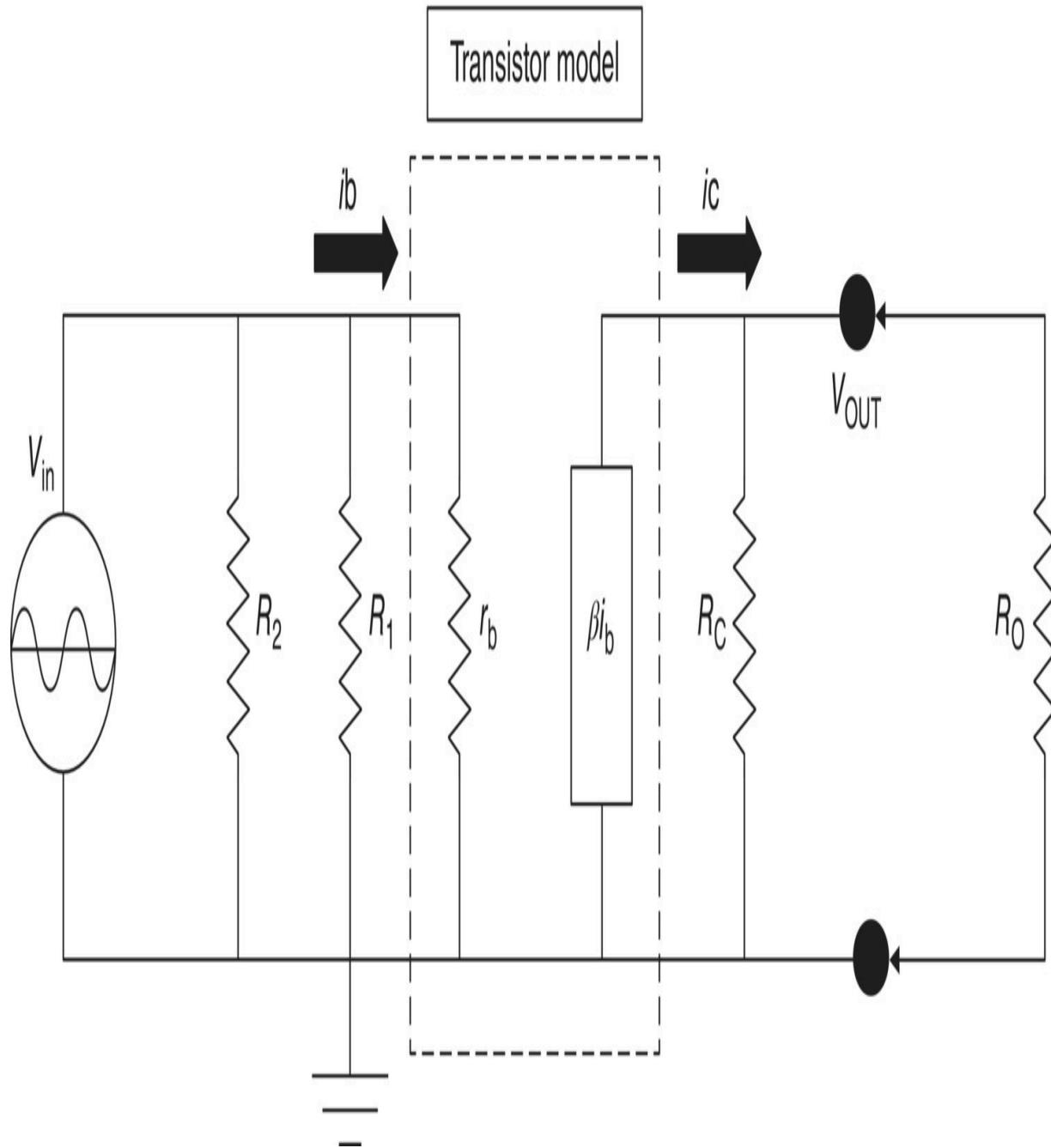

[Figure 9.6 From a sinusoidal source point of view the capacitors and the bat...](#)

[Figure 9.7 The AC equivalent circuit of a transistor consisting of an input ...](#)

[Figure 9.8 We can superimpose the sinusoidal signals on the transistor chara...](#)

[Figure 9.9 The fixed bias circuit is simpler than the collector feedback cir...](#)

[Figure 9.10 The load line on the transistor characteristic curves for a fixe...](#)

[Figure 9.11 The fixed bias circuit with the resistance values we have calcul...](#)

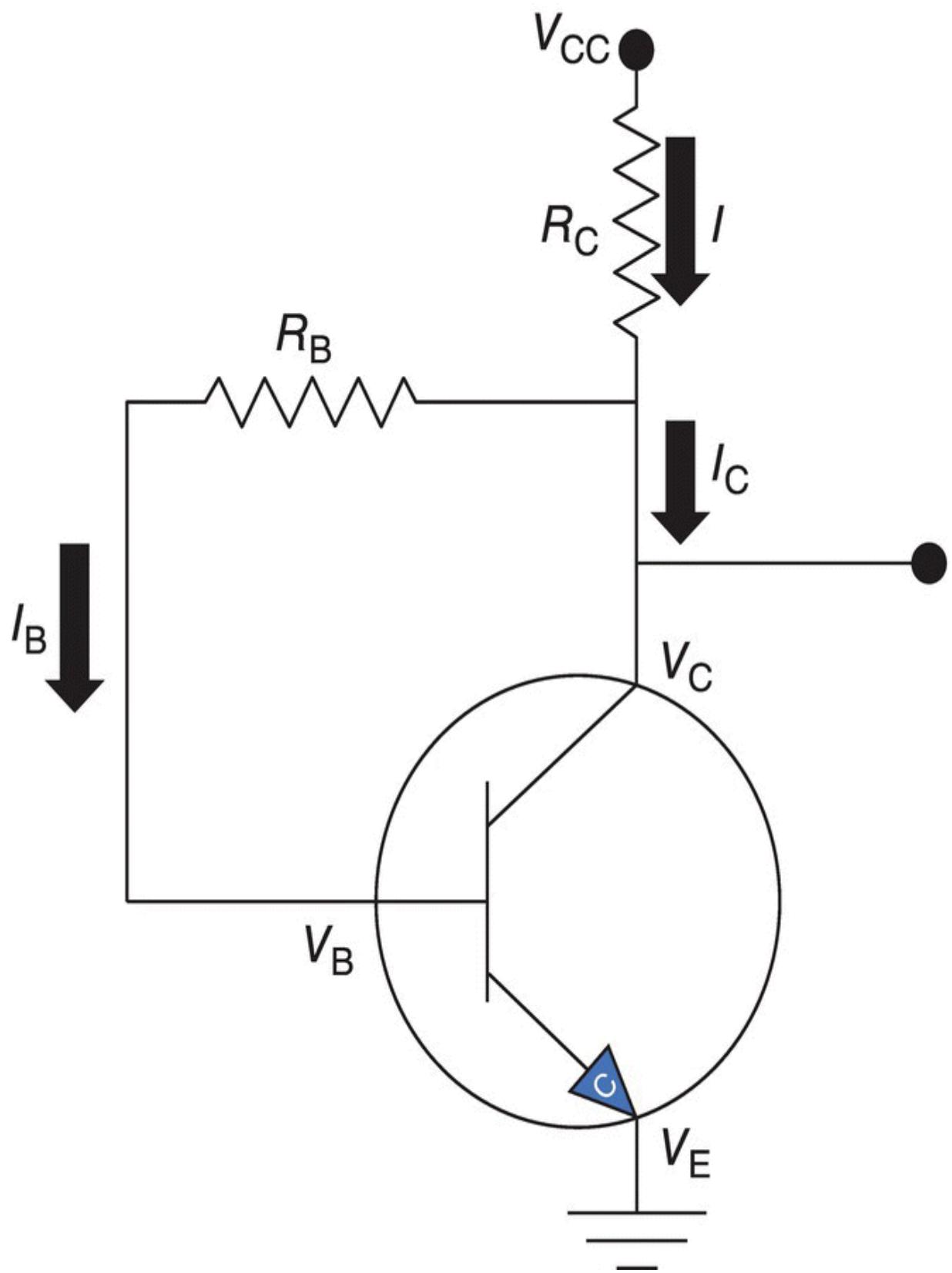

[Figure 9.12 The collector feedback bias circuit is a different way of stabili...](#)

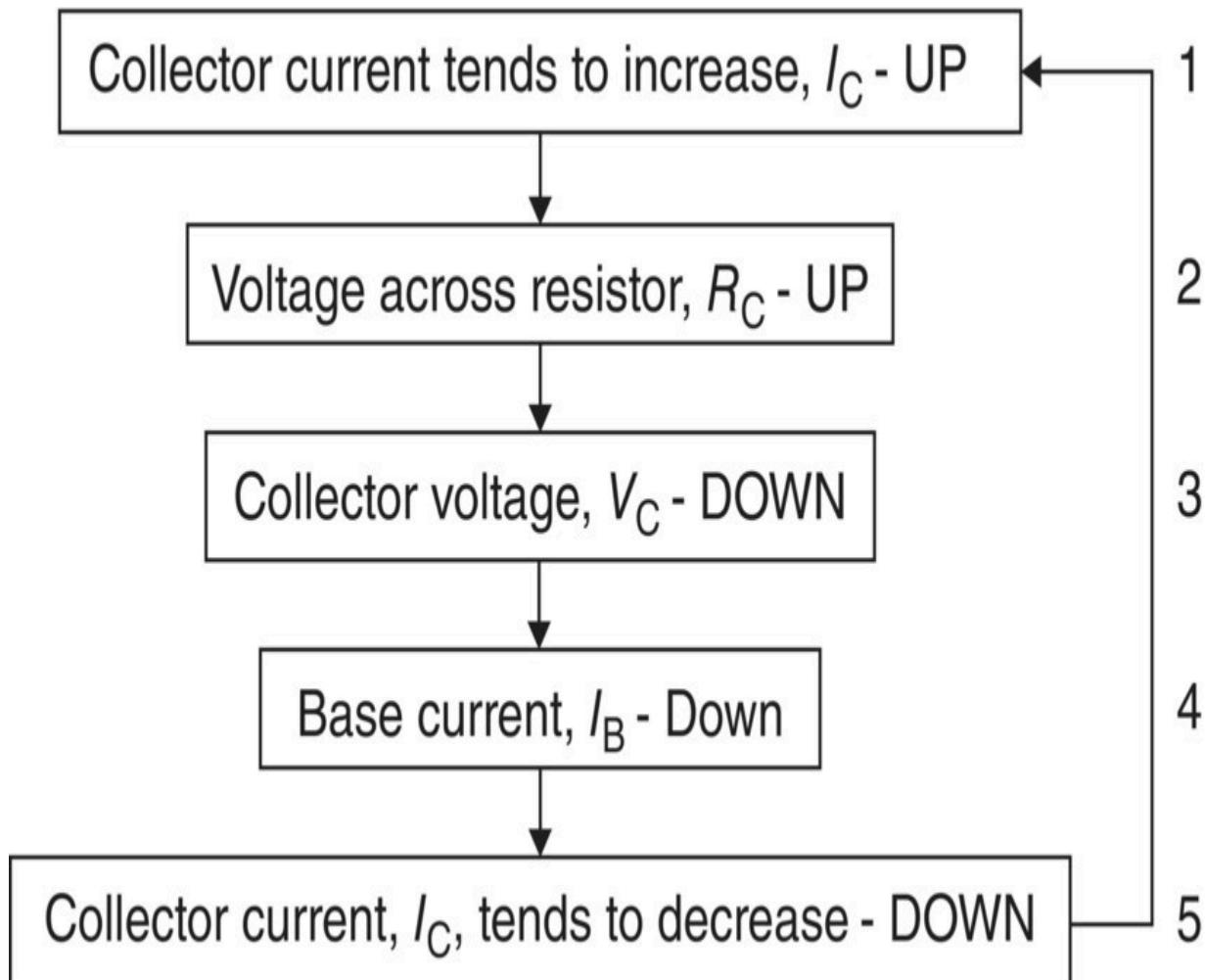

[Figure 9.13 Stabilization diagram of the collector feedback circuit.](#)

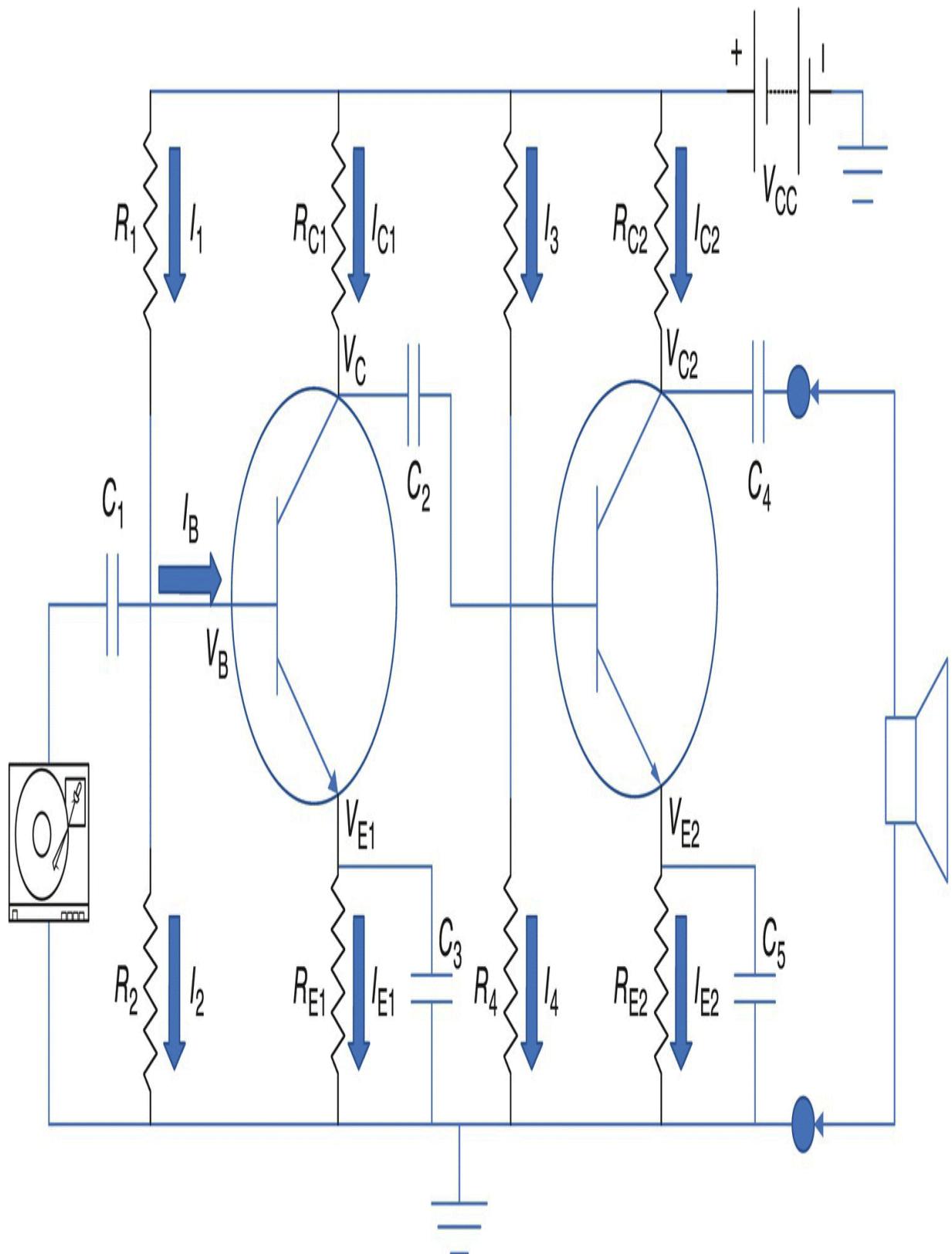

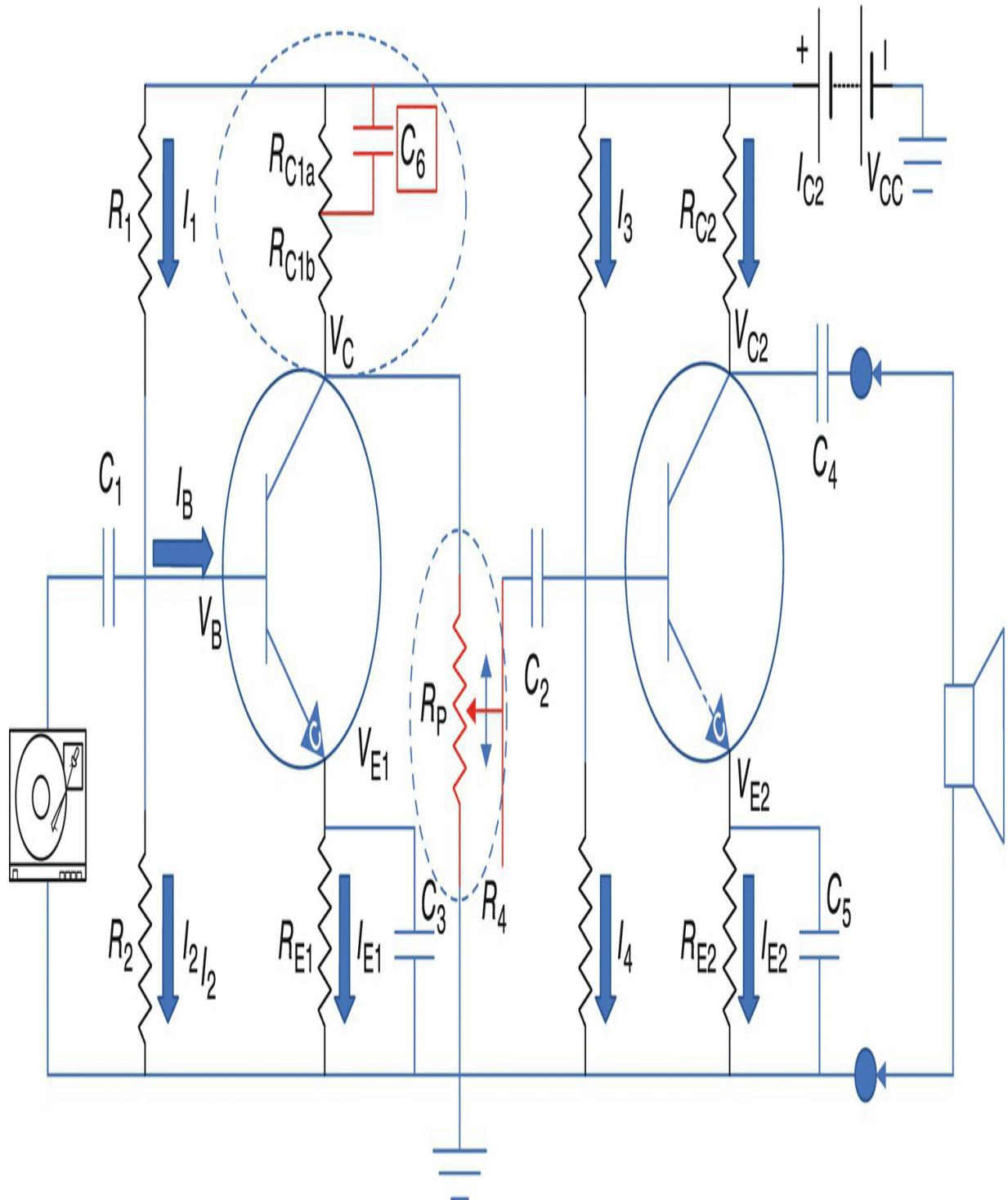

[Figure 9.14 By connecting two transistor circuits with appropriate capacitor...](#)

[Figure 9.15 By adding a potentiometer and a bypass capacitor \(both in red\) t...](#)

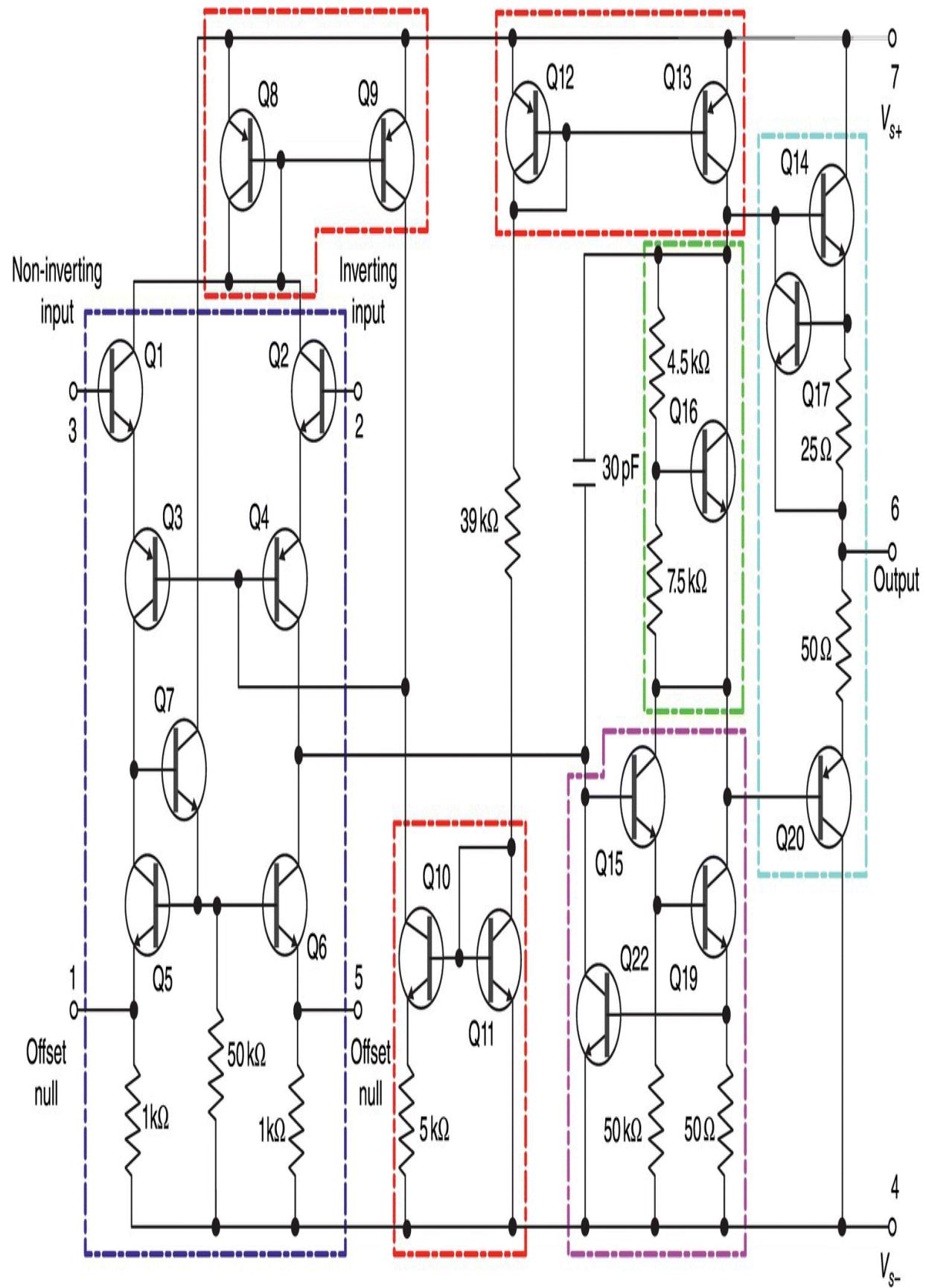

[Figure 9.16 The internal circuit of an OpAmp, the Fairchild 741.](#)

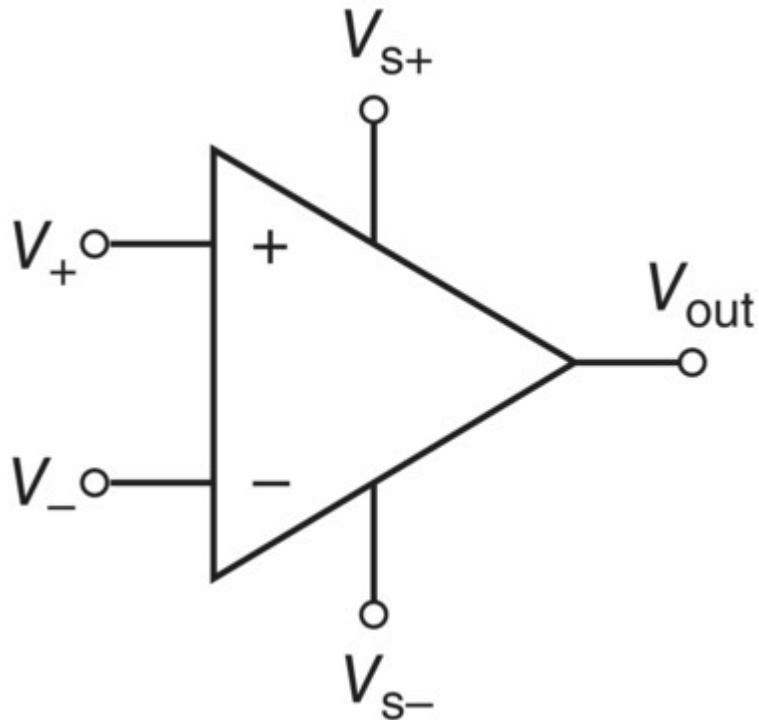

[Figure 9.17 The symbol for an OpAmp with two supply voltages, one positive a...](#)

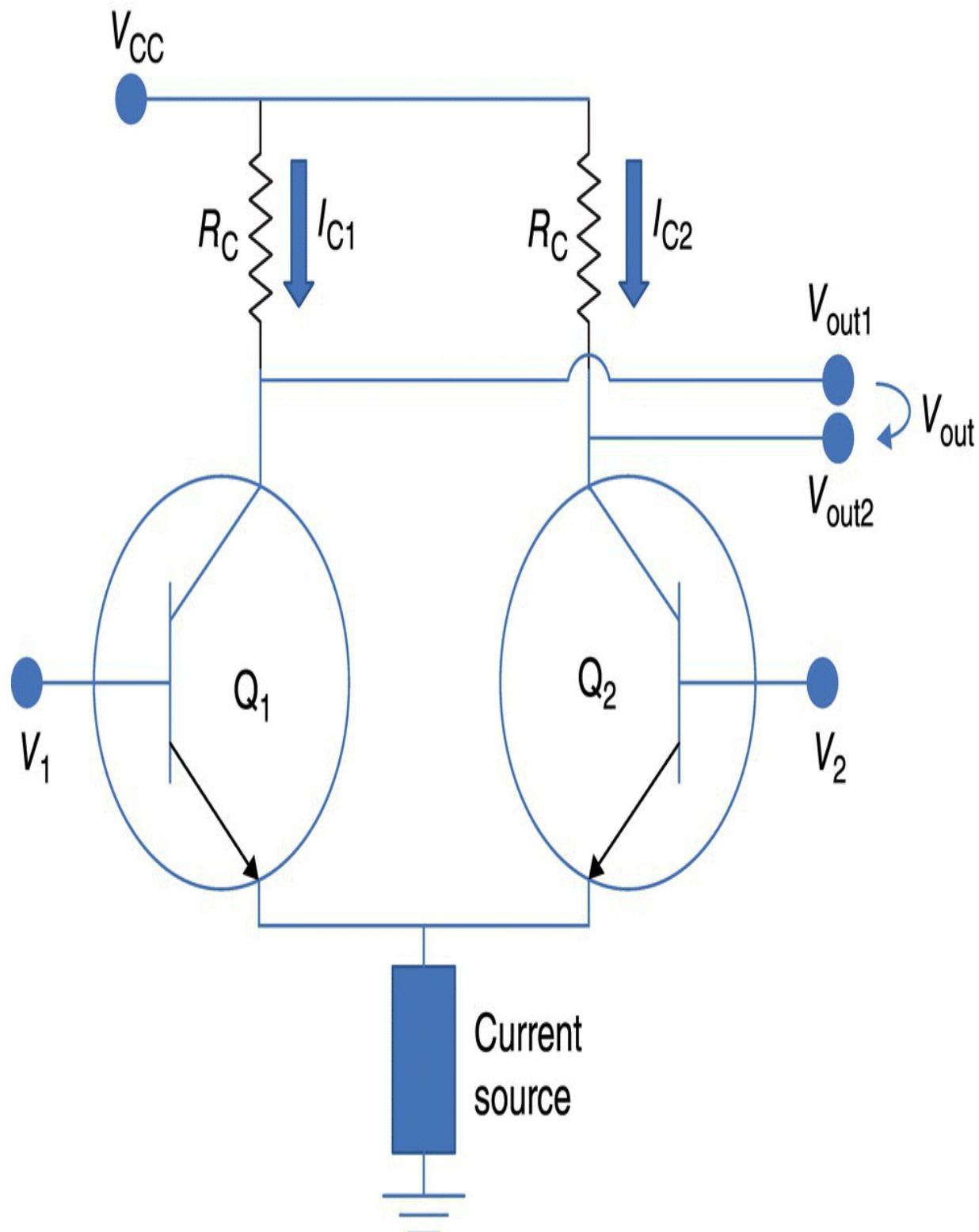

[Figure 9.18 A differential input amplifier eliminates many of the noise prob...](#)

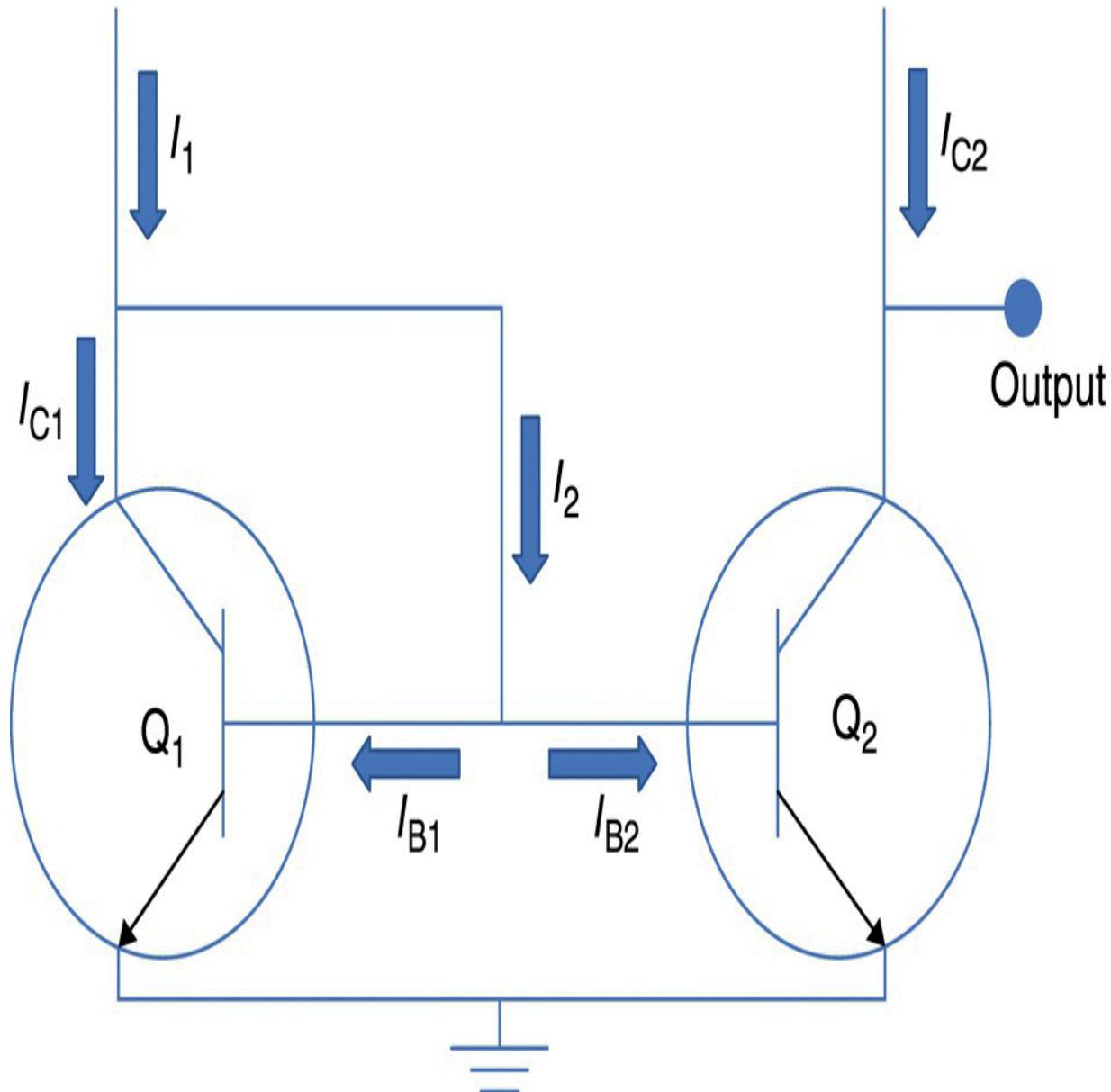

[Figure 9.19 A current mirror ensures that the output current,  \$I\_{C2}\$ , is the sa...](#)

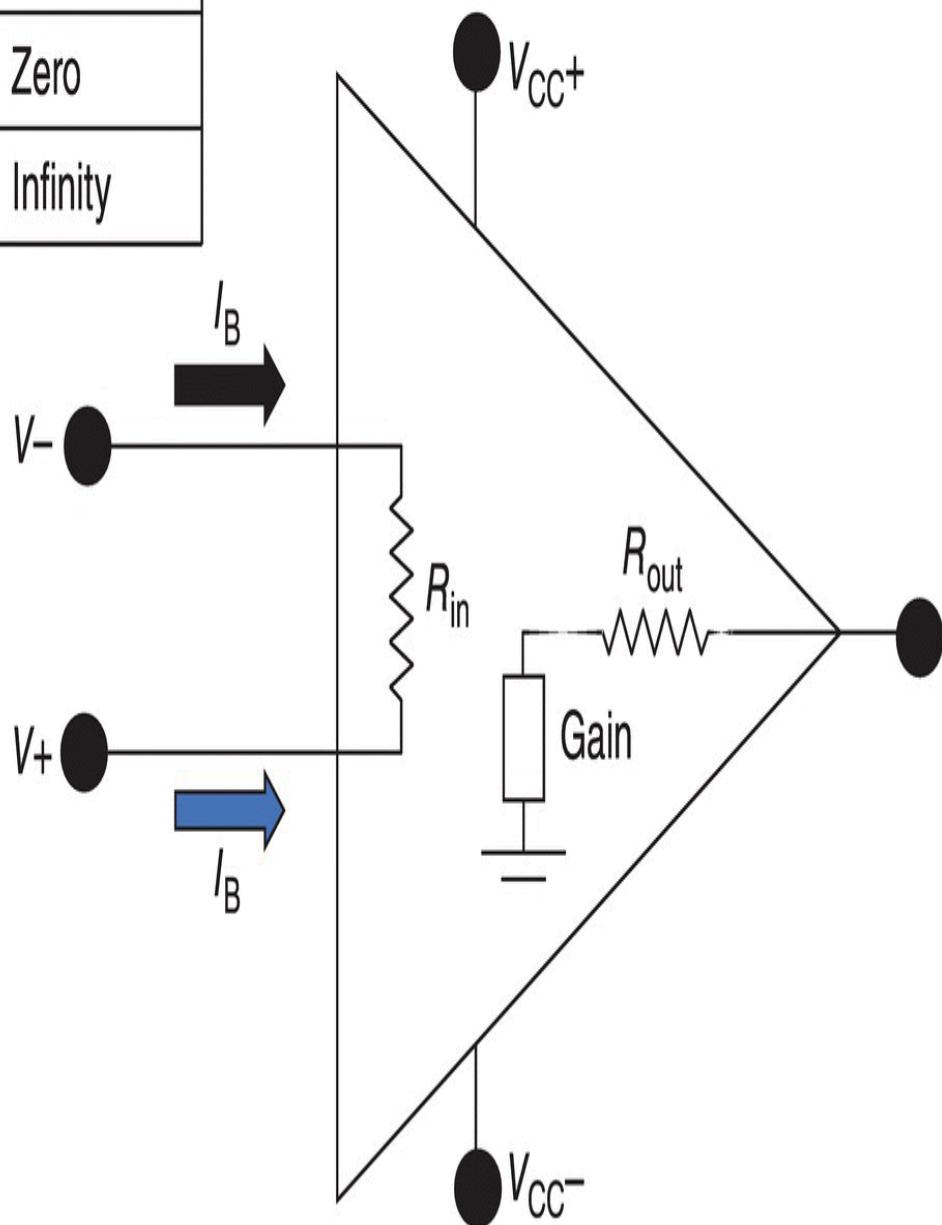

[Figure 9.20 The ideal OpAmp has an infinite resistance, zero output resistan...](#)

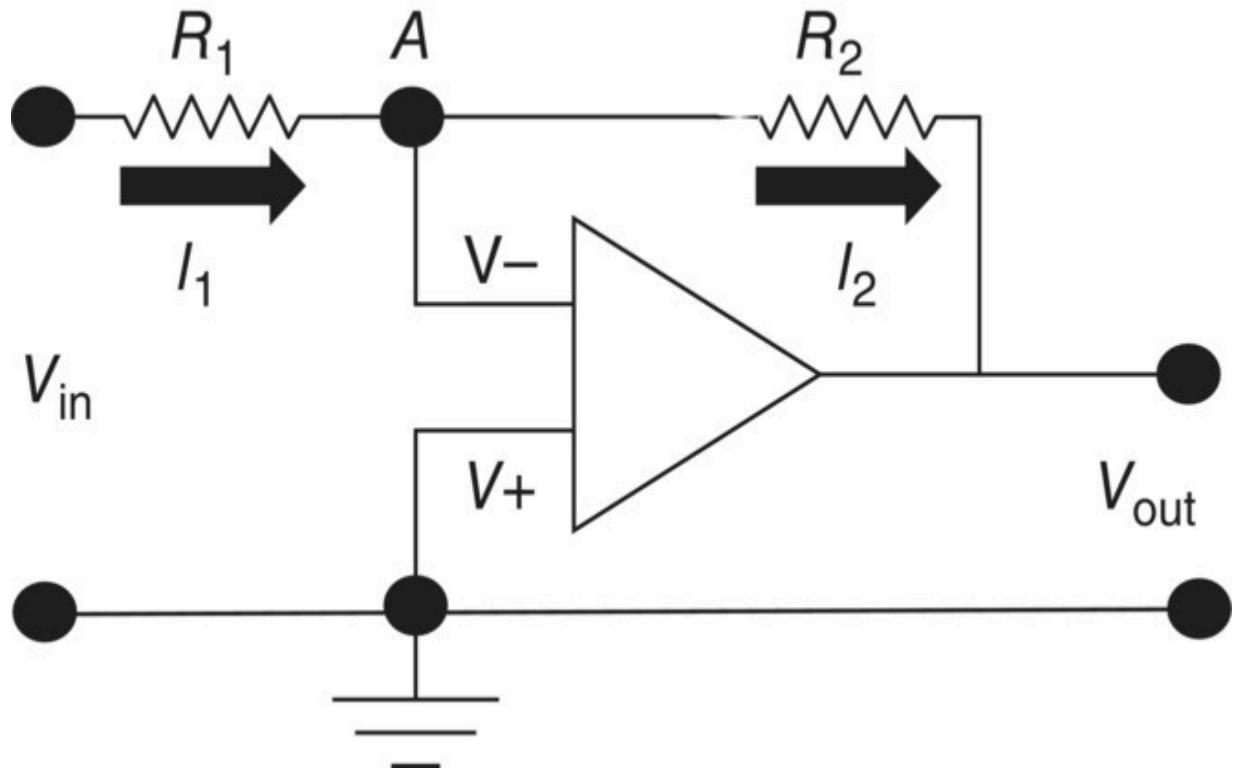

[Figure 9.21 An inverting OpAmp has a gain defined by the ratio of the two re...](#)

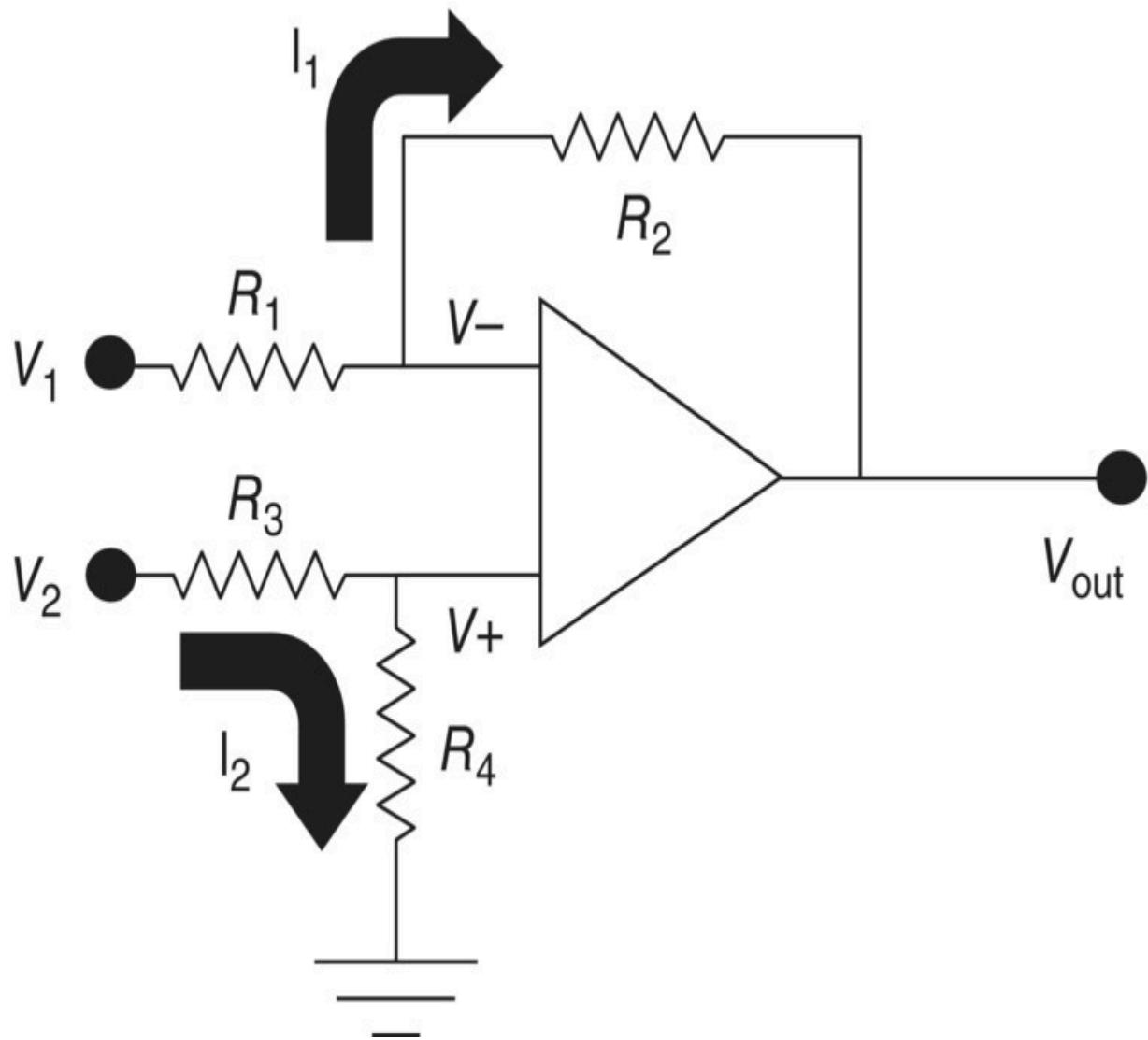

[Figure 9.22 A differential amplifier provides a gain defined by the ratio of...](#)

[Figure 9.23 The collector feedback bias circuit is a different way of stabil...](#)

## Chapter 10

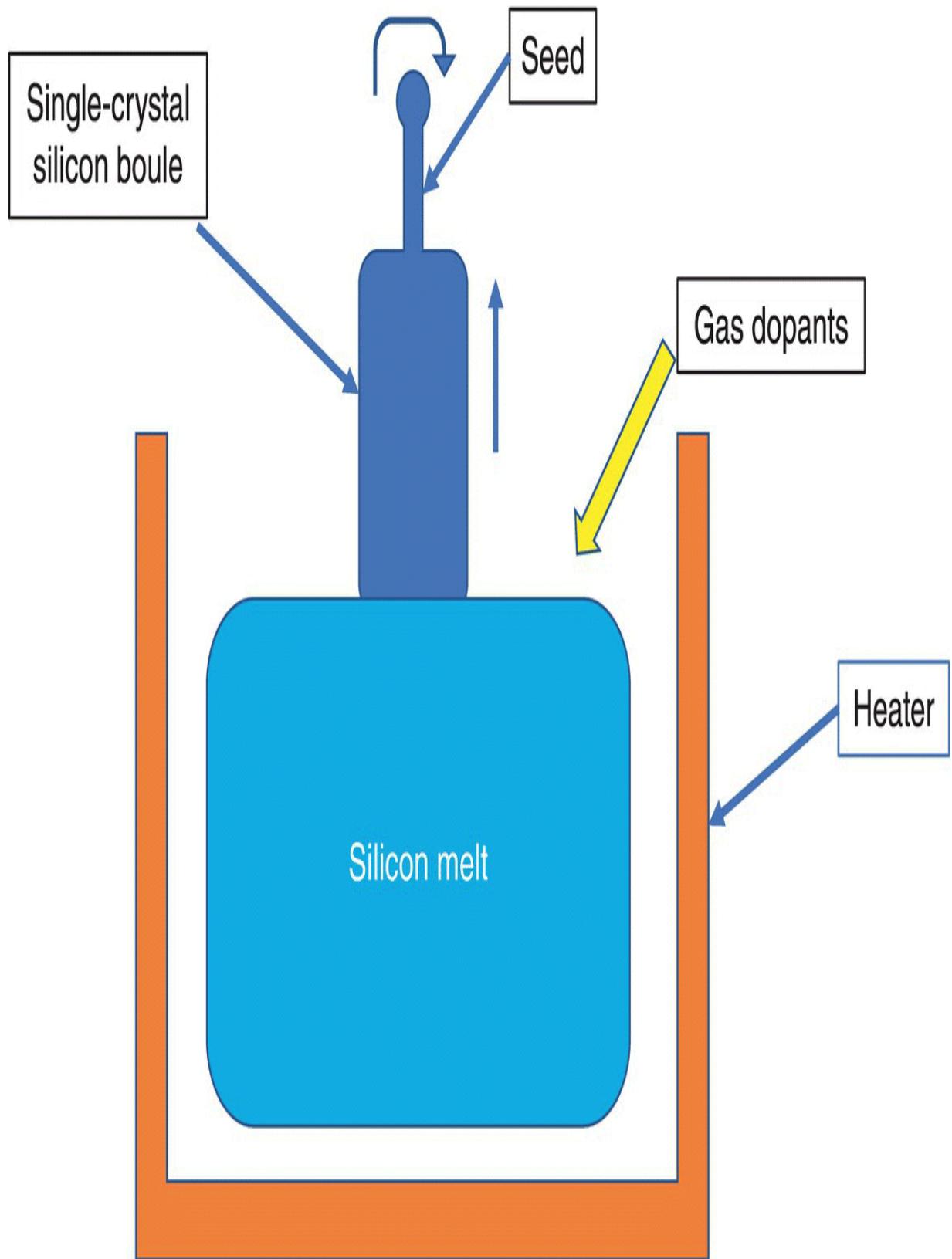

[Figure 10.1 Dr. Jan Czochalski developed a method of growing very pure and ...](#)

[Figure 10.2 The Czochralski method to grow a silicon boule. A seed pulls the...](#)

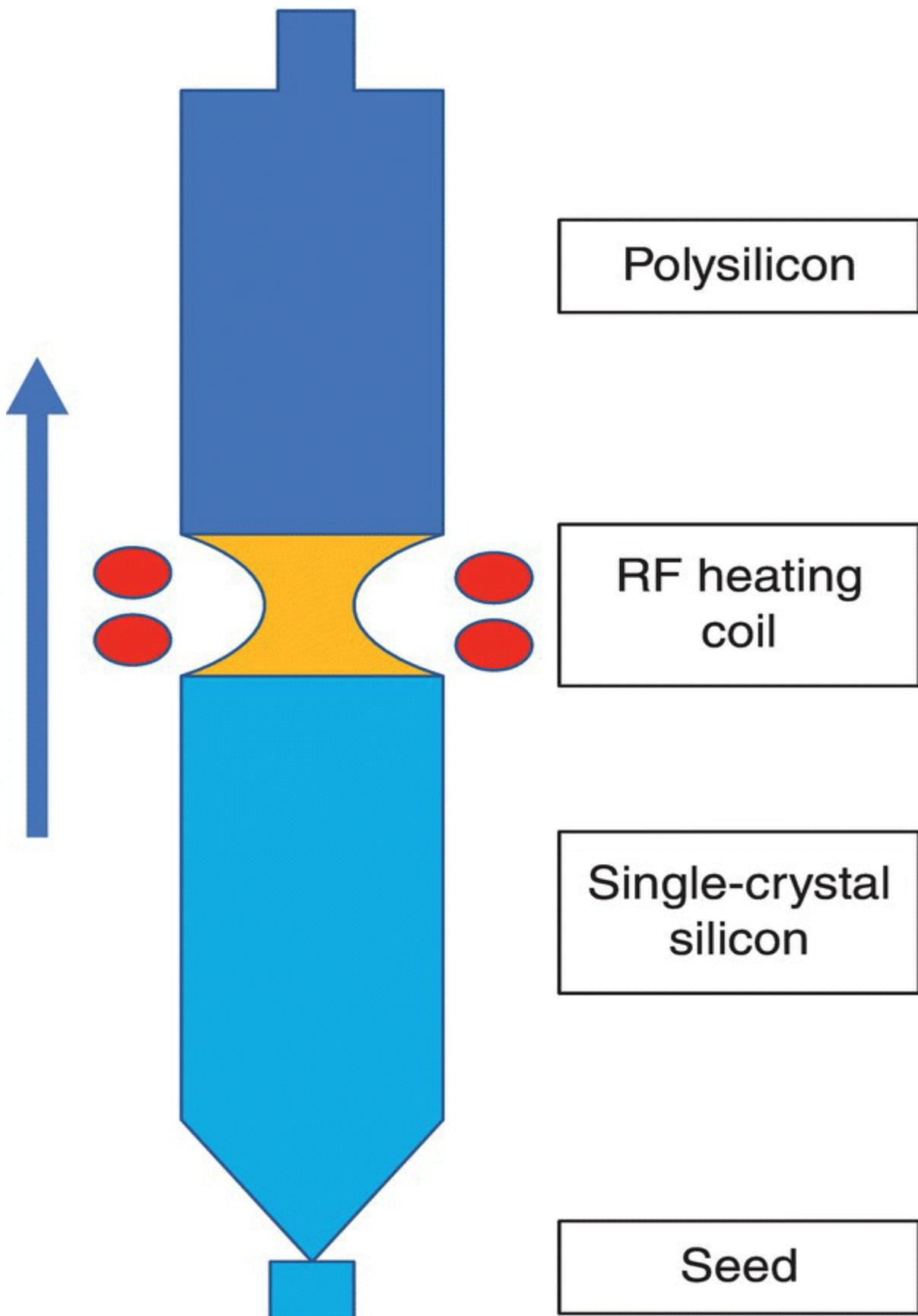

[Figure 10.3 In the float-zone growth method a heating coil moves up and down...](#)

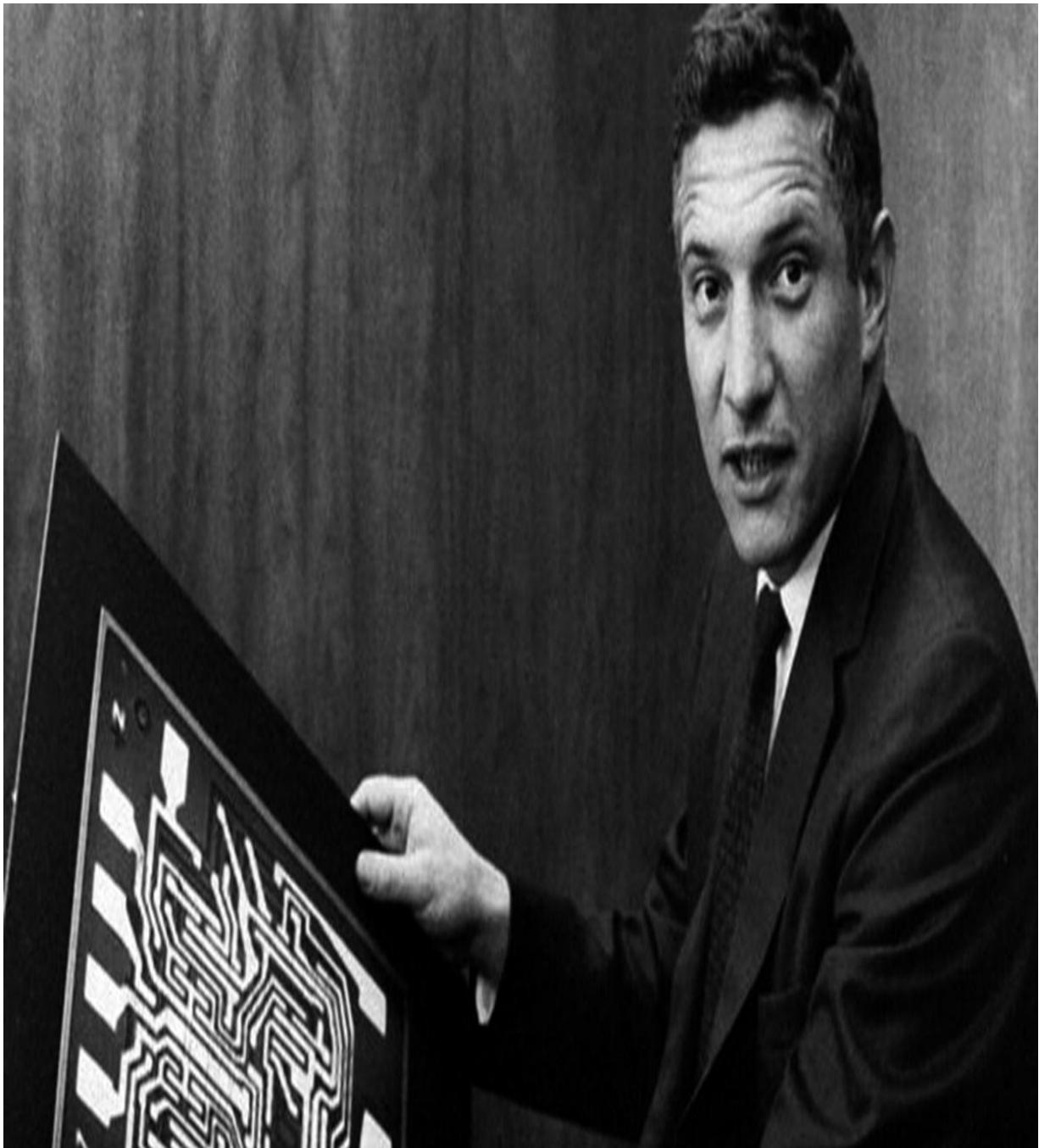

[Figure 10.4 Dr. Robert Noyce, observing the photographic process in a darkro...](#)

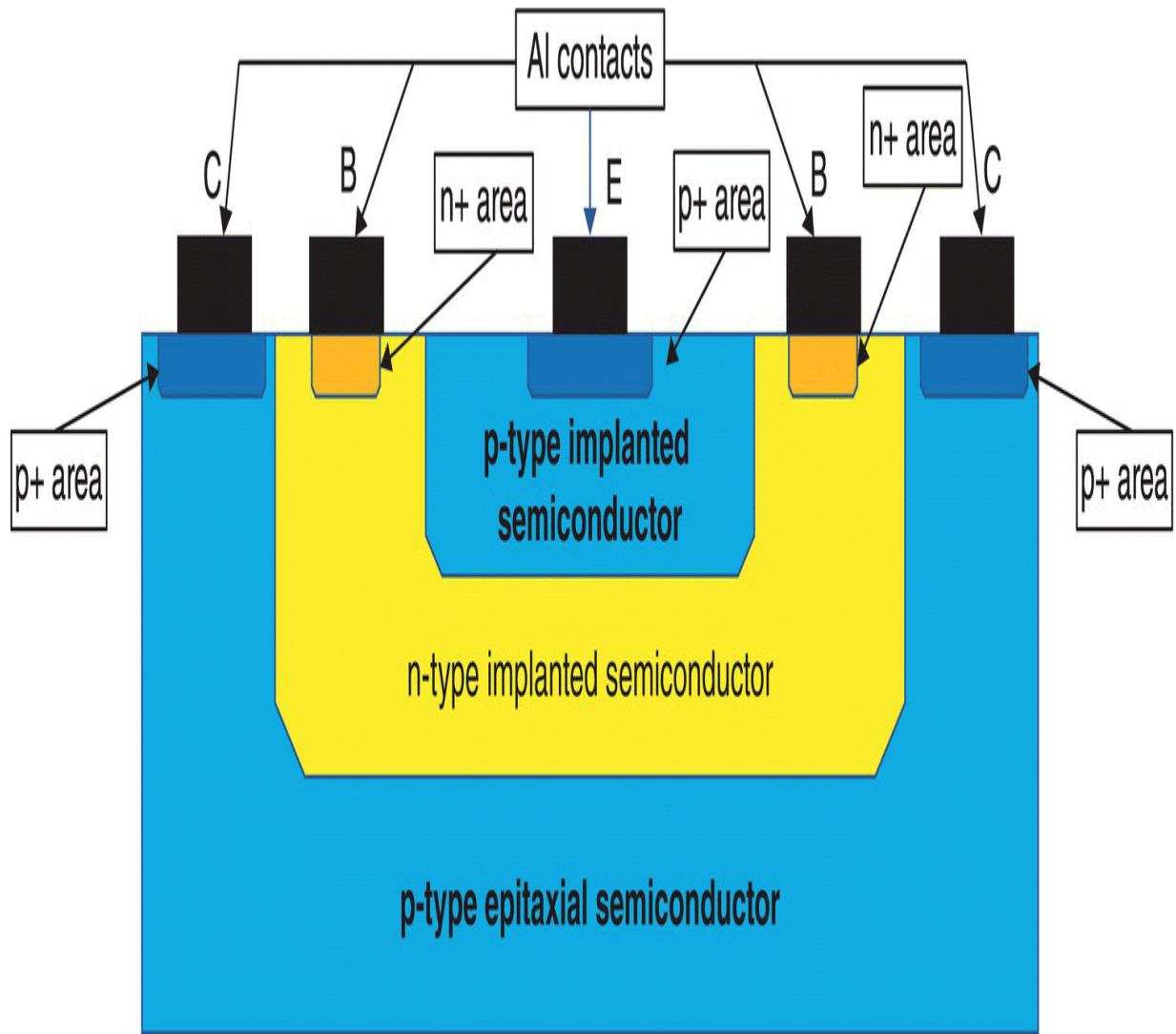

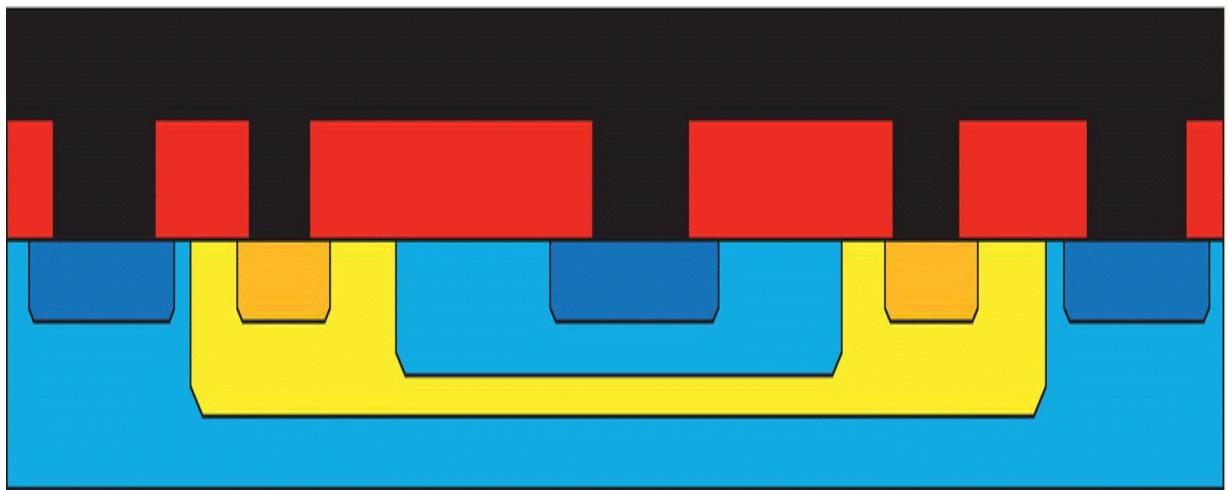

Figure 10.5 Cross-section of the planar transistor we want to build.

The p-t...

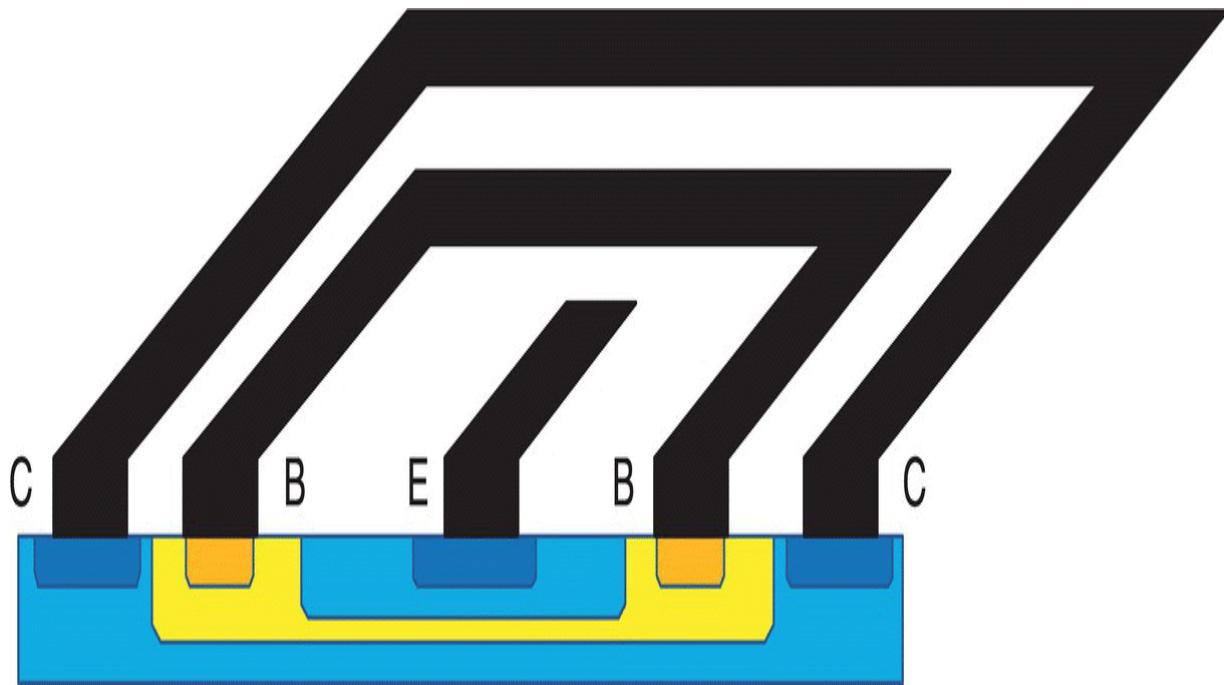

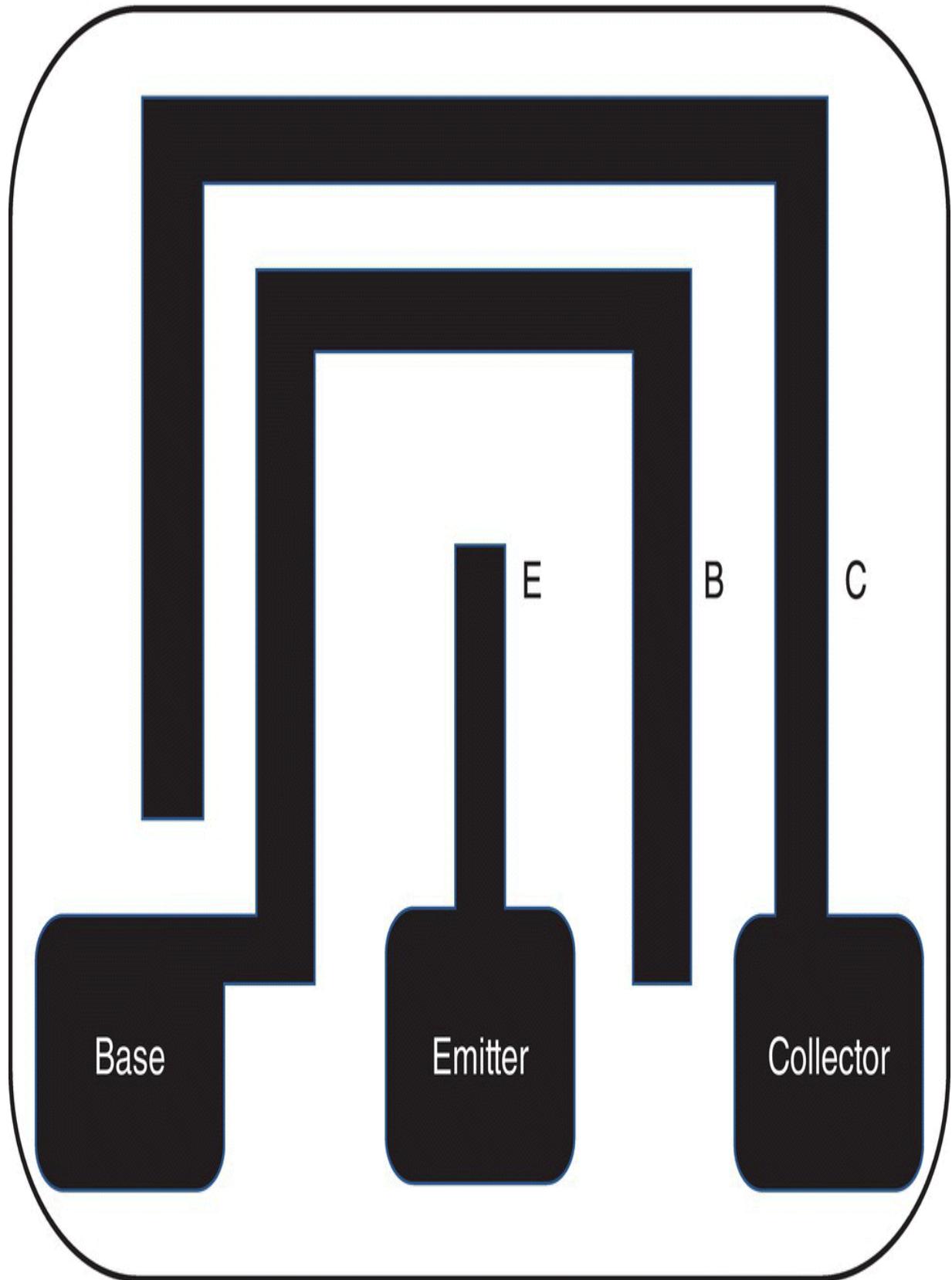

Figure 10.6 Top view of the aluminum lines connecting the different silicon ...

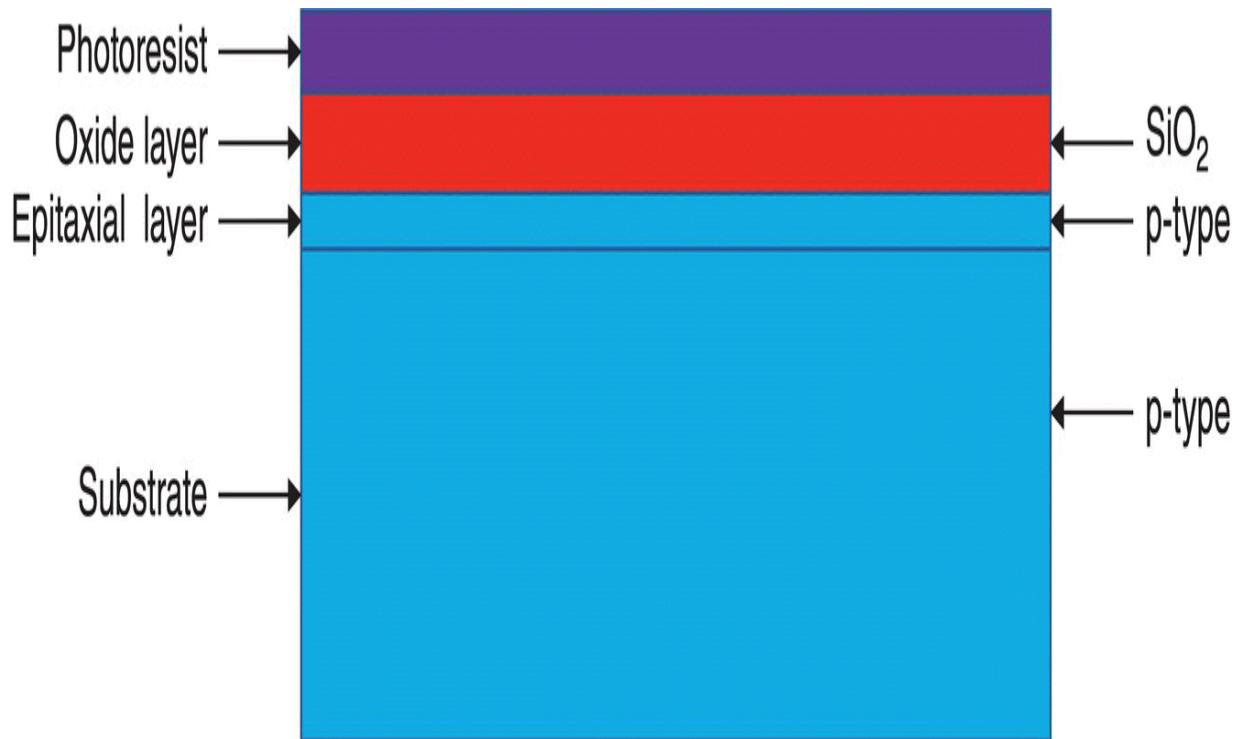

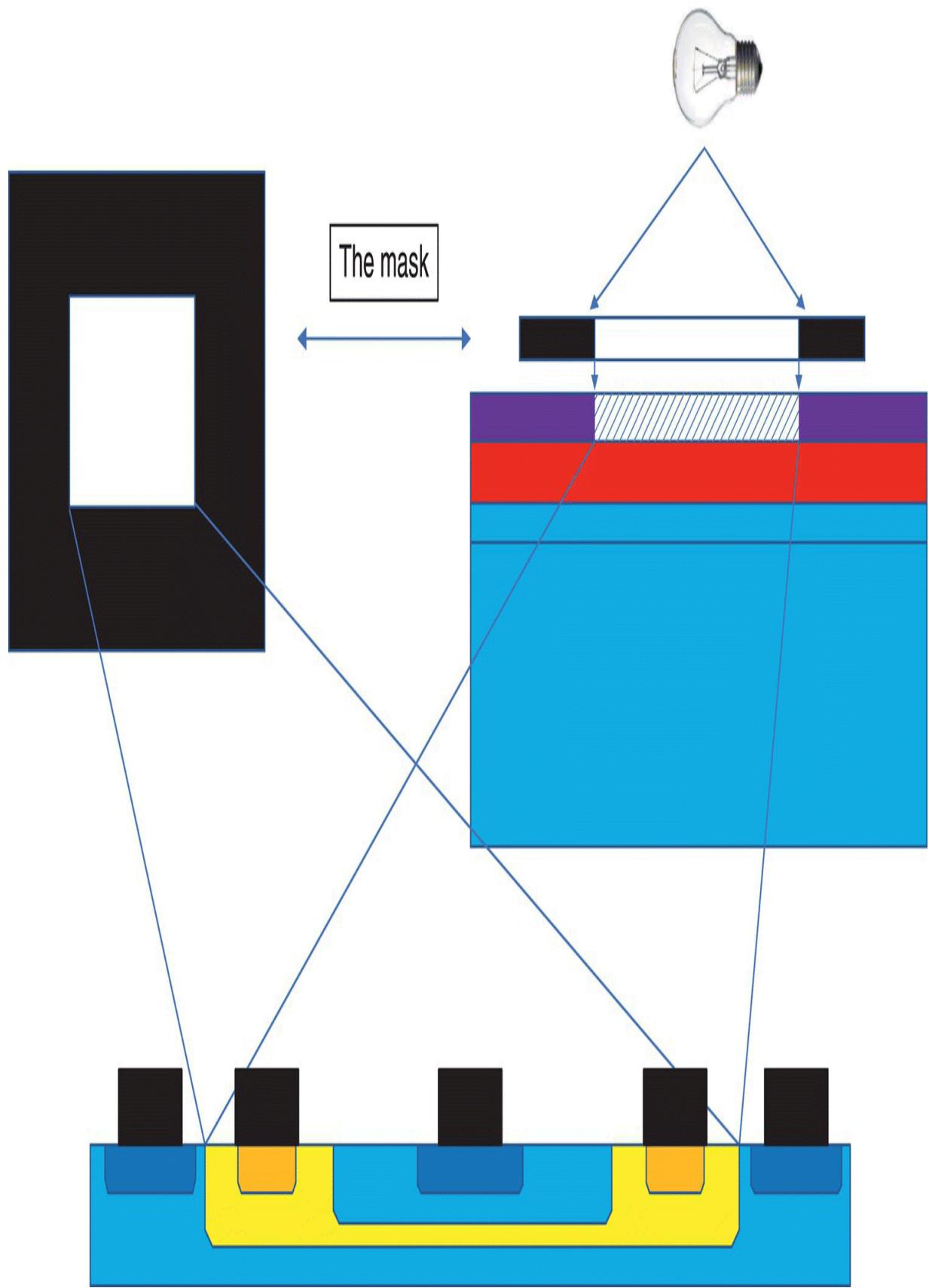

Figure 10.7 First four steps of transistor fabrication: the epitaxial layer ...

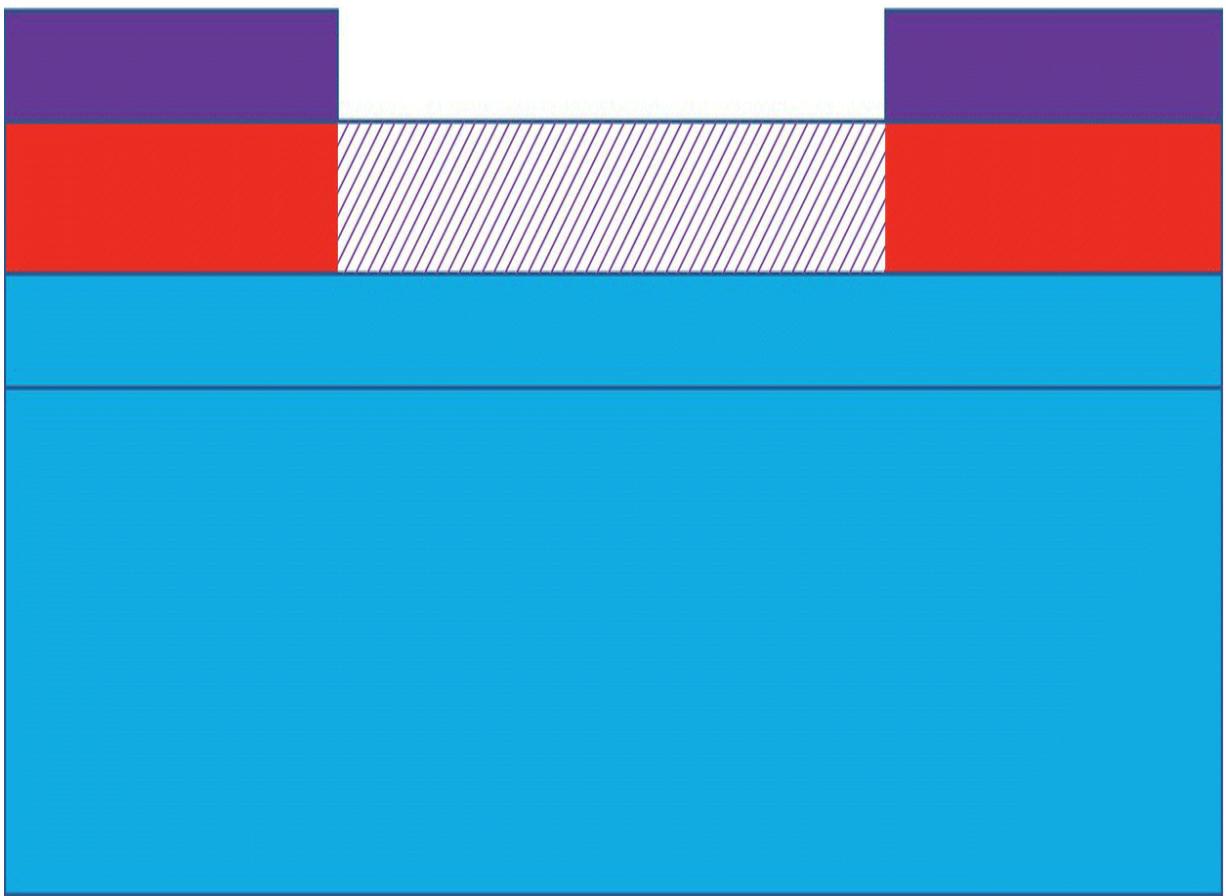

Figure 10.8 The next step is to photographically illuminate the portion of t...

Figure 10.9 The semiconductor after the illuminated part of the photoresist ...

Figure 10.10 We remove the oxide with ammonium fluoride and the excess photo...

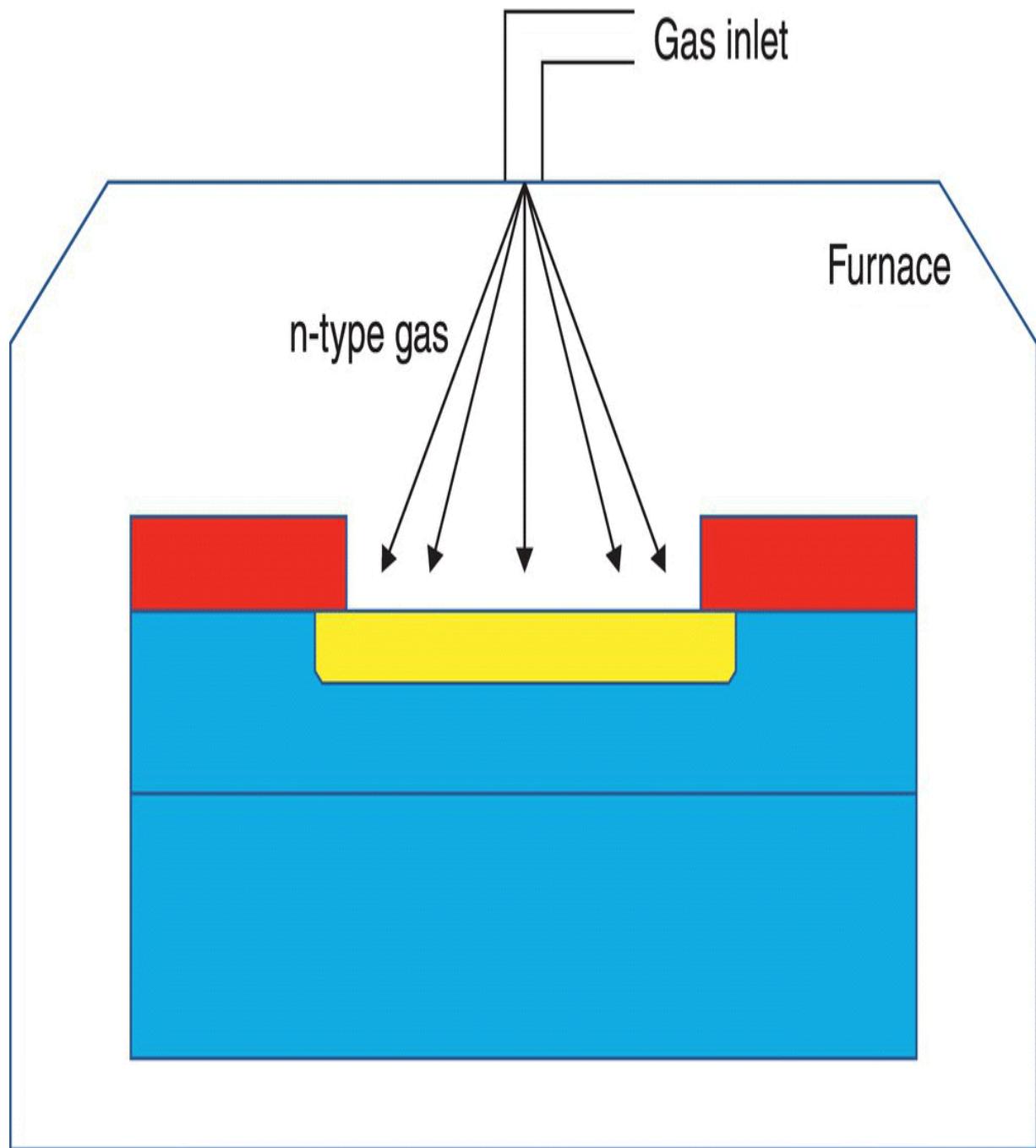

Figure 10.11 The semiconductor, with the desired oxide removed, is located i...

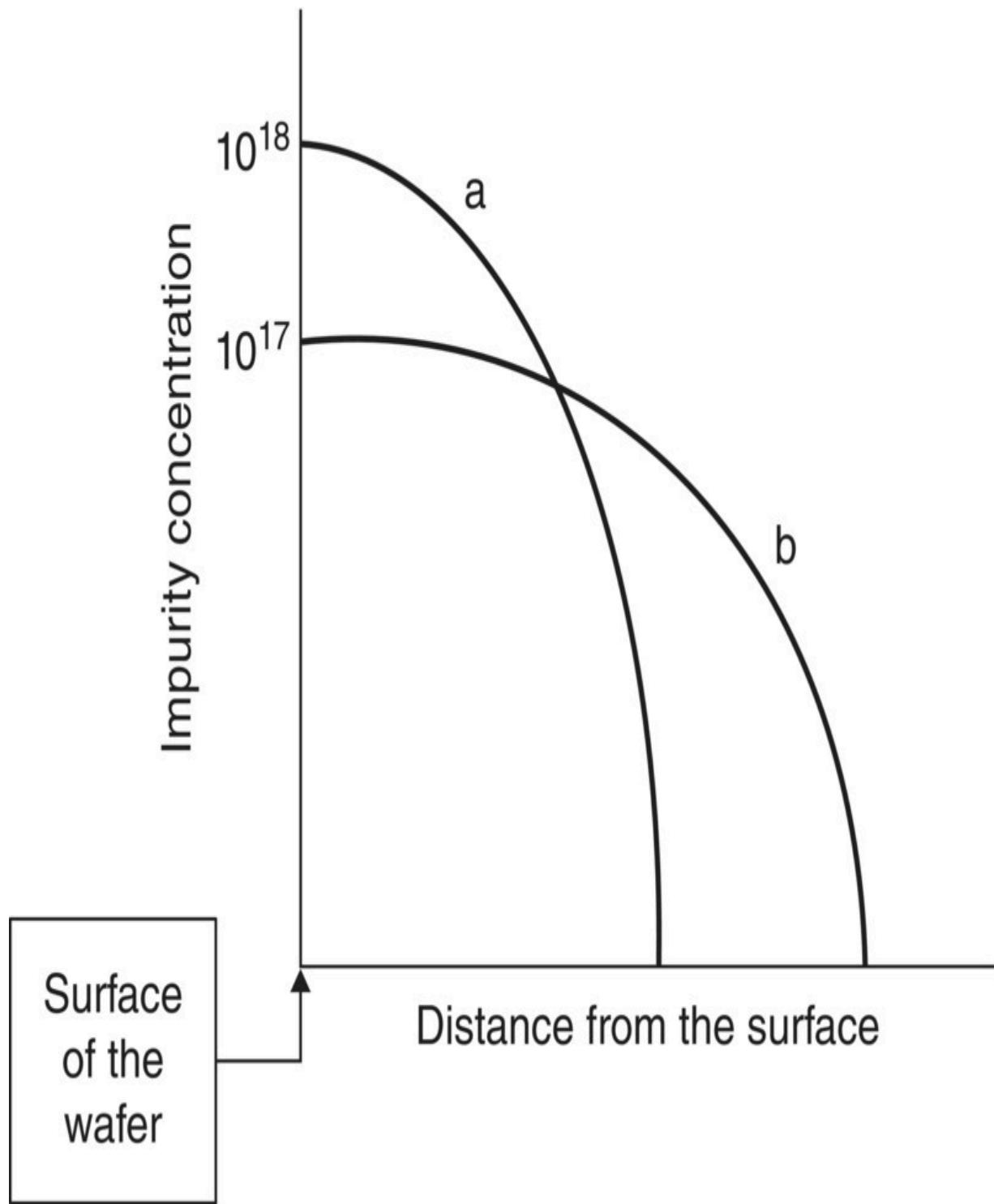

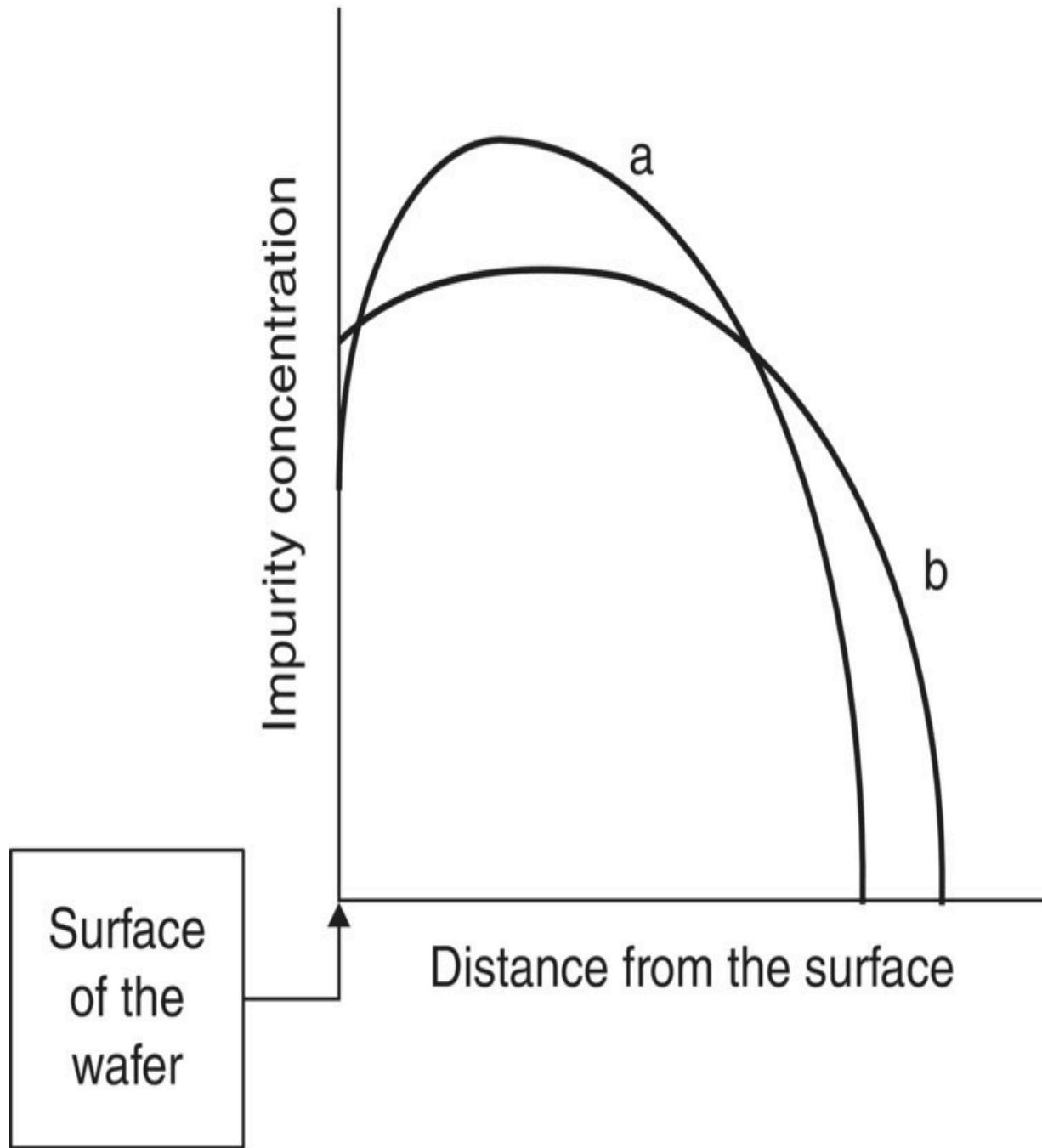

Figure 10.12 The impurity concentration at the end of the deposition (curve a...

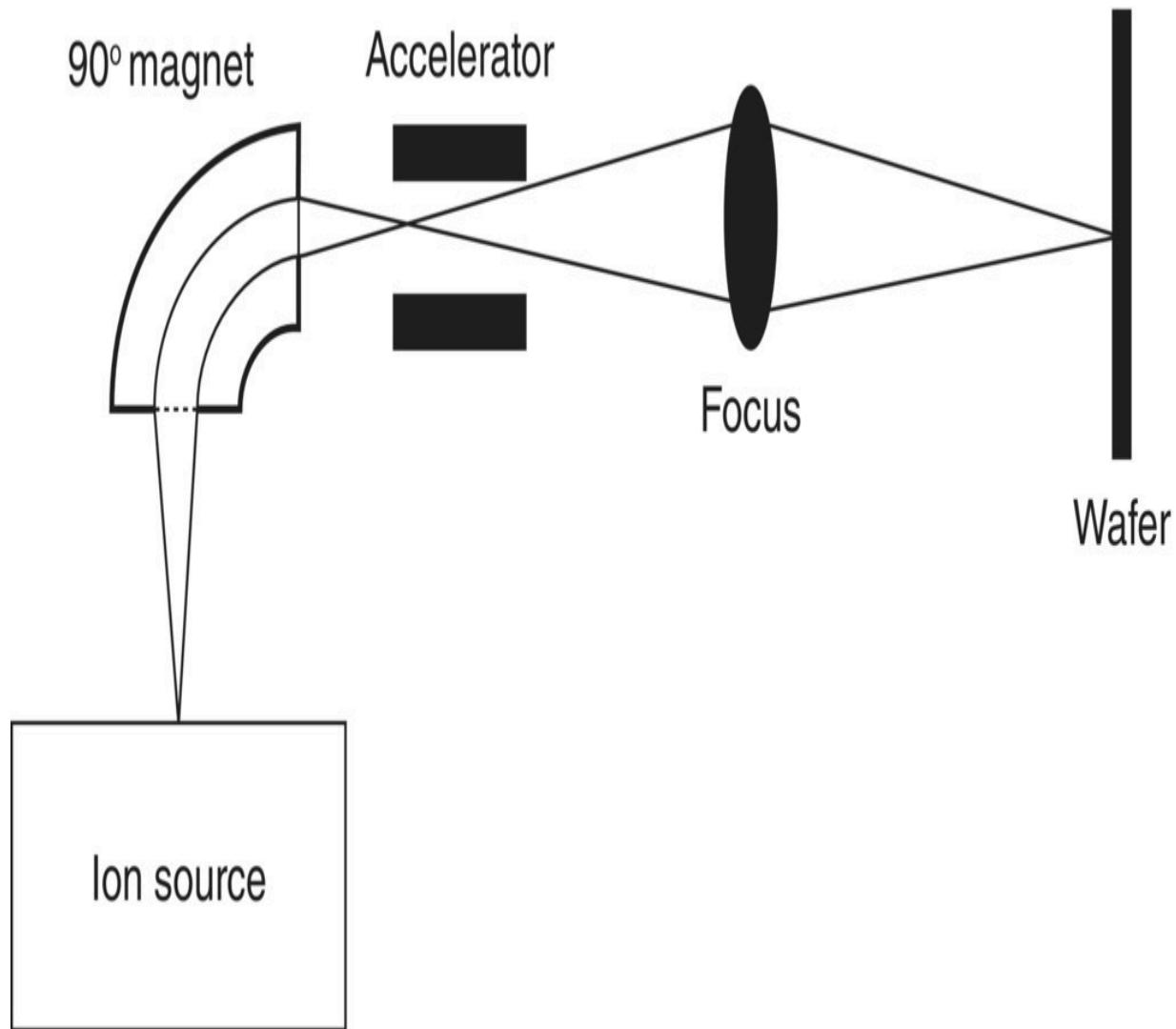

Figure 10.13 An ion implanter consists of an ion source, a magnet to separat...

Figure 10.14 The impurity concentration in an implanted wafer as a function ...

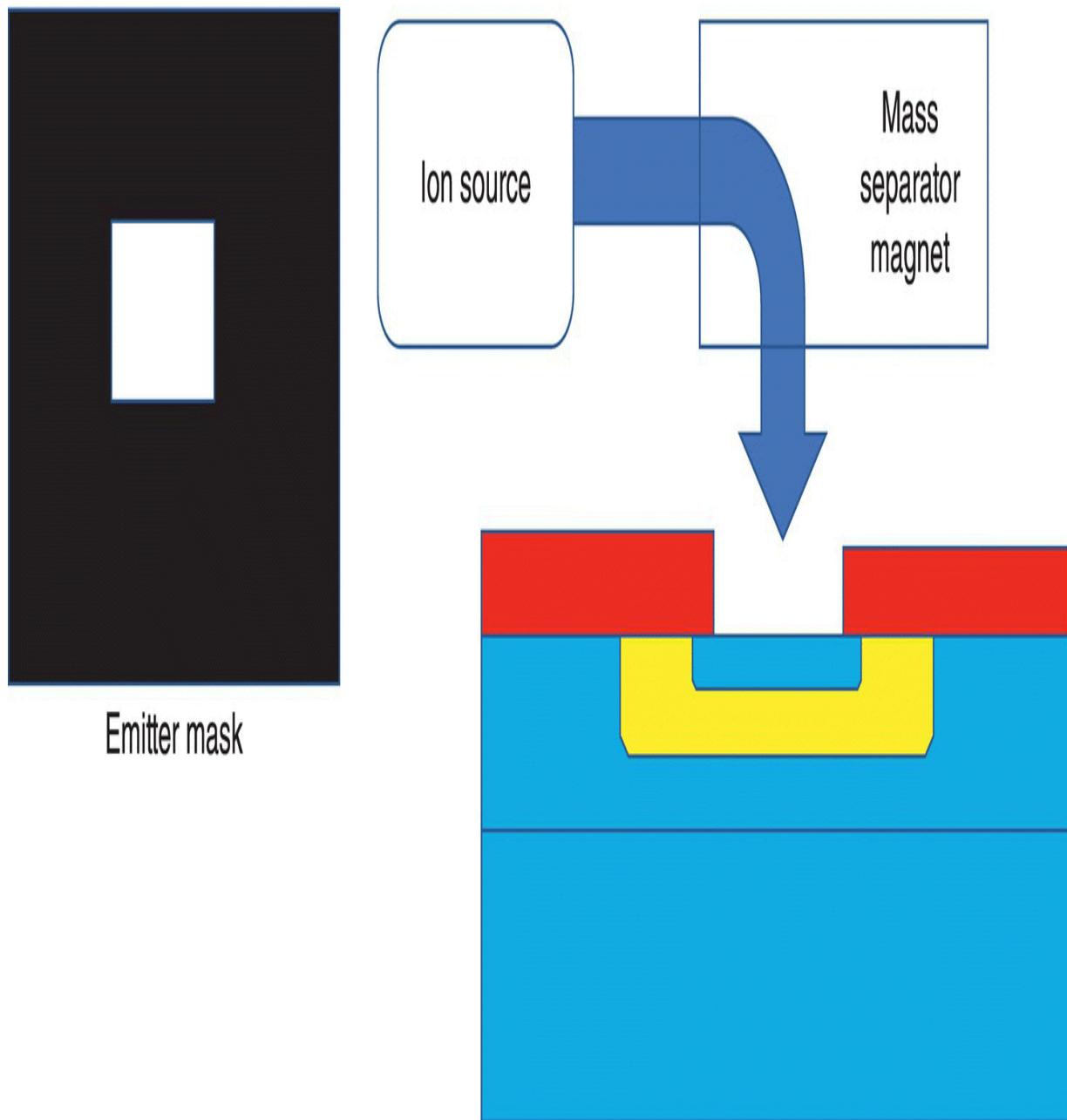

Figure 10.15 Using an ion implanter we fabricate the emitter region using a ...

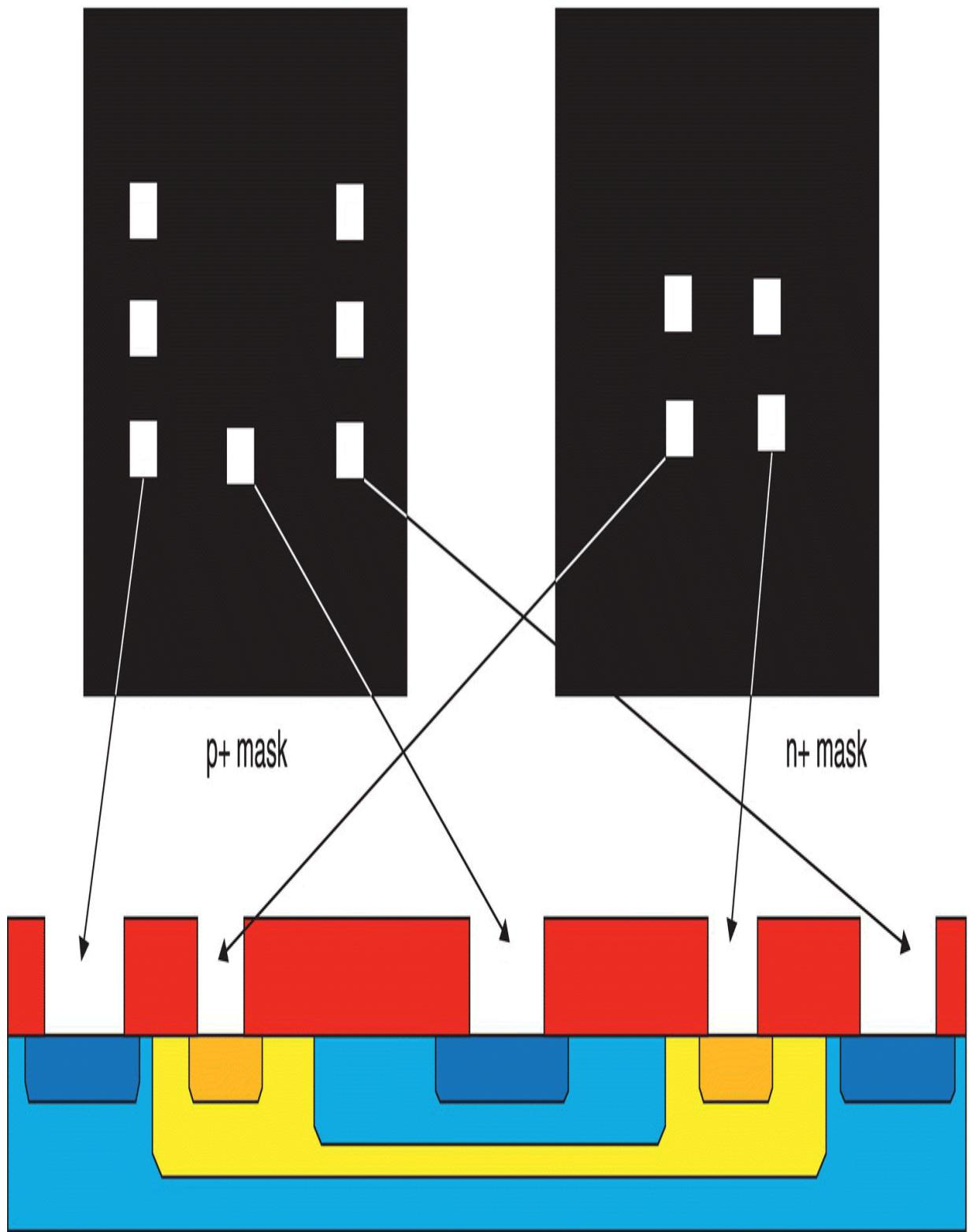

Figure 10.16 Mask used to create the p+ (left) and n+ (right) regions.

Figure 10.17 A wafer covered with a metal layer makes contact with all the n...

Figure 10.18 The aluminum mask connects each contact on the wafer to areas w...

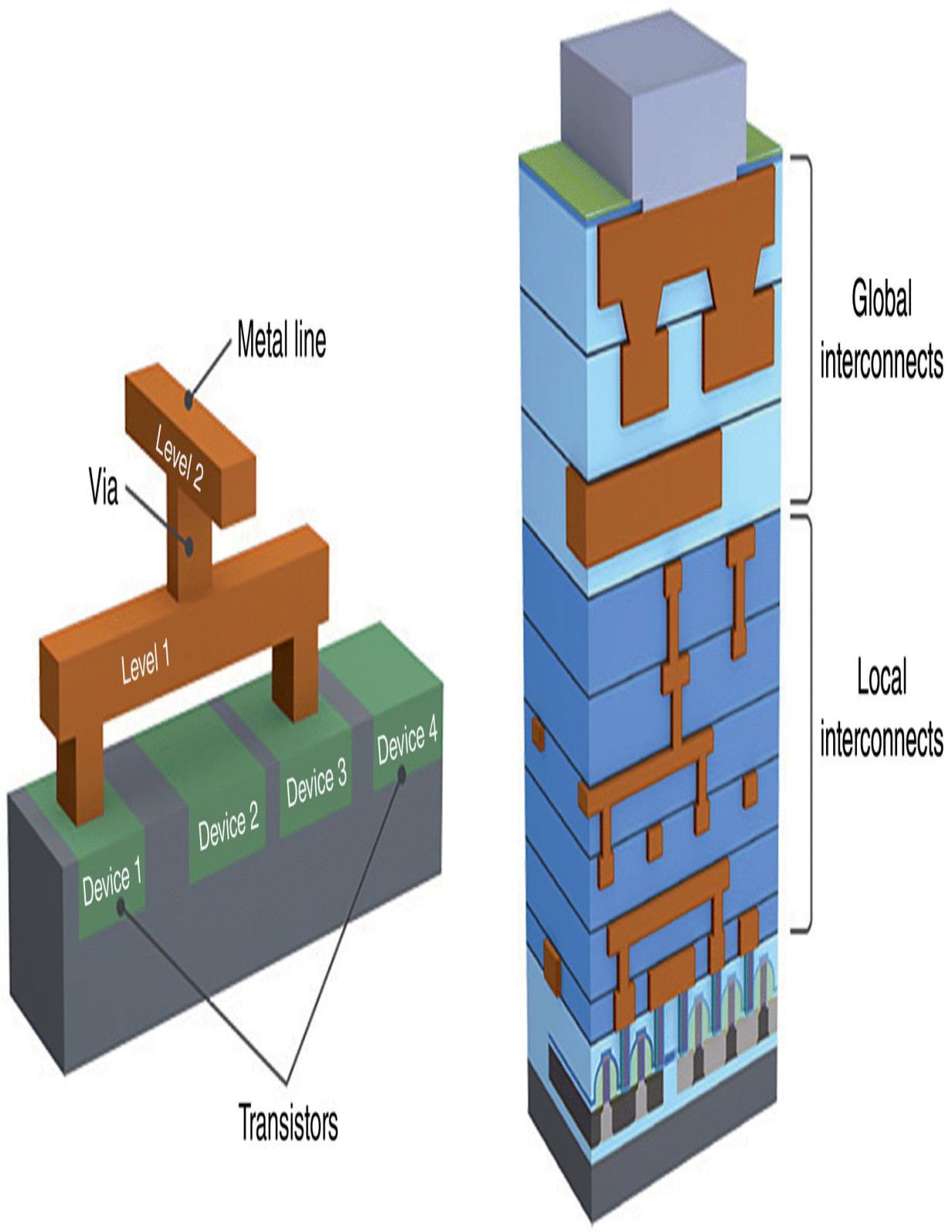

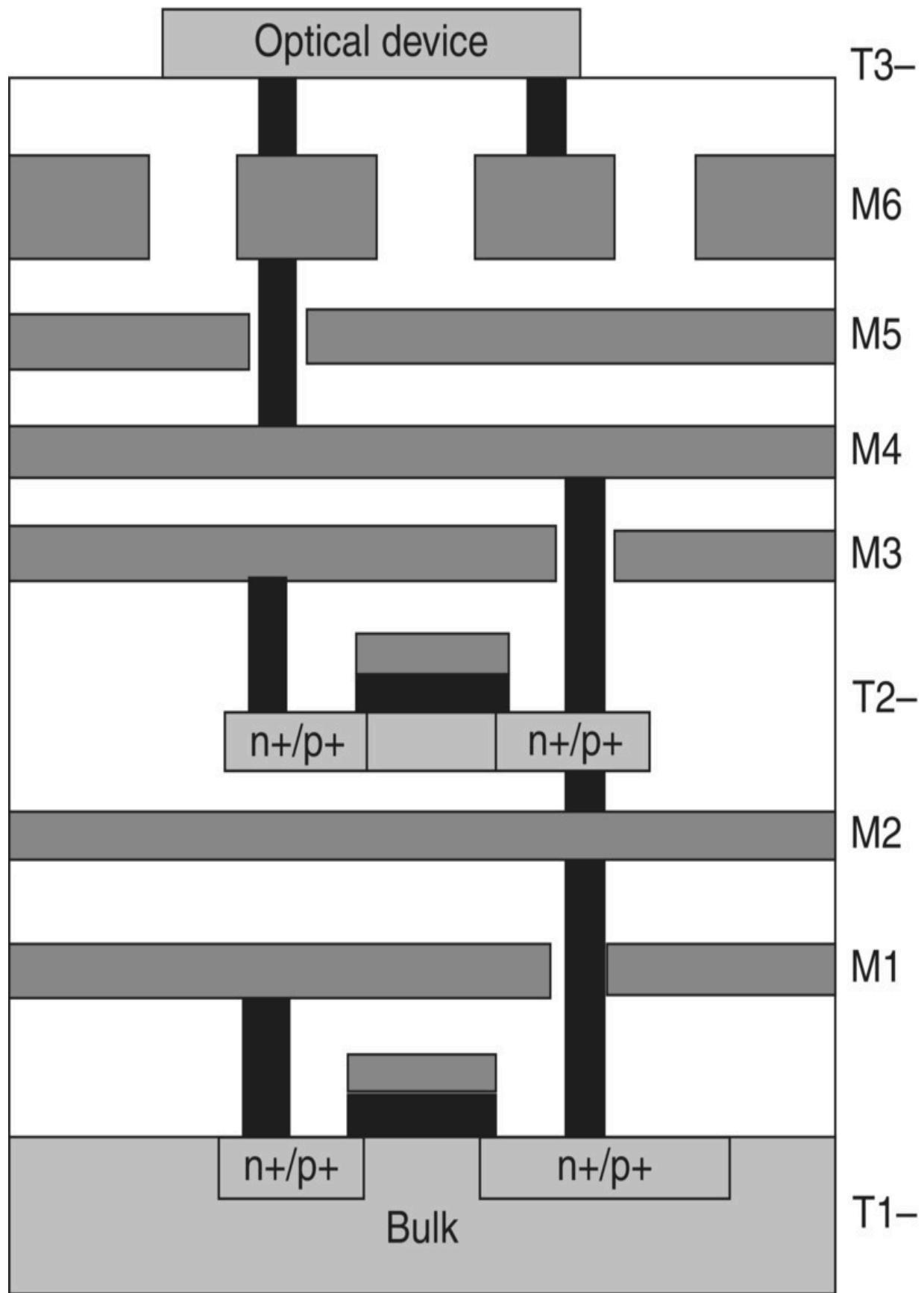

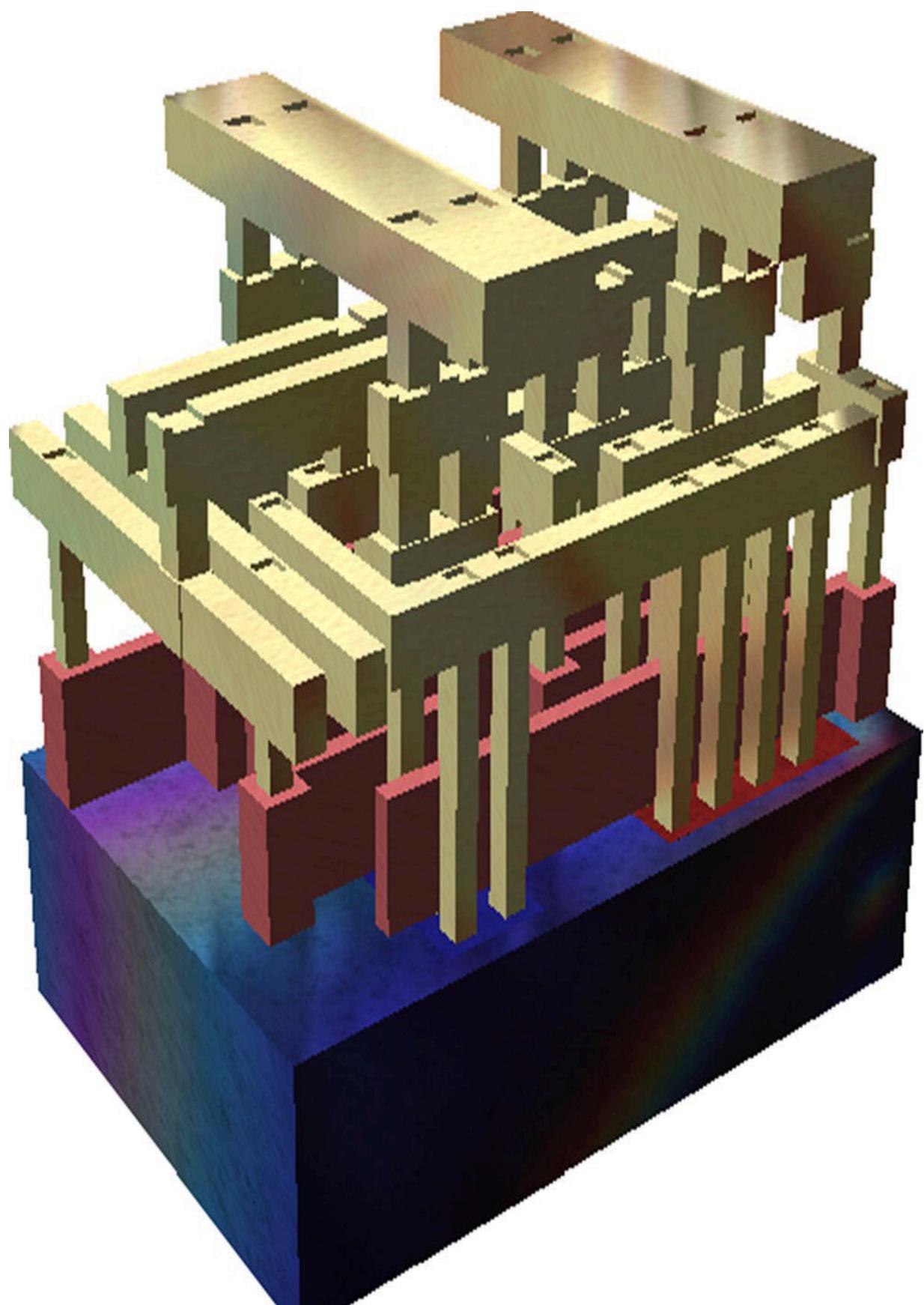

Figure 10.19 Modern electronic integrated circuits use multiple levels of in...

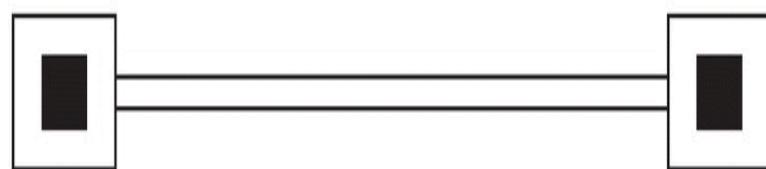

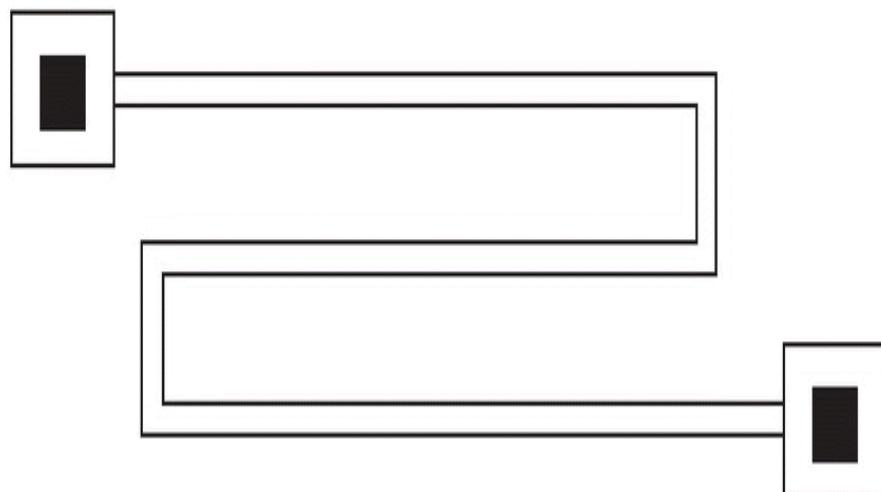

[Figure 10.20 Fabrication of a resistor. Cross-section of an integrated resistor...](#)

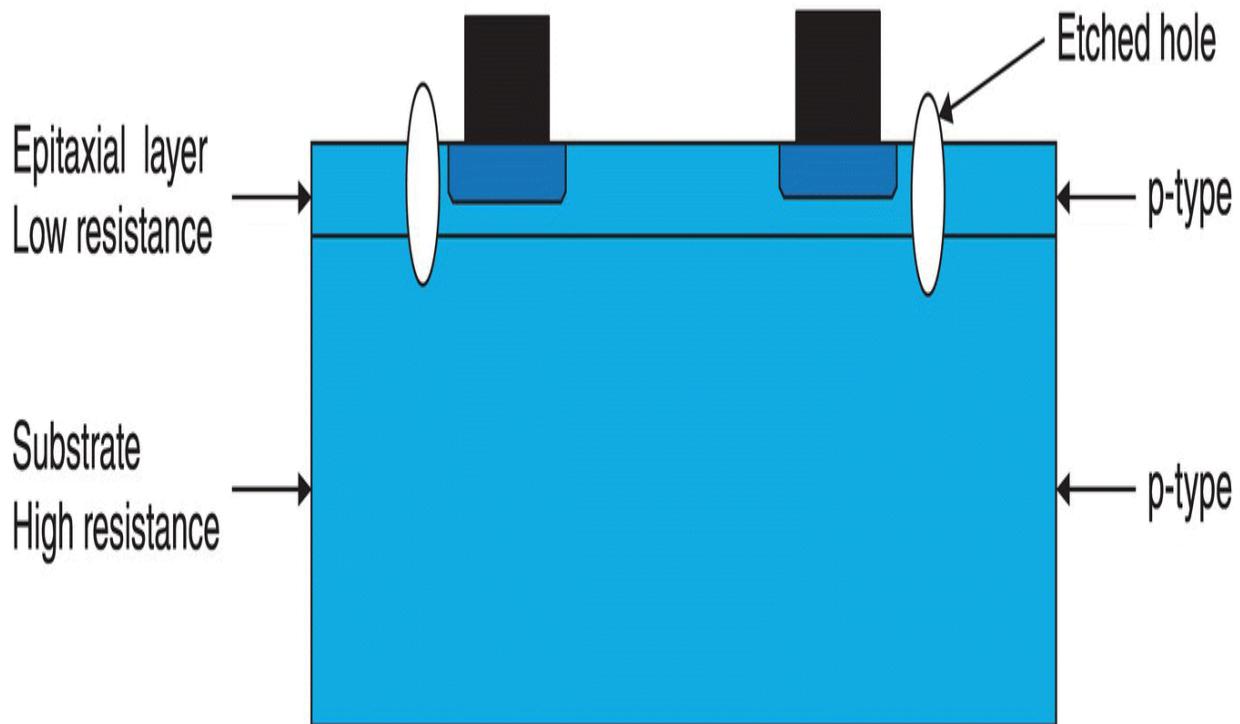

[Figure 10.21 Another way to fabricate a resistor is to use the epitaxial layer...](#)

[Figure 10.22 Capacitors are fabricated using the same techniques as MOSFETs ...](#)

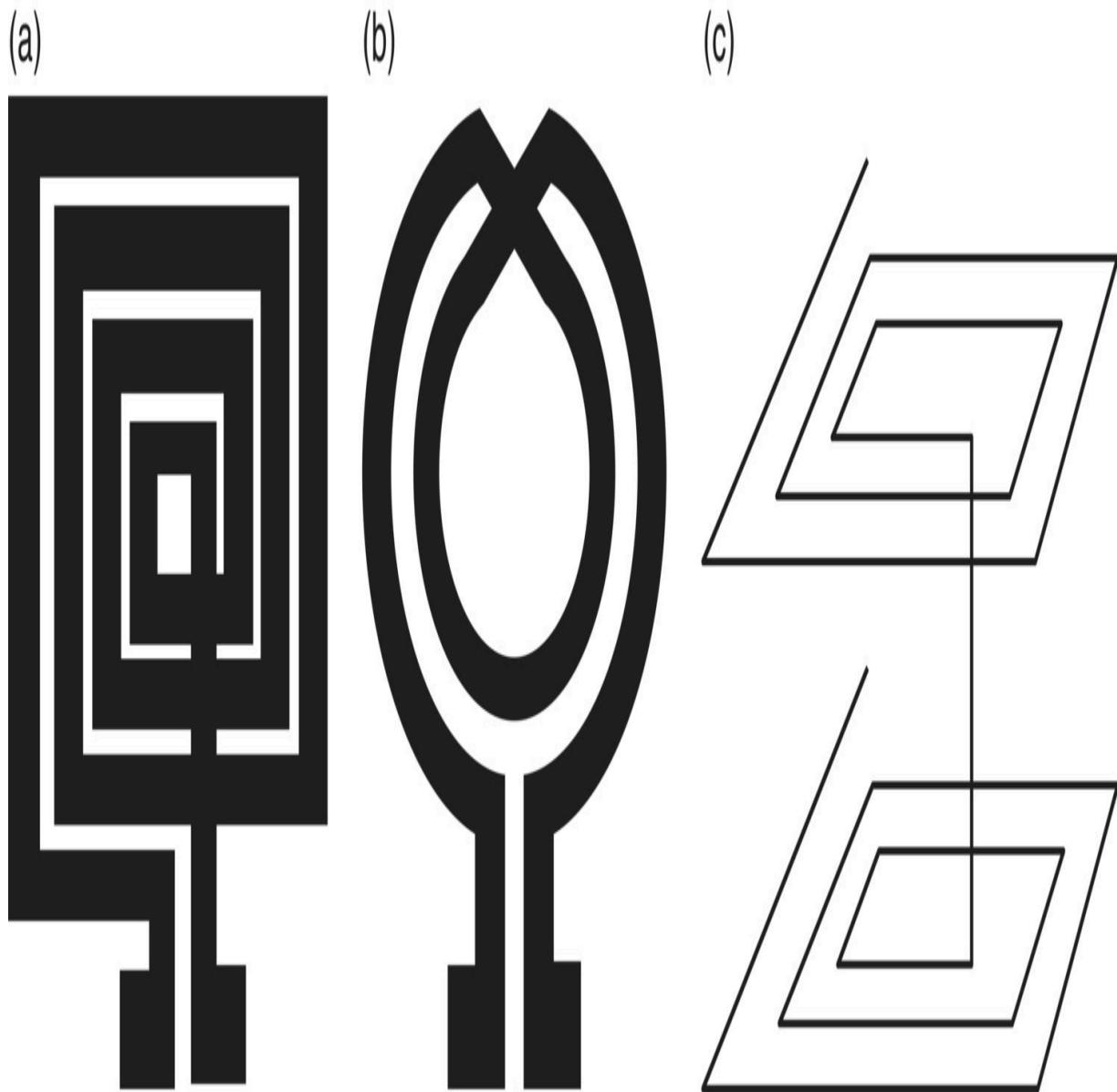

[Figure 10.23 Spiral inductors can also be fabricated in a spiral form, as a ...](#)

[Figure 10.24 A fully processed wafer.](#)

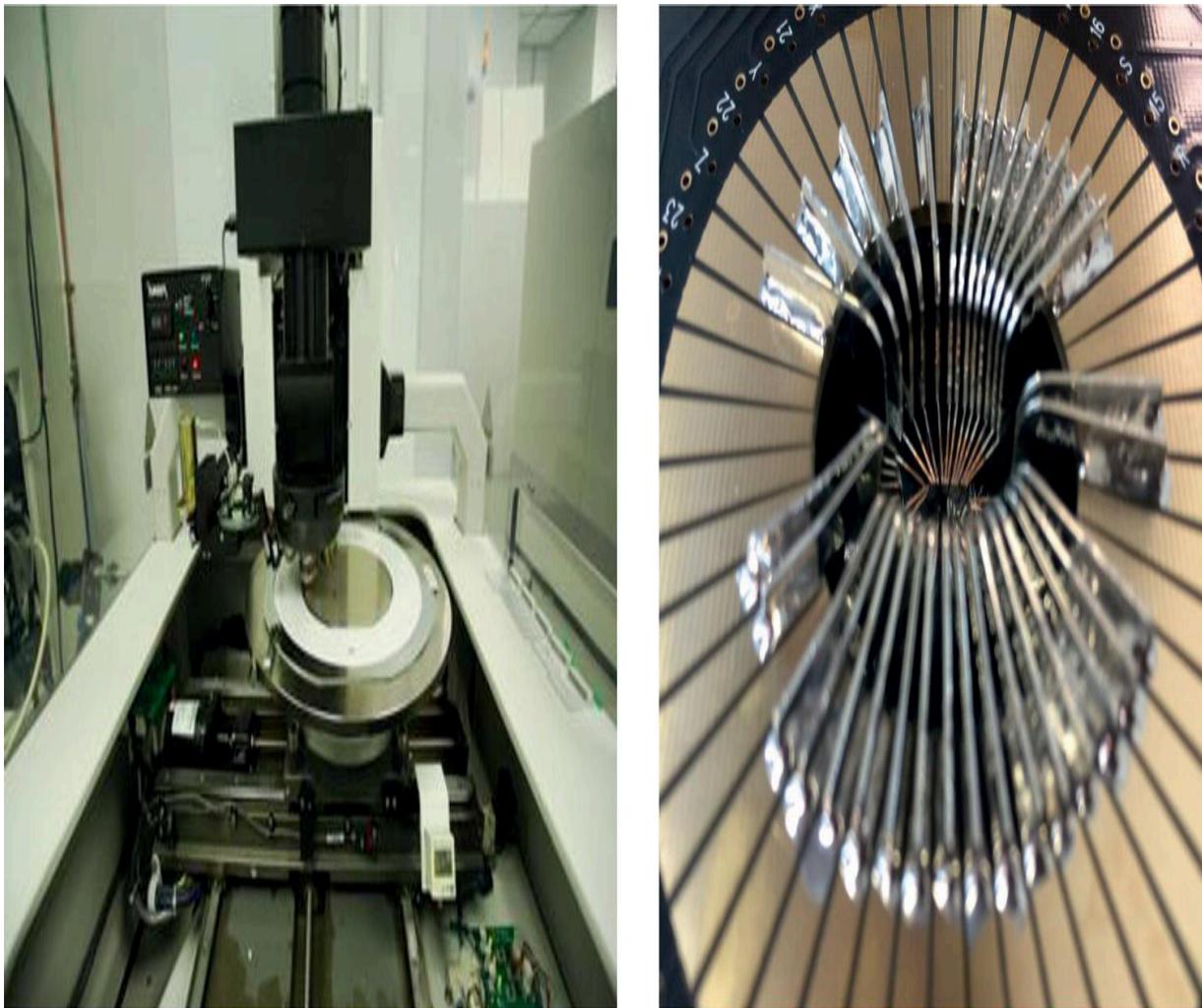

[Figure 10.25 A modern probe tester \(left\) and the very thin conductive probe...](#)

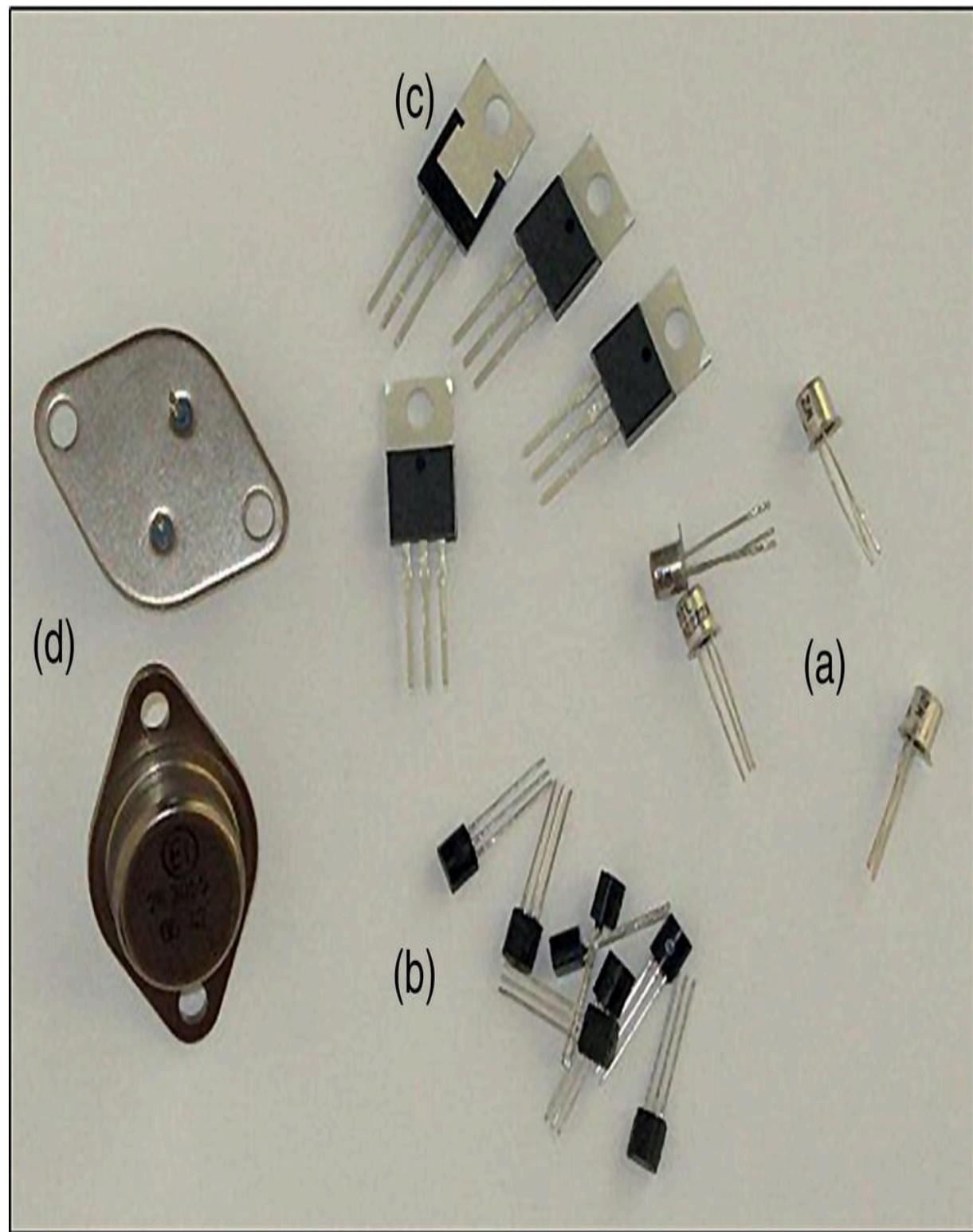

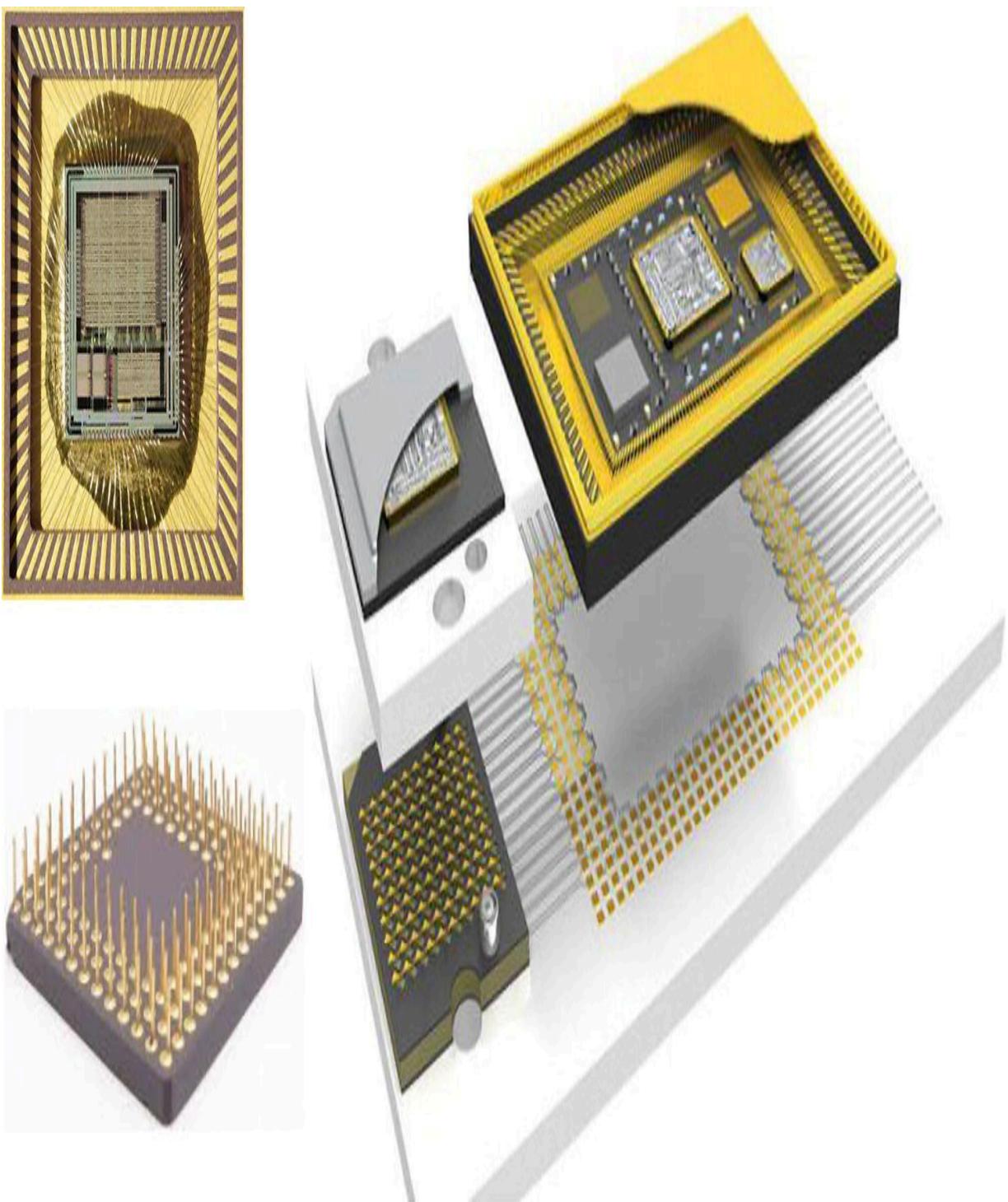

[Figure 10.26 Single electronic device packaging with the three inputs for emphasis...](#)

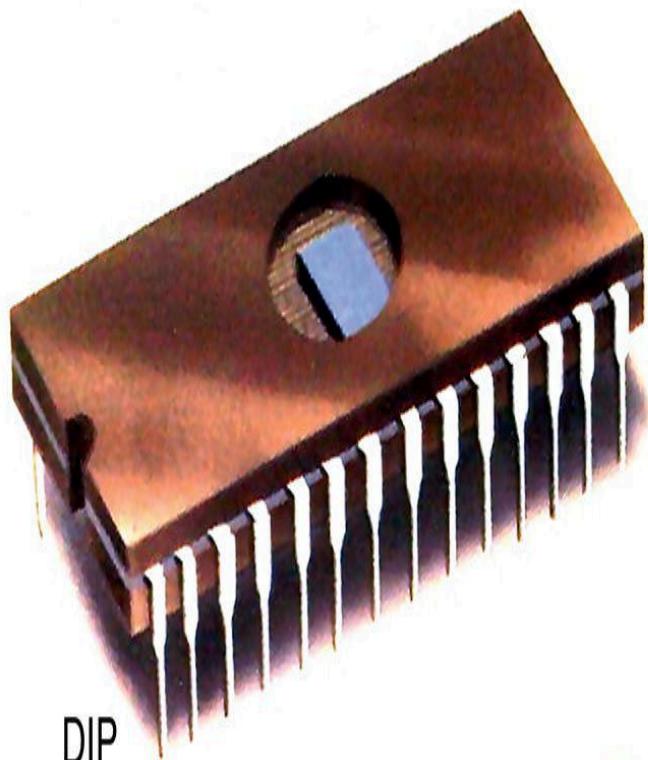

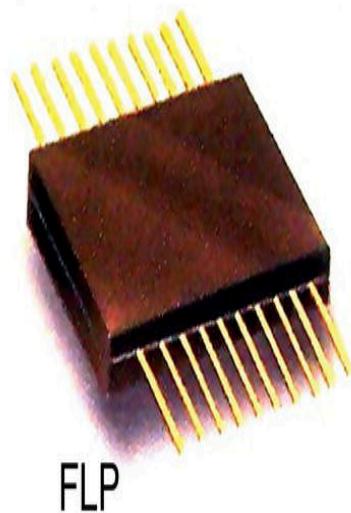

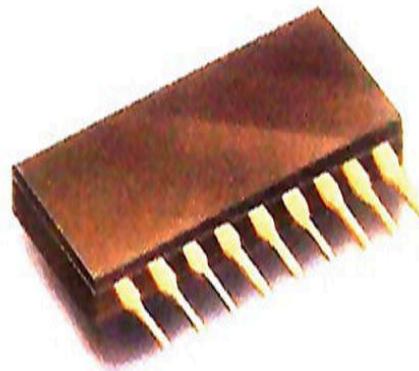

[Figure 10.27 In a flat package the chip sits in the middle and is bonded to ...](#)

[Figure 10.28 Packaging for devices with many inputs and outputs.](#)

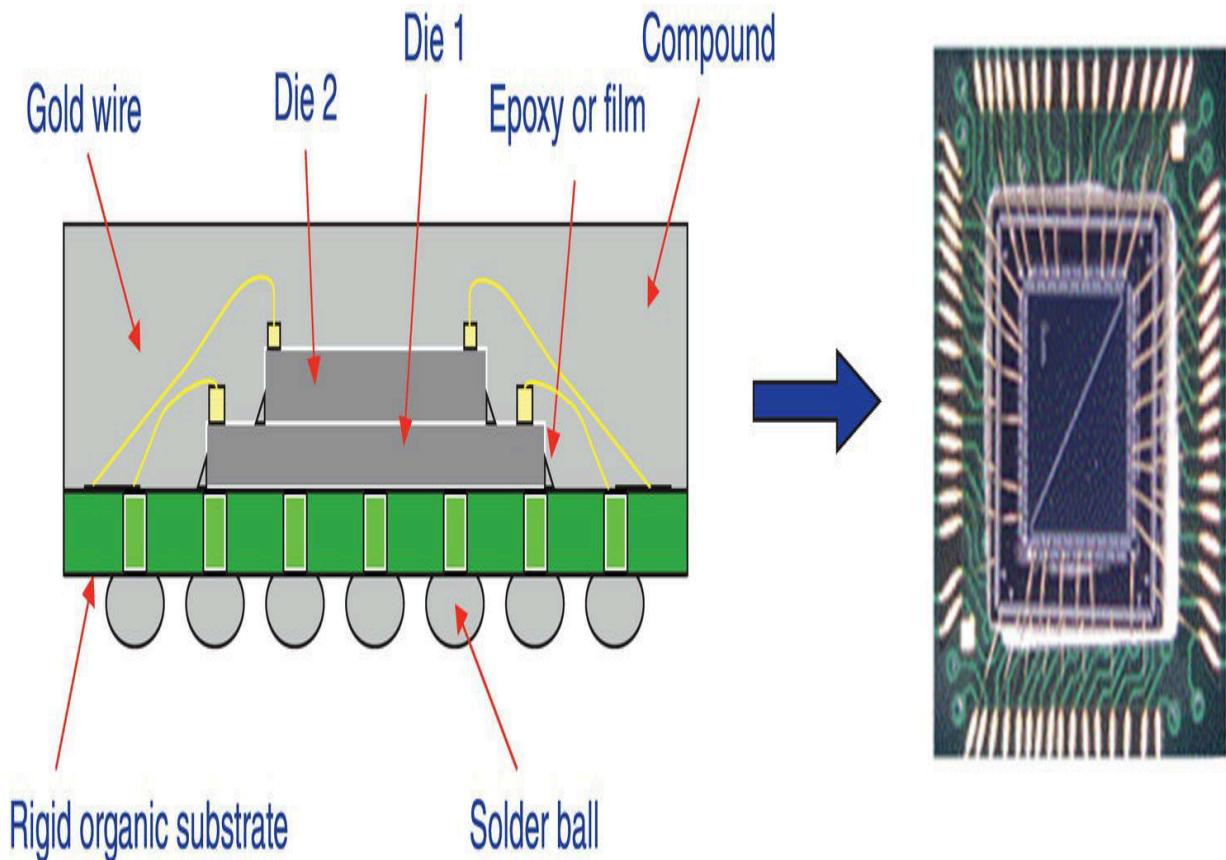

[Figure 10.29 A sketch of the flip bonding process \(left\) and a completed package...](#)

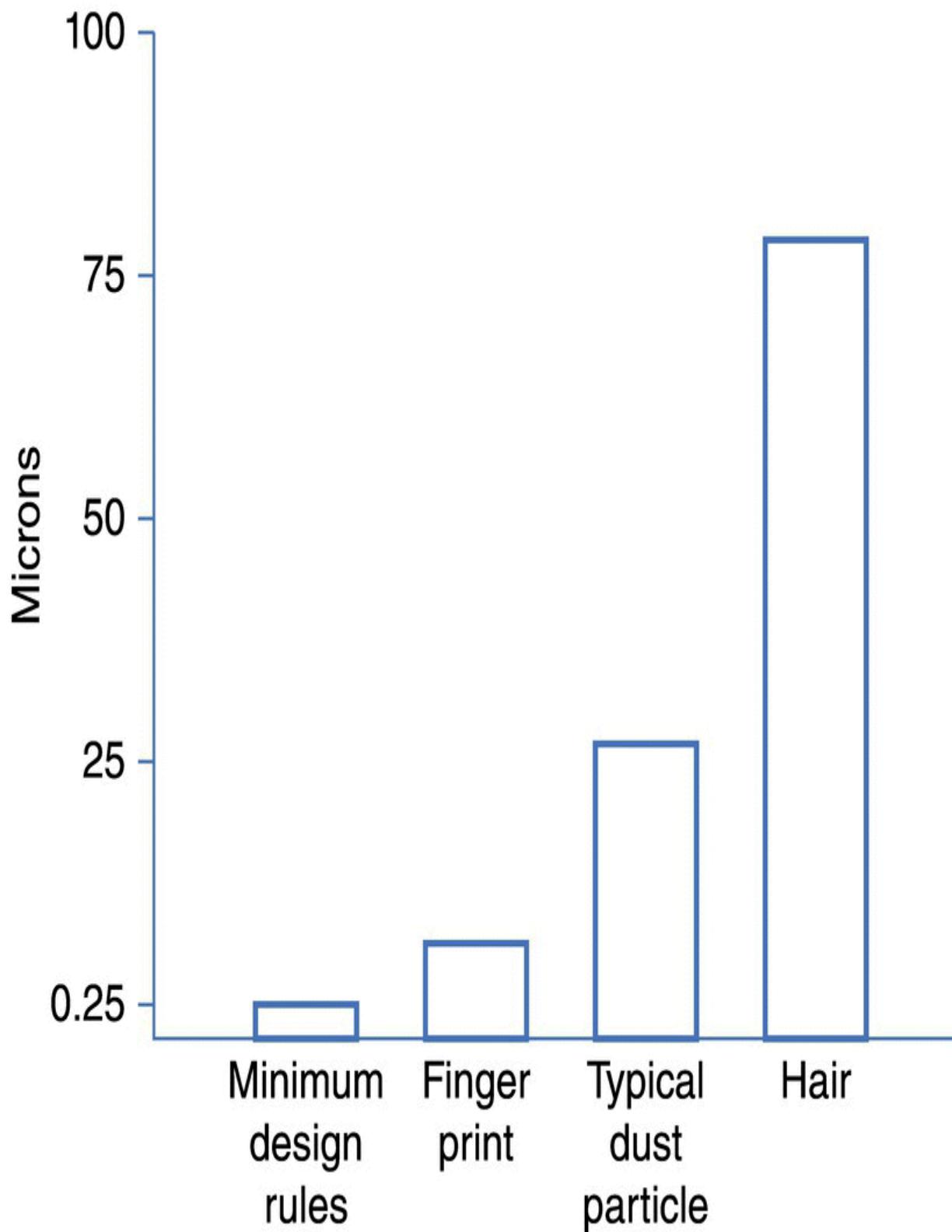

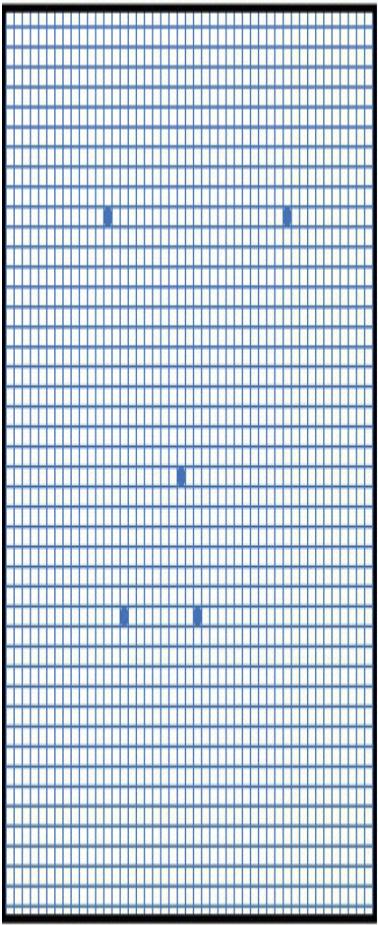

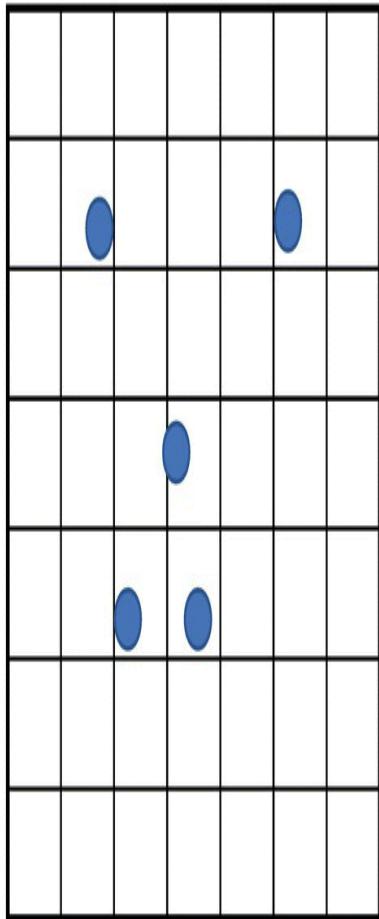

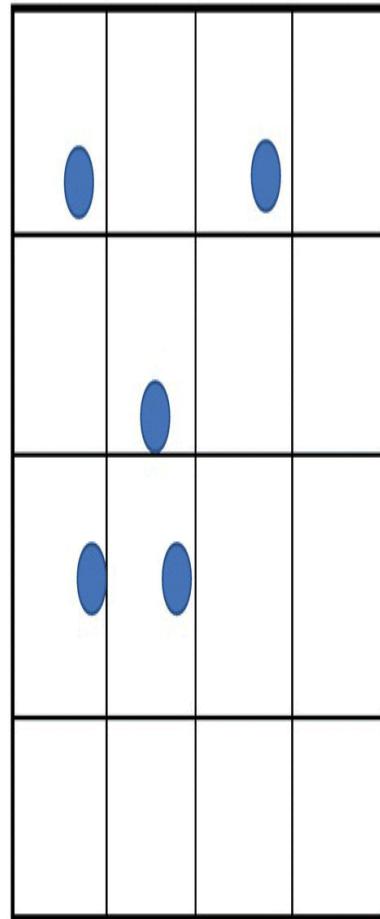

[Figure 10.30 The minimum design rules compared to typical impurities that cause...](#)

[Figure 10.31 Effect on yield of defects as a function of chip size.](#)

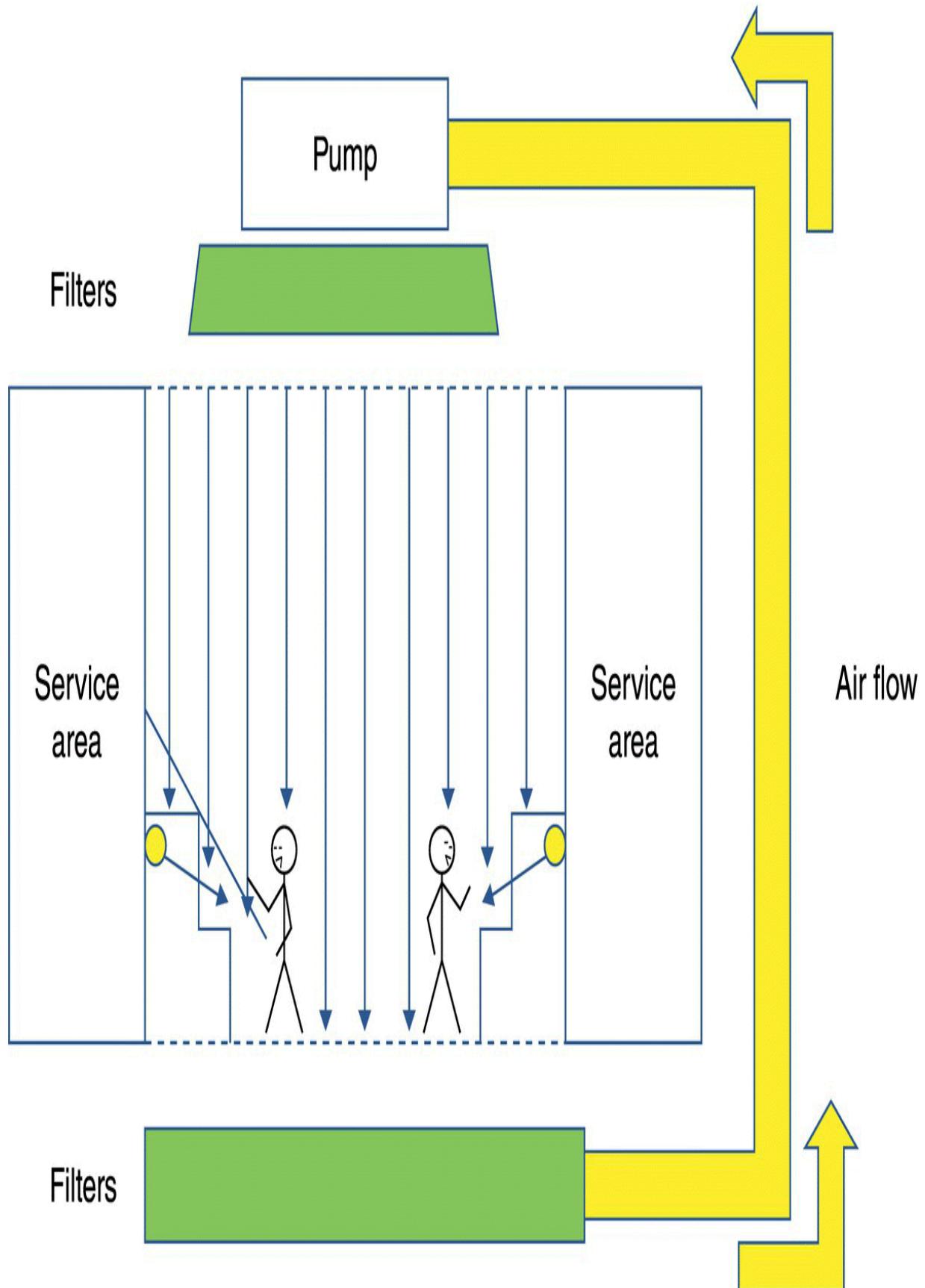

[Figure 10.32 A typical laminar flow clean room keeps the air flow vertically...](#)

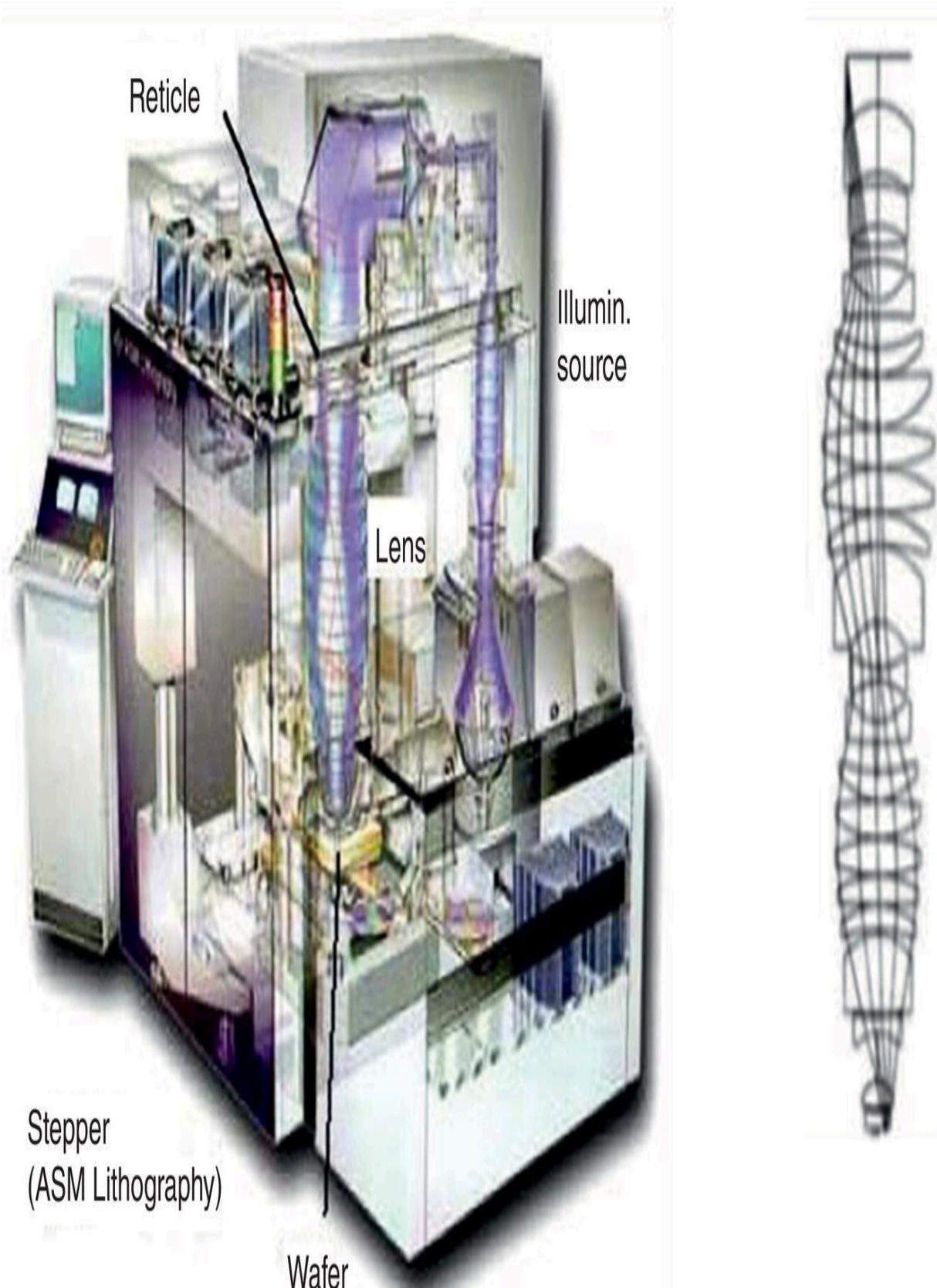

[Figure 10.33 Left, a stepper photolithography system \(ASM Lithography Co.\) ...](#)

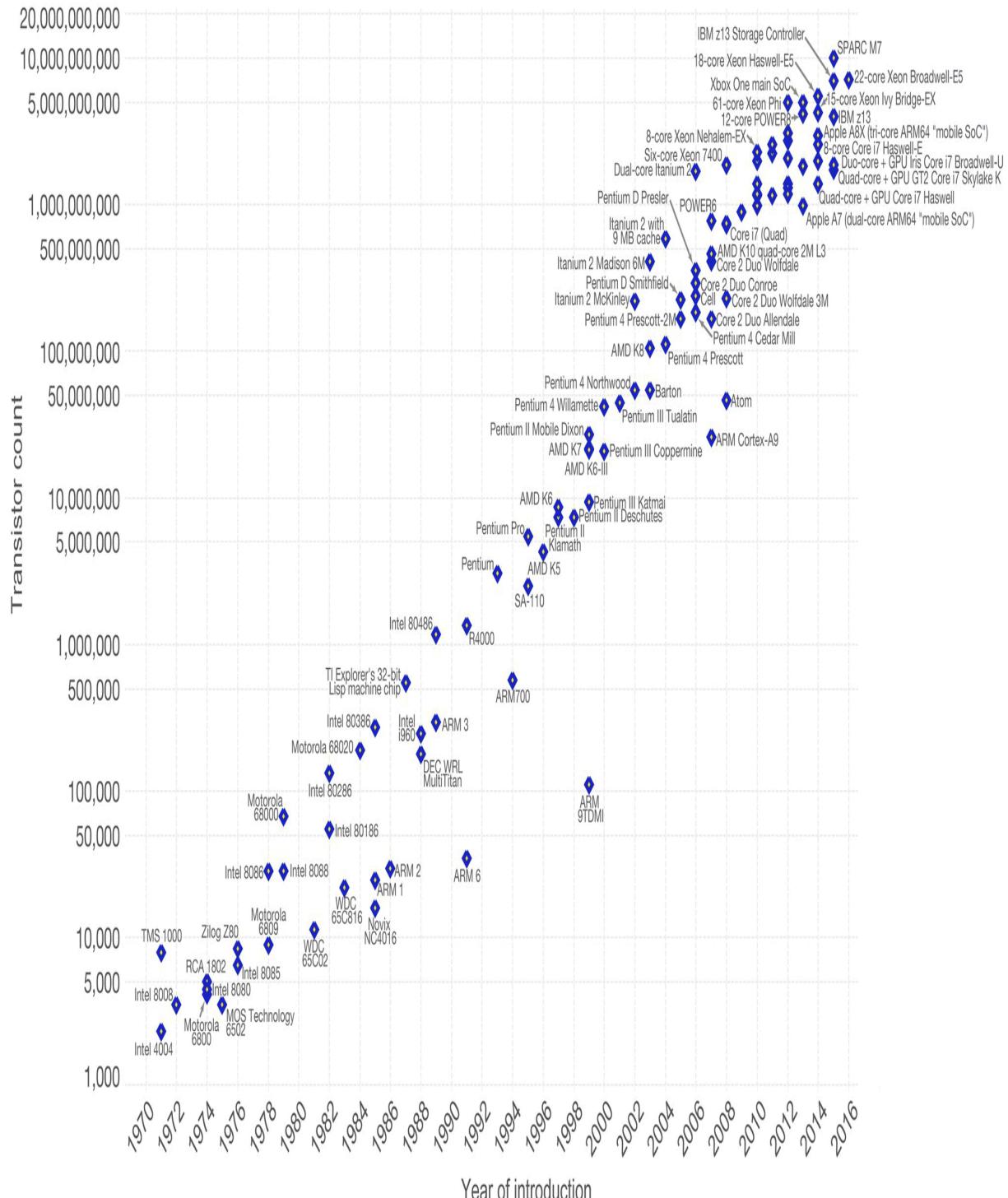

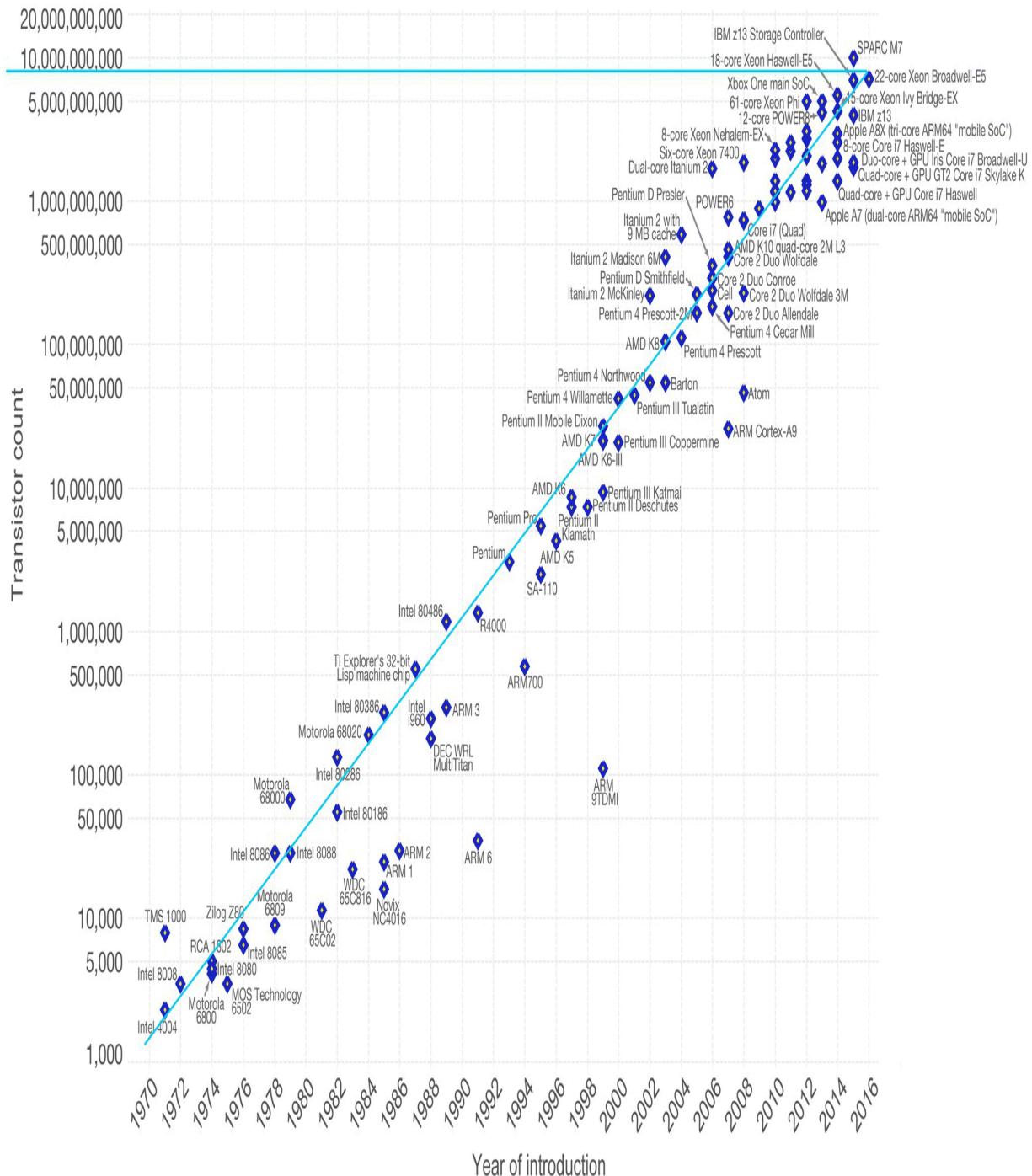

[Figure 10.34 1970 to 2016 progress in the transistor count per square inch....](#)

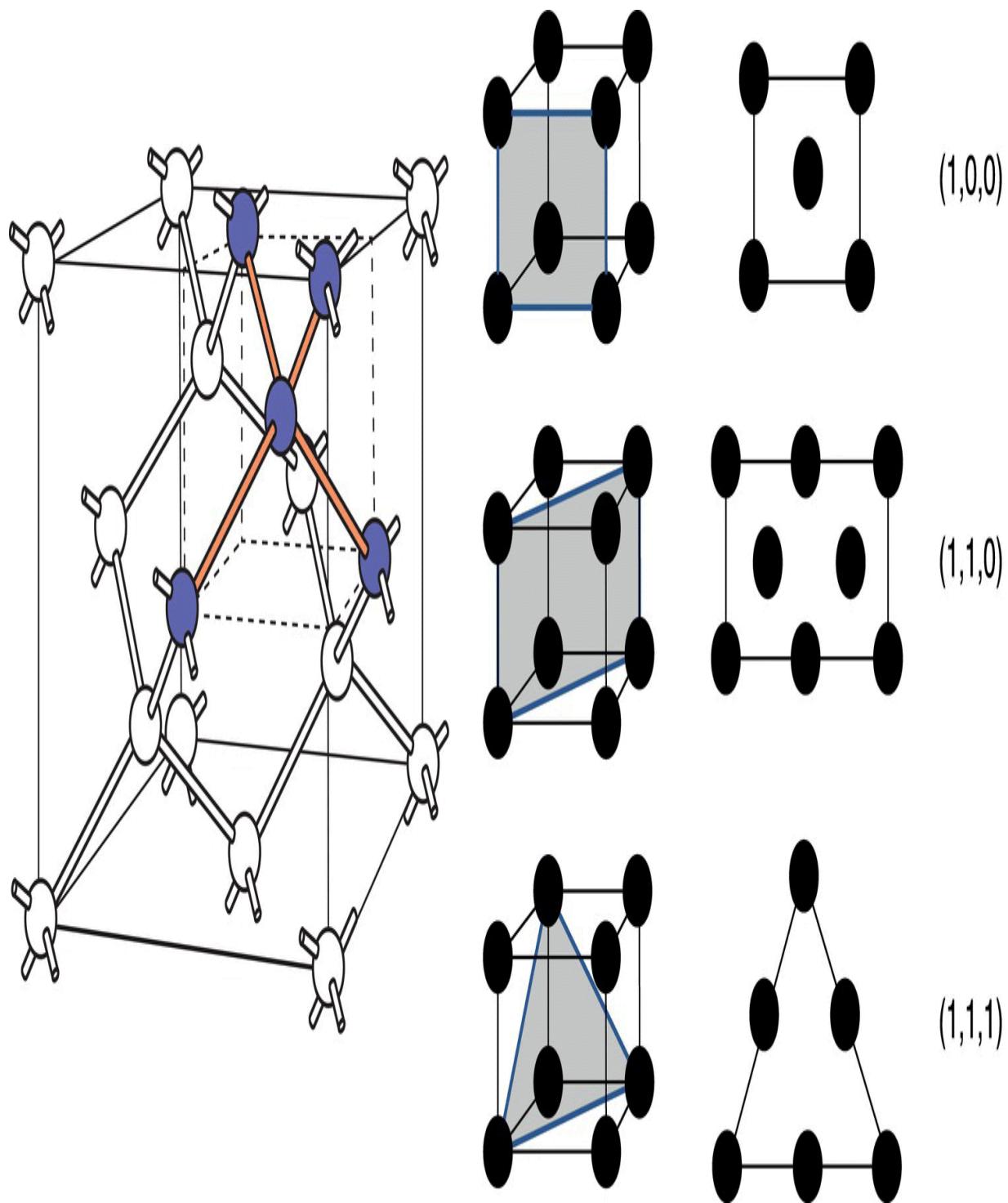

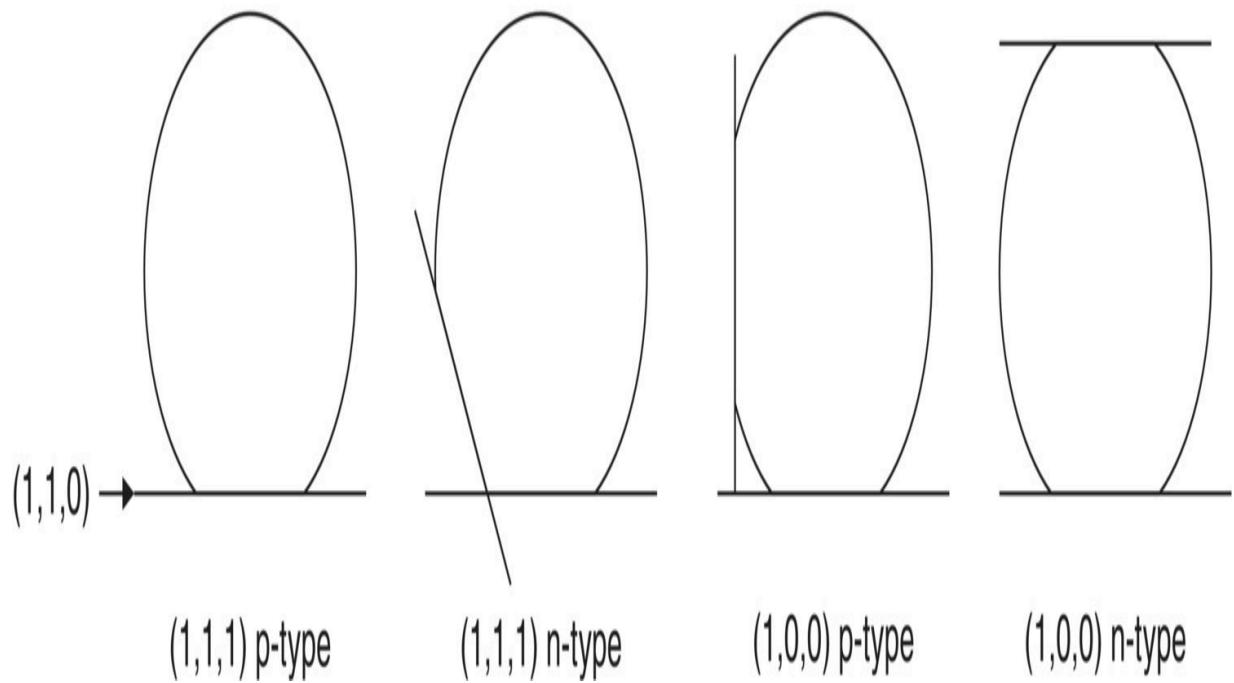

[Figure 10.35 Three ways we can slice the diamond crystal structure.](#)

[Figure 10.36 The flats in different locations around the periphery of the wa...](#)

Chapter 11

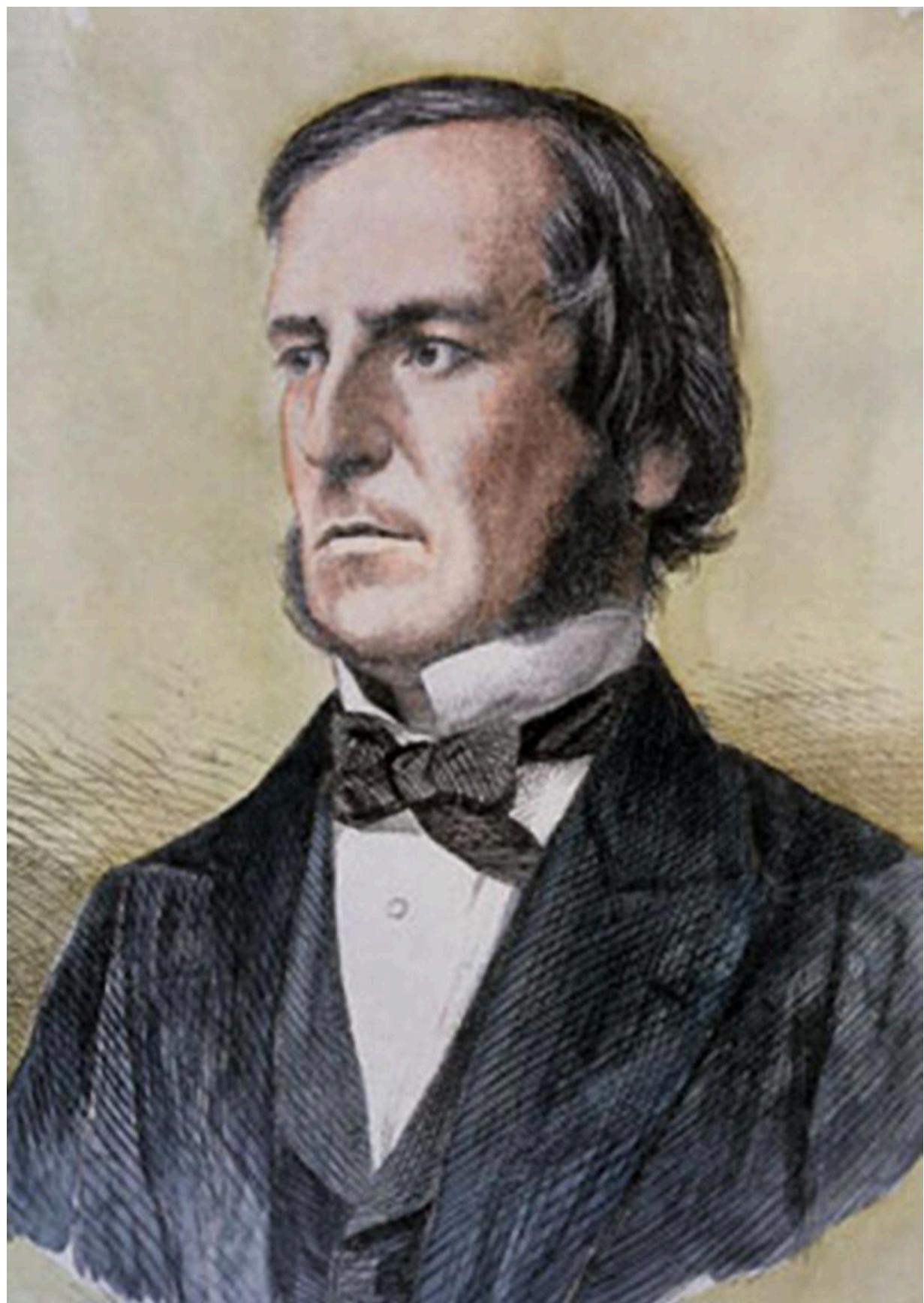

[Figure 11.1 George Boole developed the symbolic logic language called Boolea...](#)

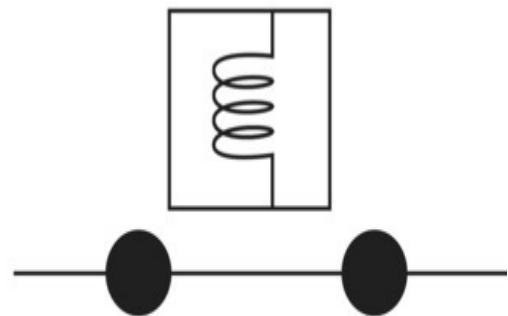

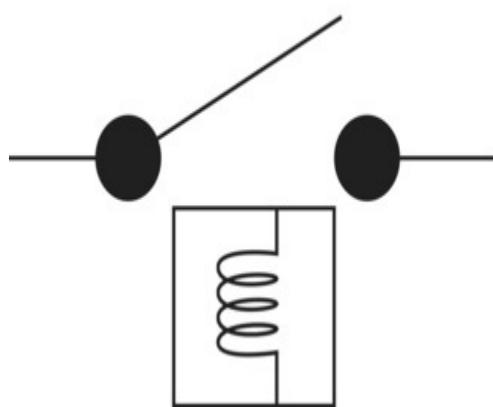

[Figure 11.2 Symbols of normally OFF \(left\) and normally ON \(right\) relays.](#)

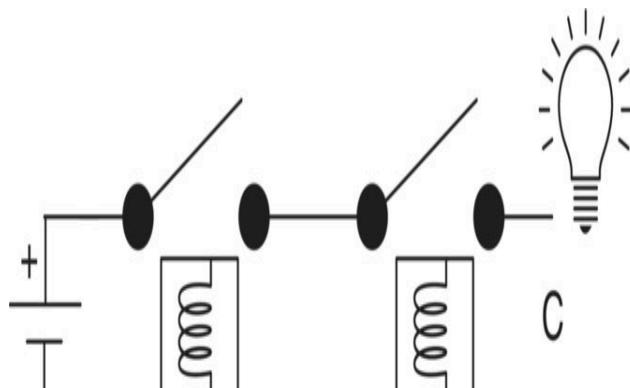

[Figure 11.3 The logic circuit AND using two normally closed relays \(top left...](#)

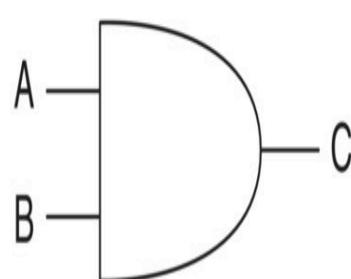

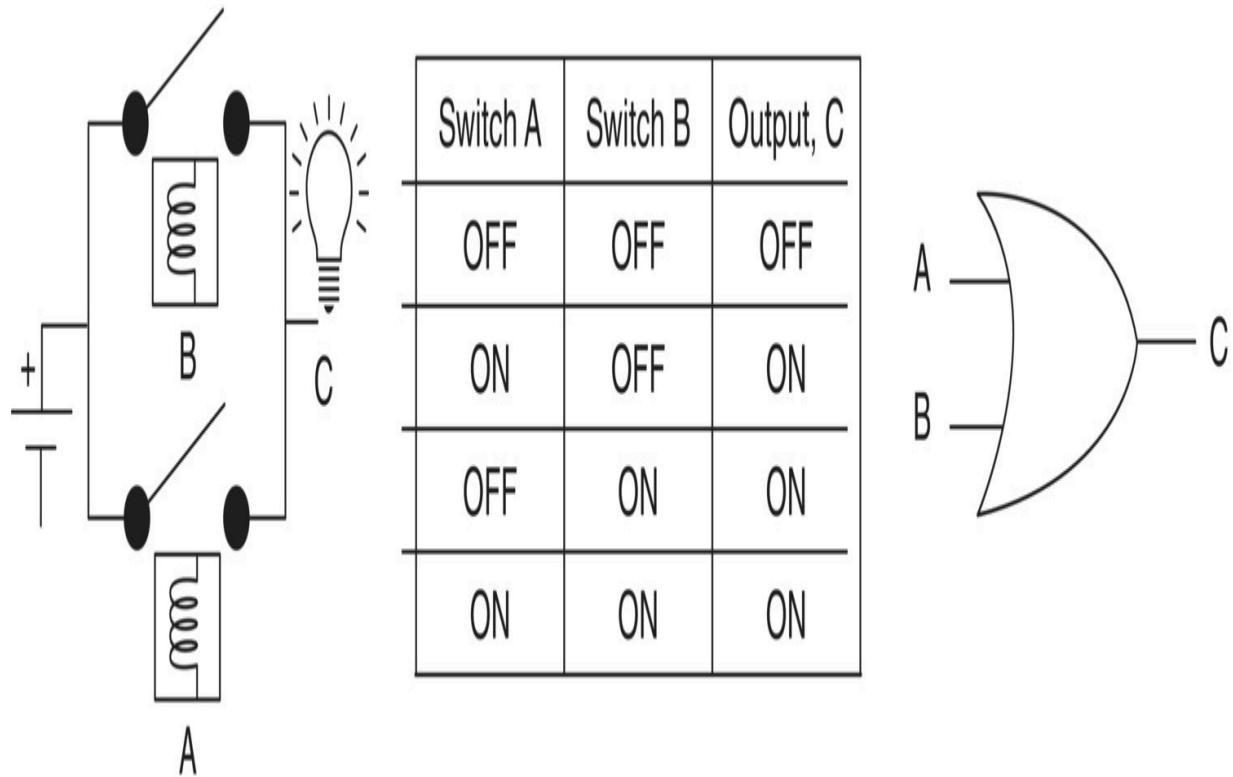

[Figure 11.4 The logic circuit OR using relays \(left\), its truth table \(middl...](#)

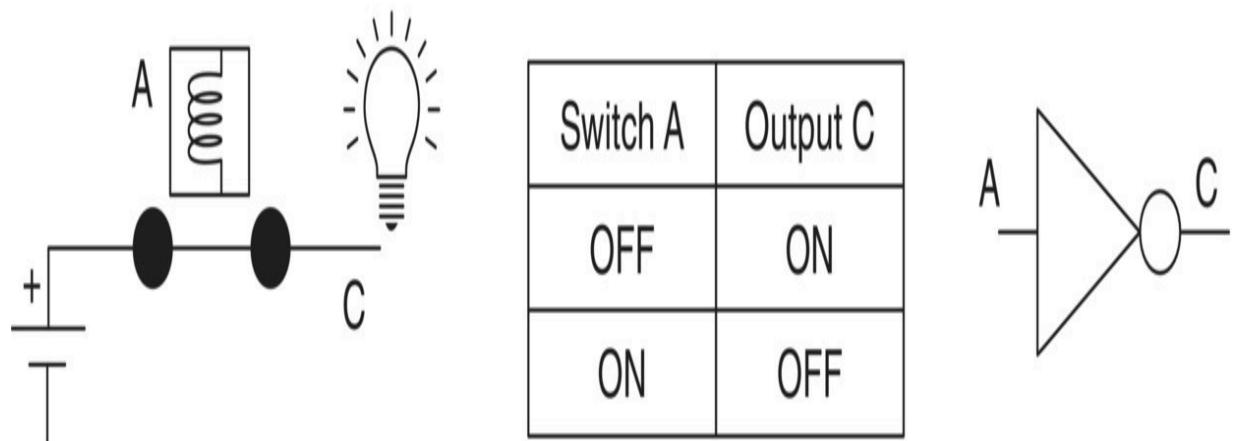

[Figure 11.5 The logic circuit NOT using a relay \(left\), the truth table \(mid...](#)

[Figure 11.6 The XOR truth table \(left\) and its symbol \(right\). For the outpu...](#)

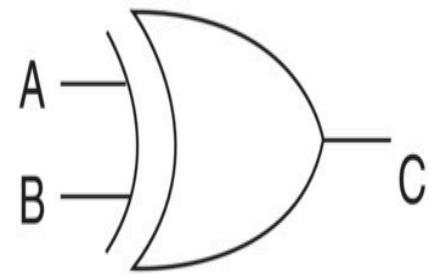

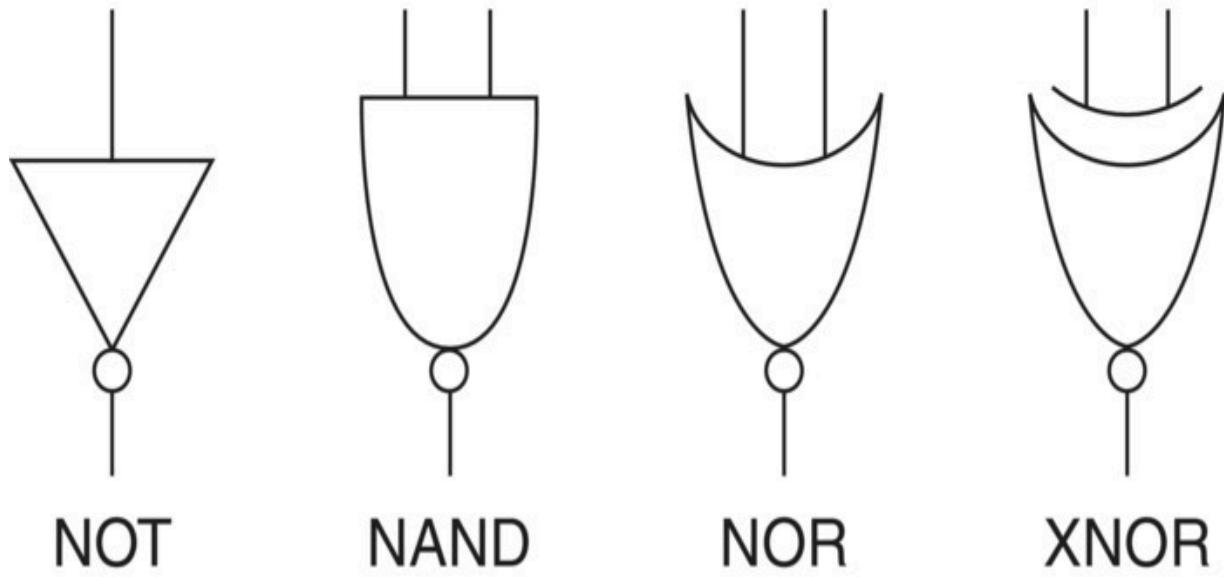

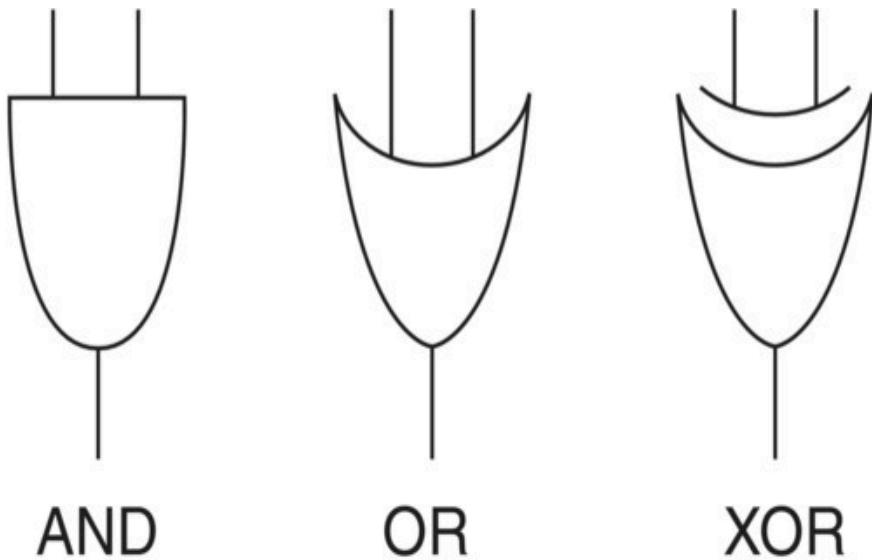

[Figure 11.7 The seven logic symbols we use in designing digital electronic c...](#)

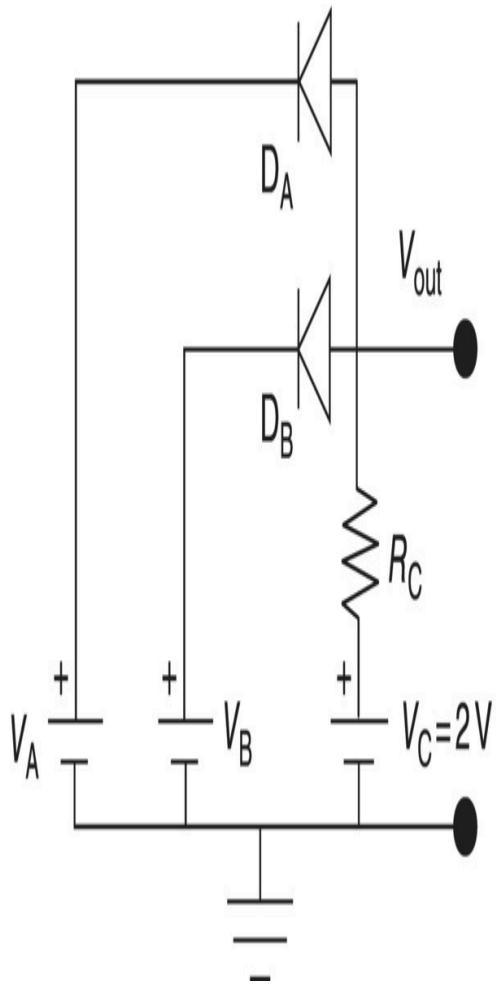

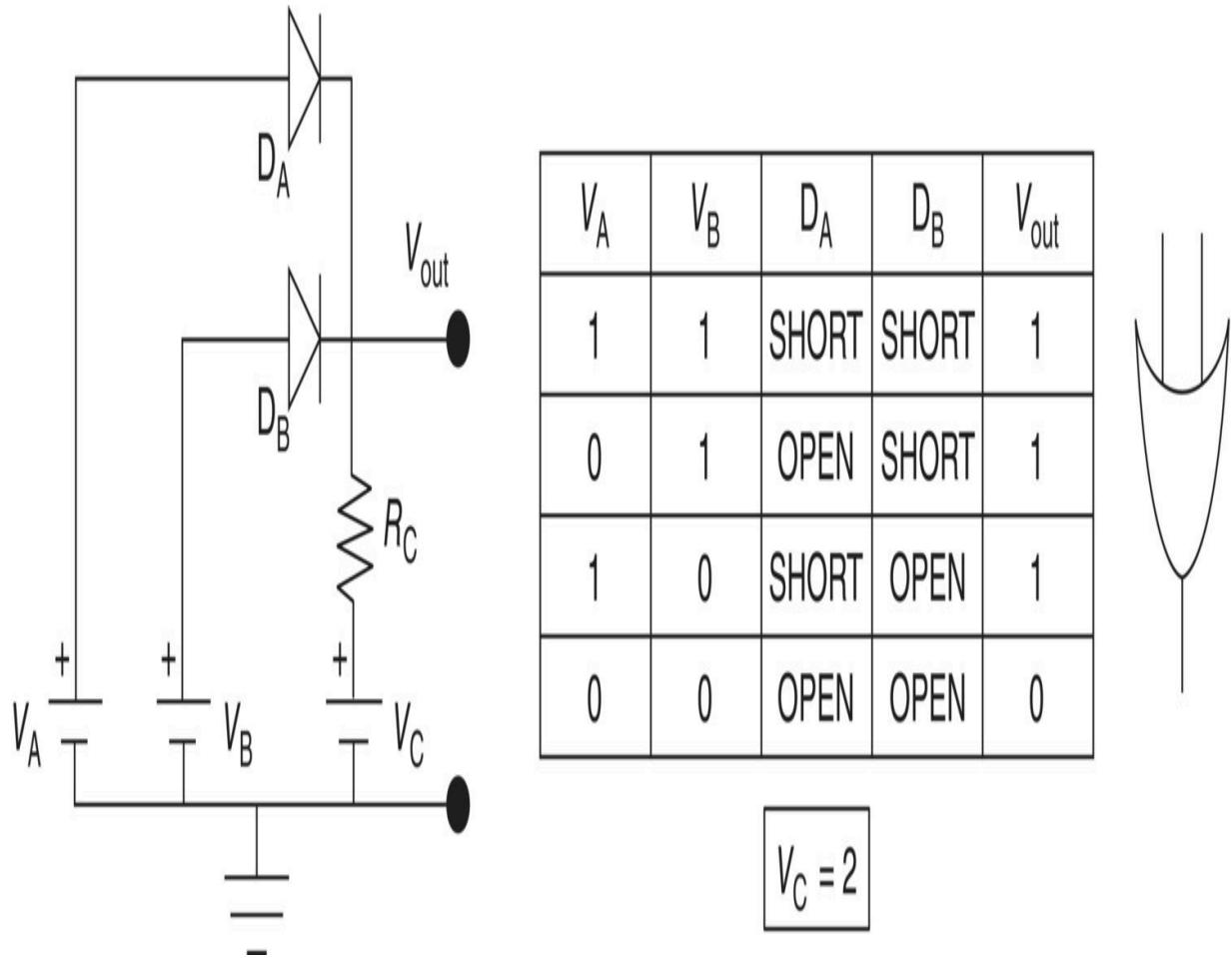

[Figure 11.8 Diode implementation of the AND function \(left\), the truth table...](#)

[Figure 11.9 Diode implementation of an OR function \(right\) with the truth ta...](#)

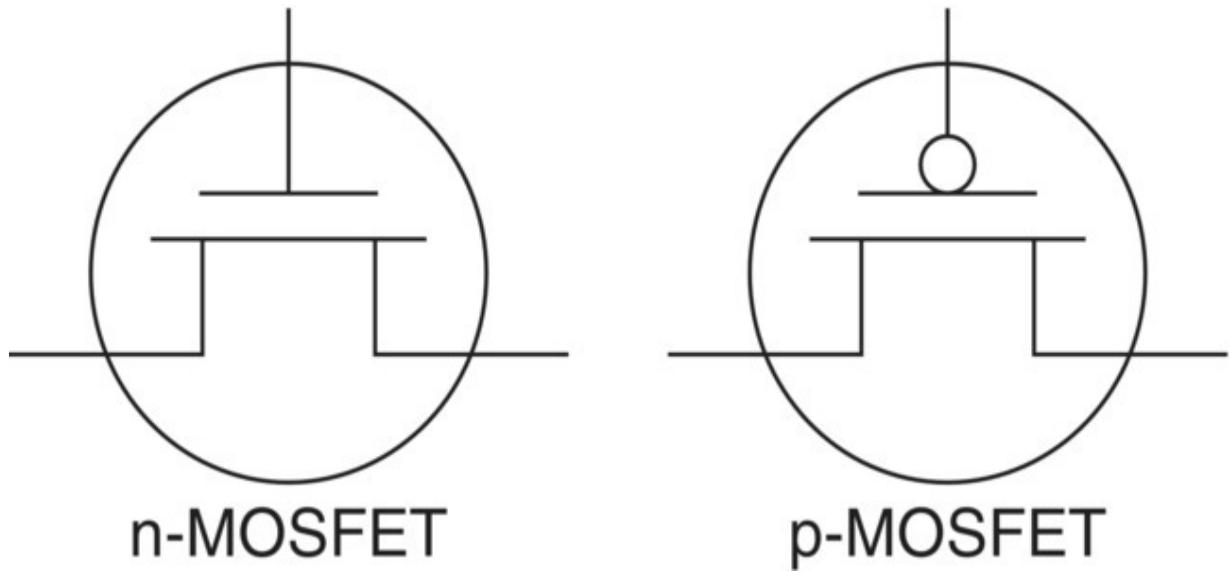

[Figure 11.10 Symbols for the n- \(left\) and p- \(right\) MOSFETs. The p-MOSFET ...](#)

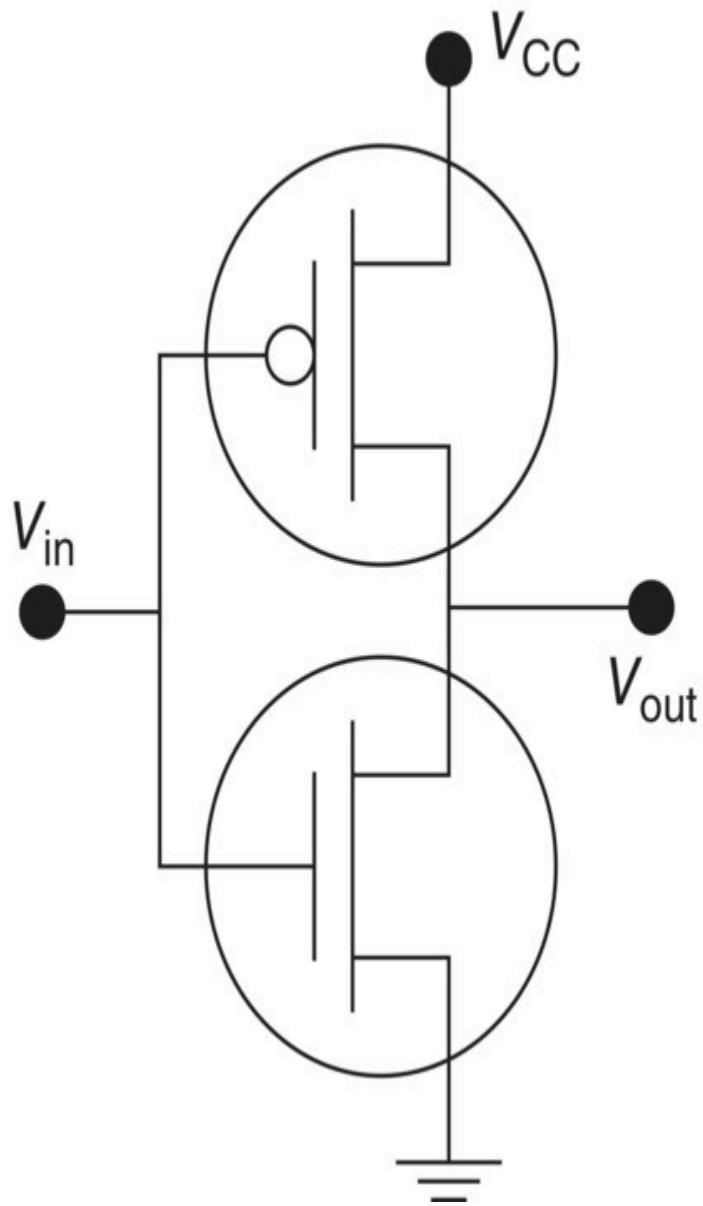

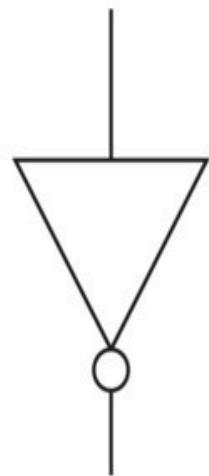

[Figure 11.11 The NOT circuit using CMOS with the truth table and its symbol....](#)

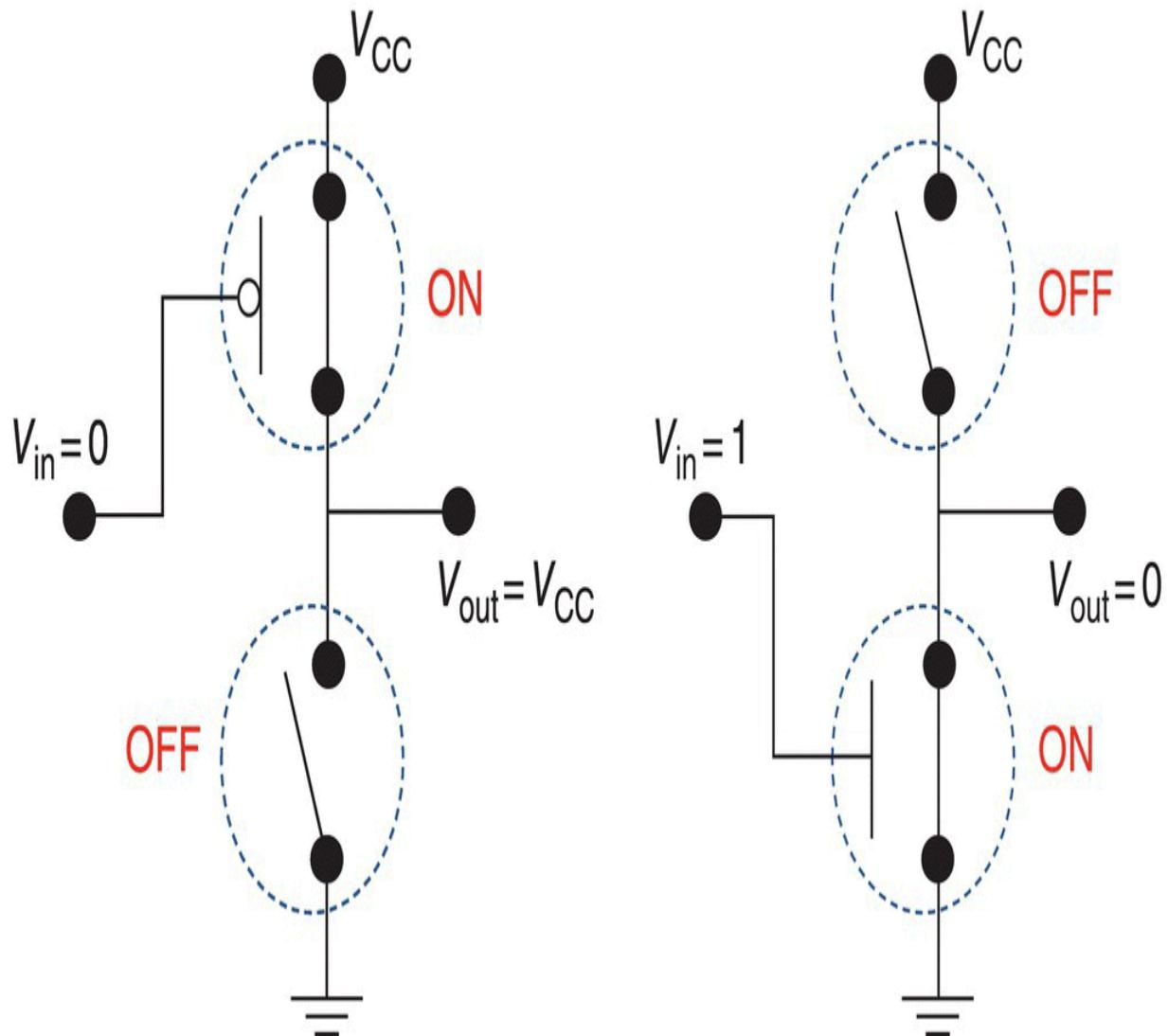

[Figure 11.12 The two states of the OR circuit, with  \$V\_{in}\$  OFF on the left and ...](#)

[Figure 11.13 The NOR circuit \(left\), the truth table \(top right\), and the NO...](#)

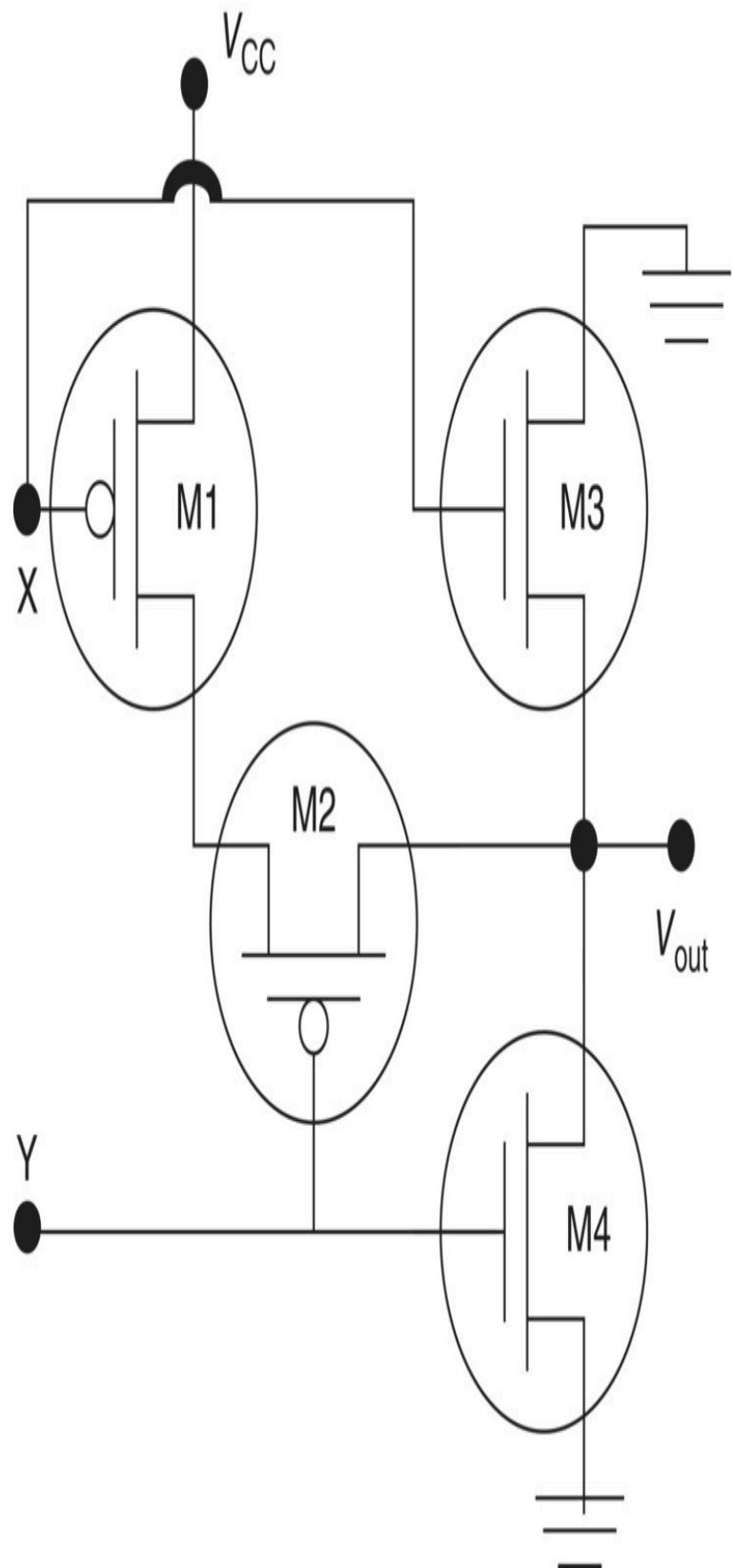

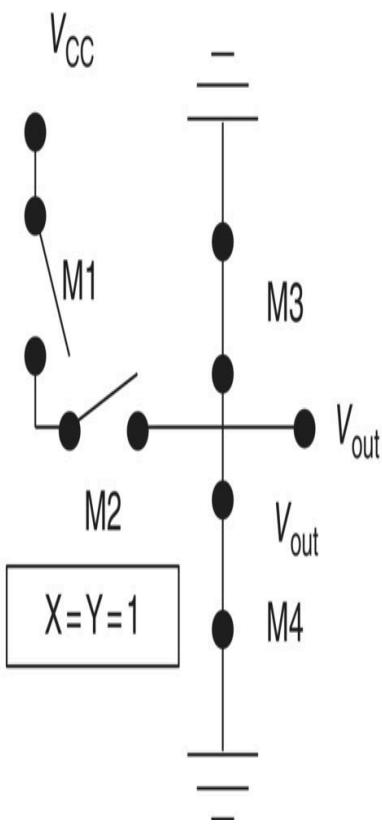

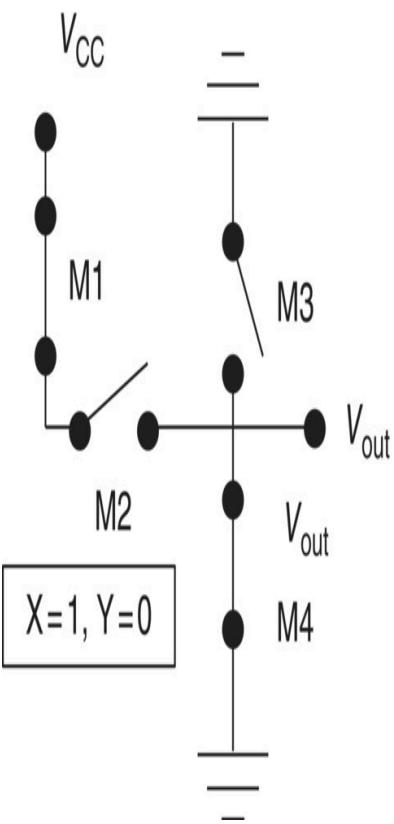

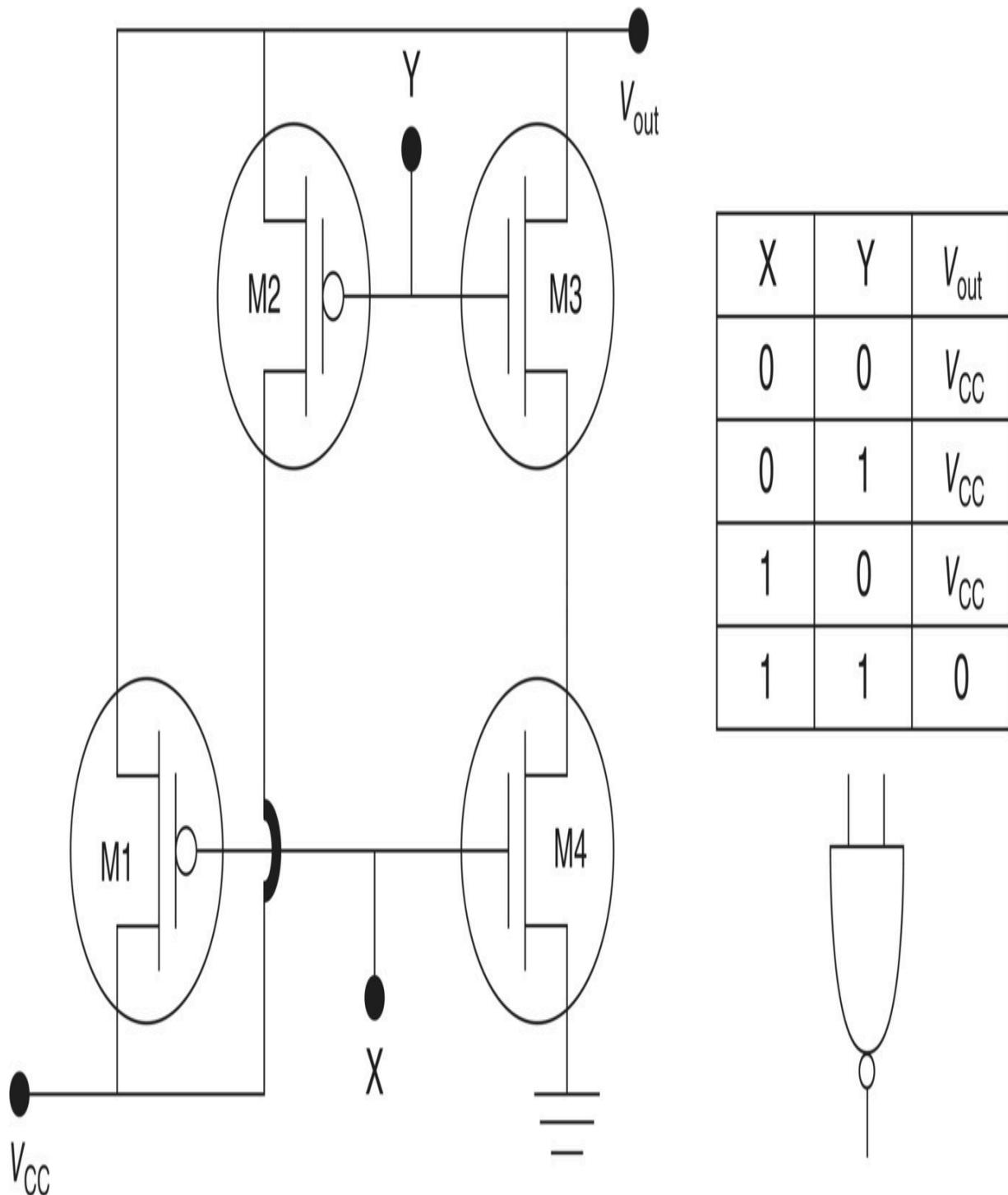

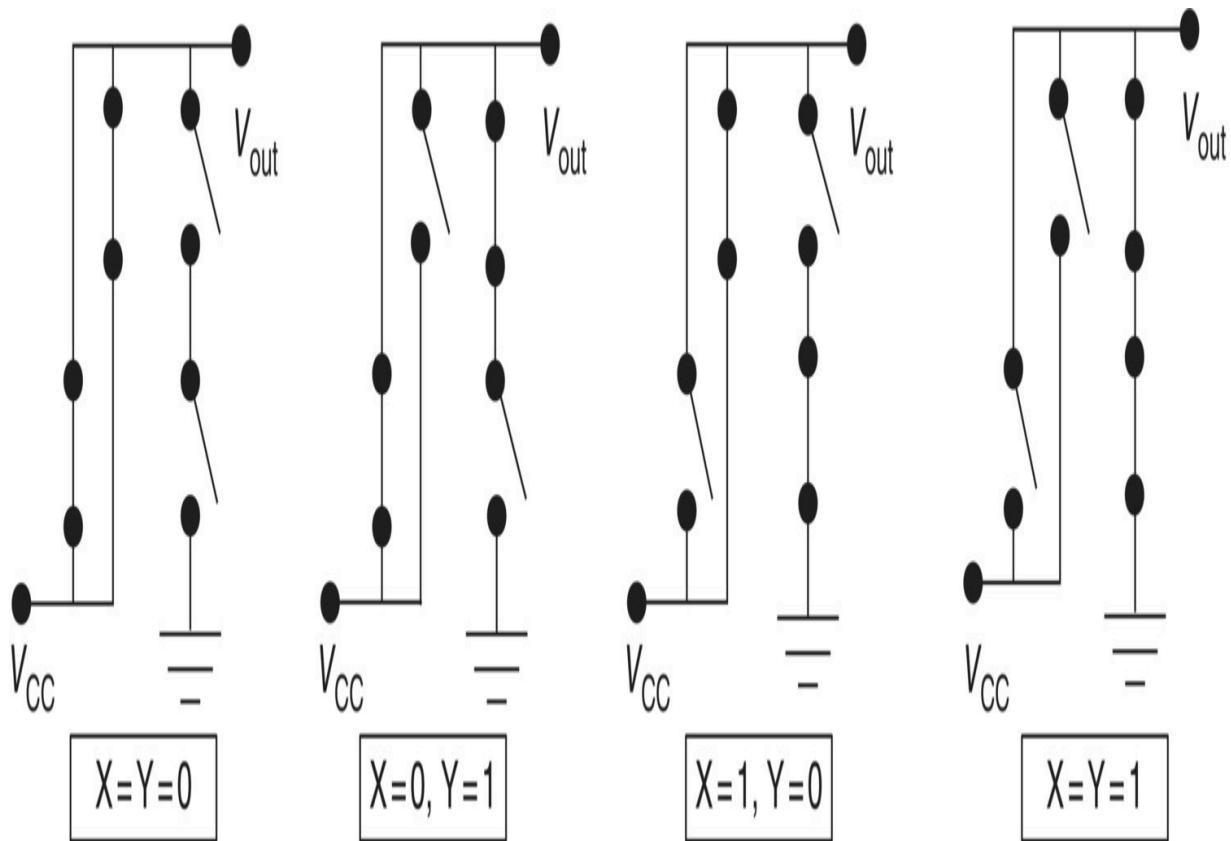

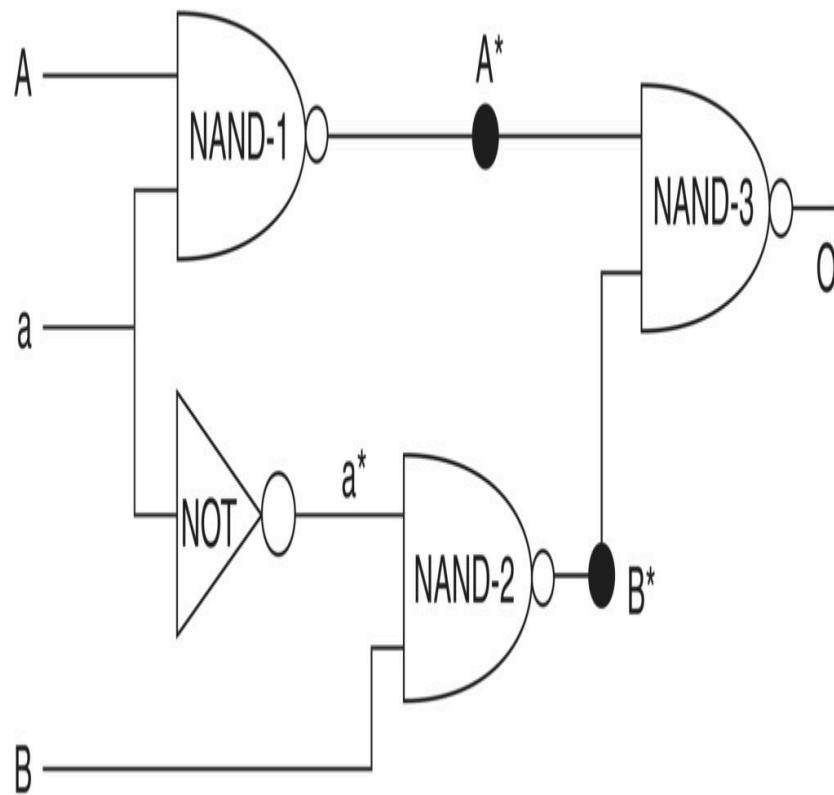

Figure 11.14 The switching status of the four MOSFET circuits as the two inp...

Figure 11.15 The NAND circuit (left) with the truth table (top right) and it...

Figure 11.16 The CMOS switching status as the inputs go independently from 0...

Figure 11.17 The logic function XNOR, its truth table, and its symbol.

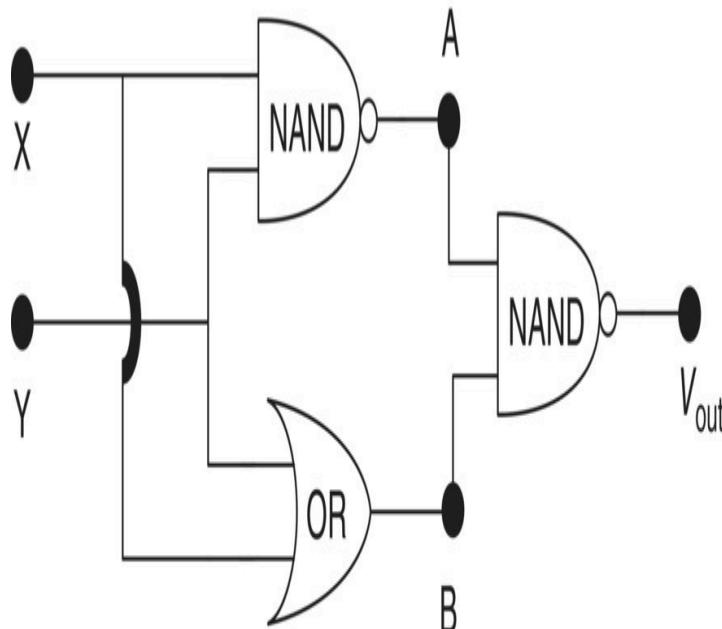

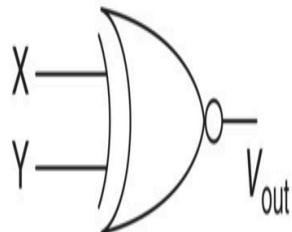

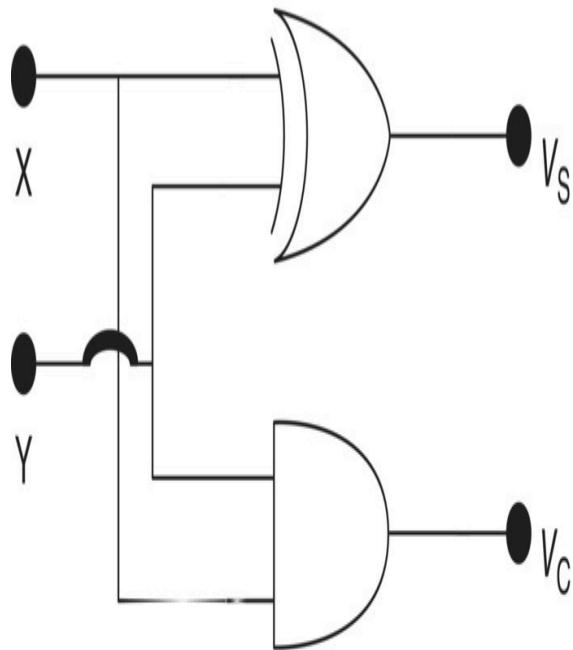

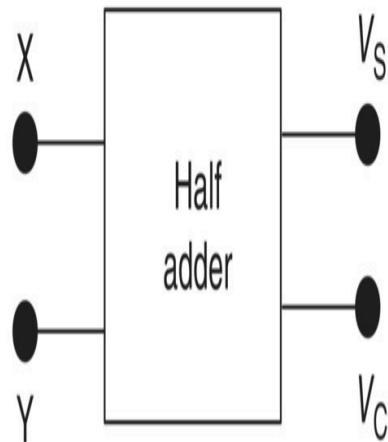

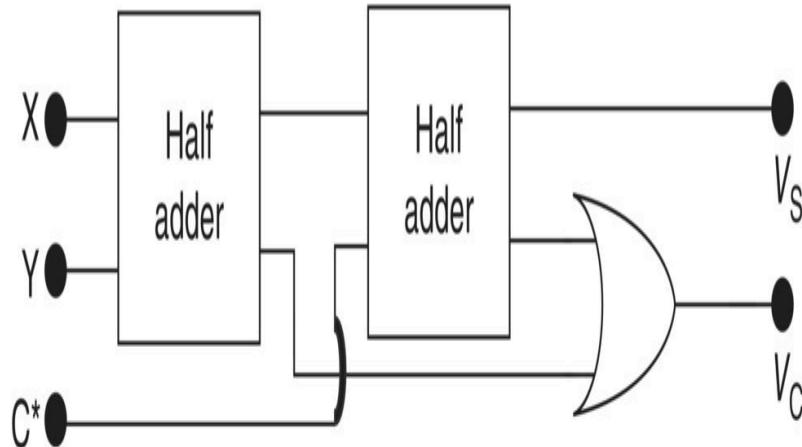

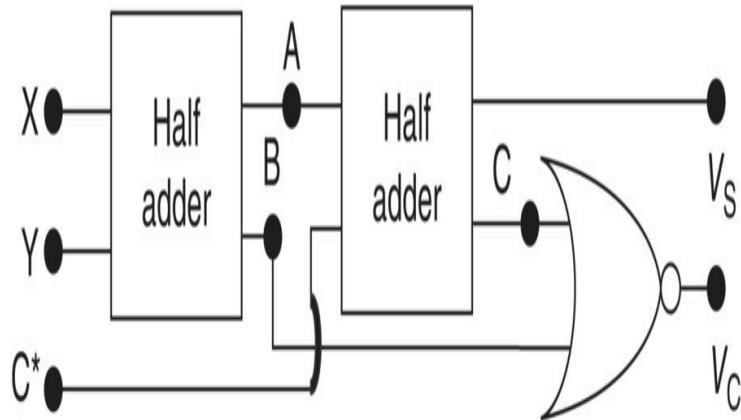

Figure 11.18 The half adder circuit (left), the truth table (right), and its...

Figure 11.19 The full adder with the truth table and the new symbol can be c...

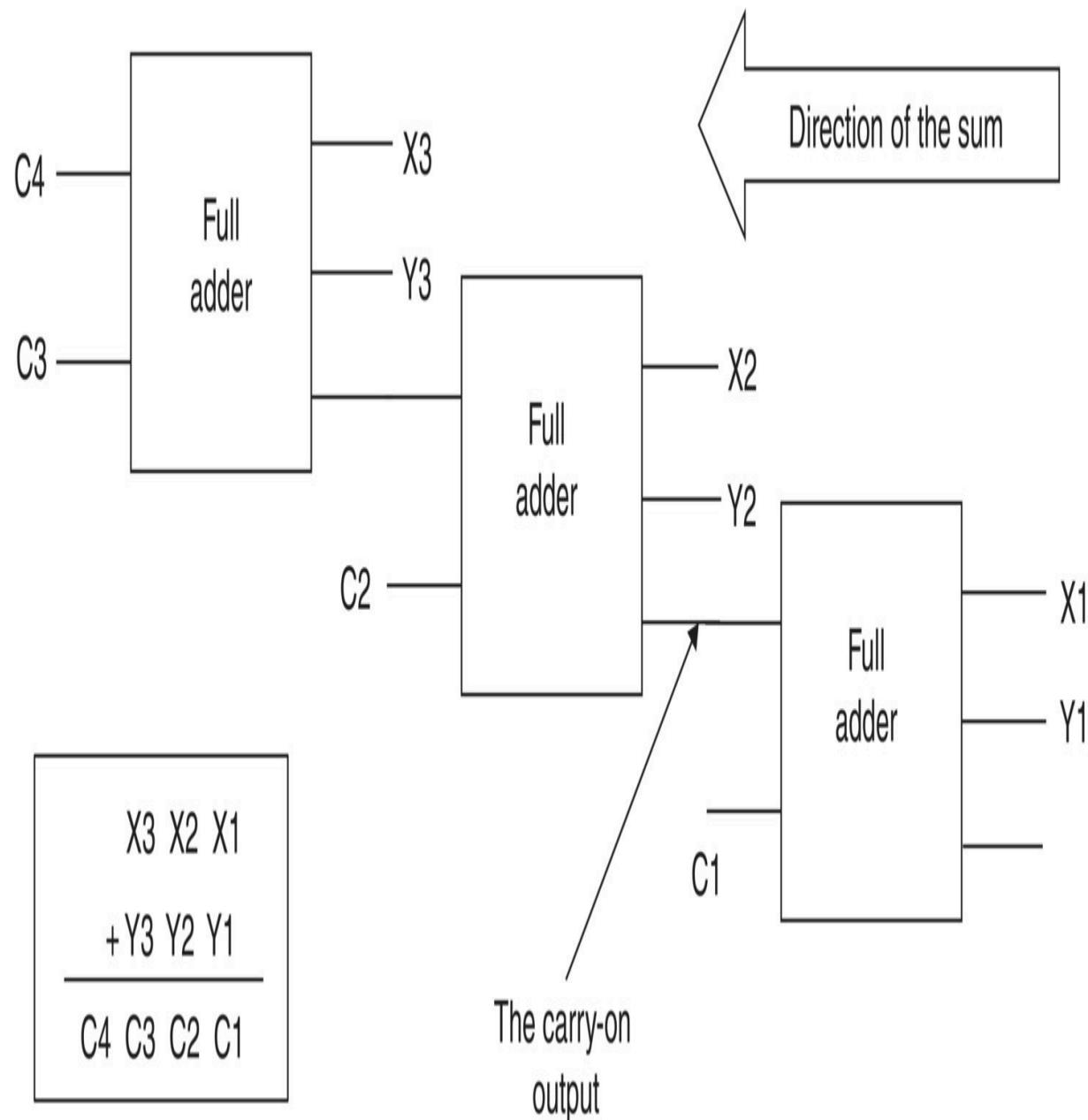

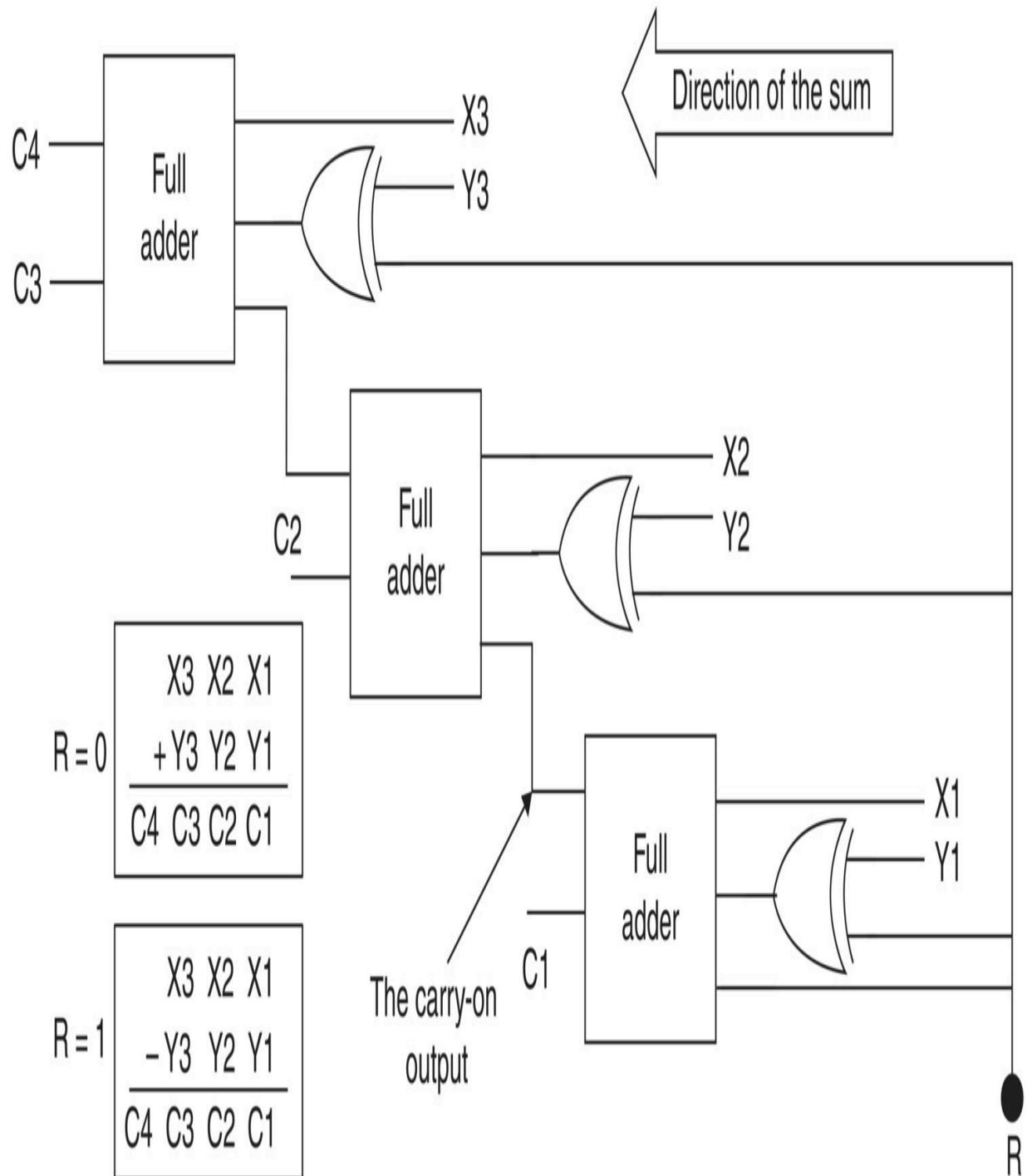

Figure 11.20 Adding two three-digit numbers. We use as many full adders as t...

Figure 11.21 How elementary (left) and high school students (right) subtract...

Figure 11.22 Step-by-step subtraction of two digital numbers.

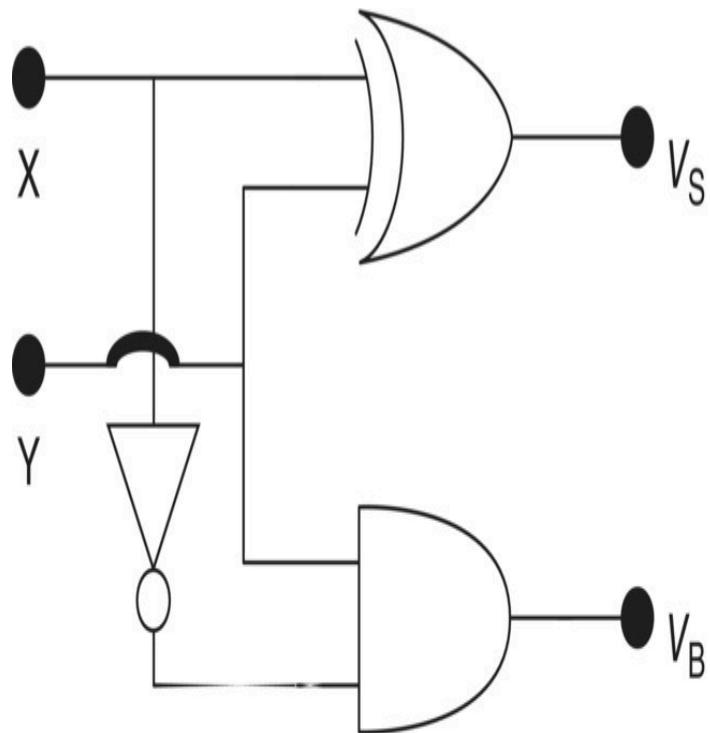

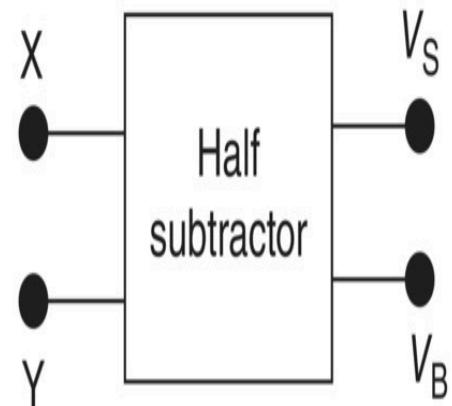

Figure 11.23 The half subtractor circuit (left), the truth table (top right)...

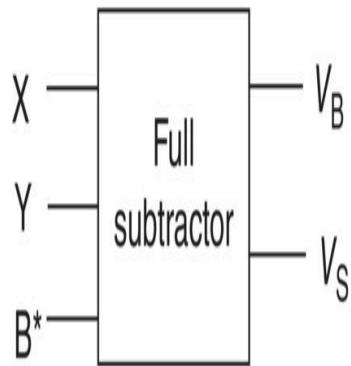

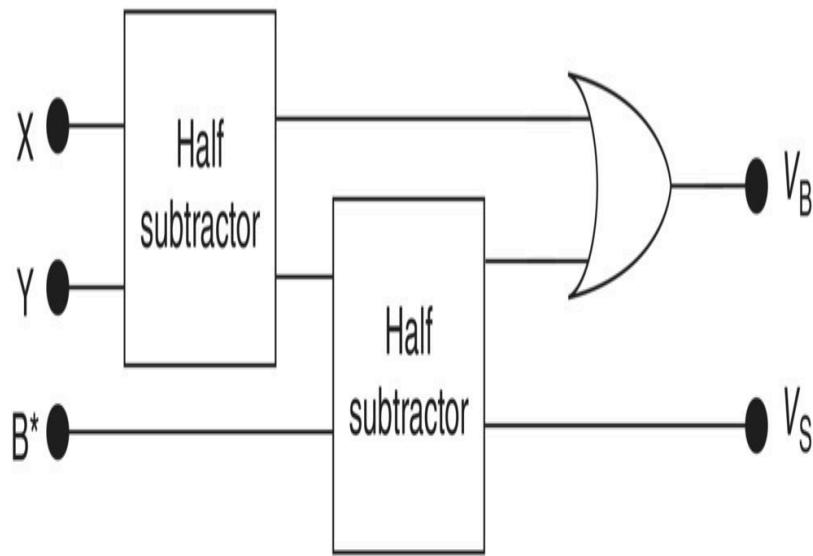

Figure 11.24 Full subtractor (top left), its symbol (lower left), and the tr...

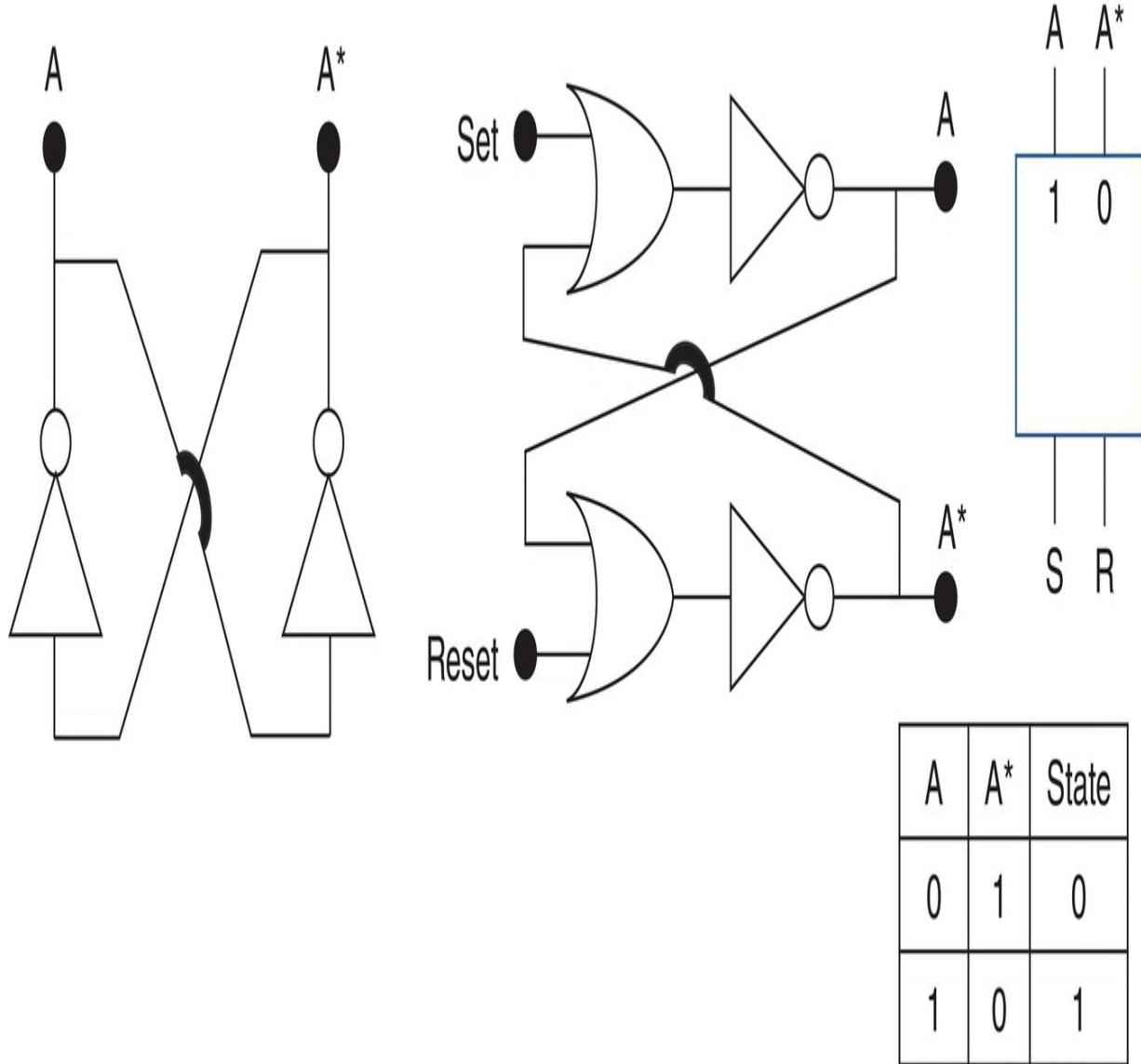

Figure 11.25 Flip-flop (left) and latch (middle) modules, their symbol, and ...

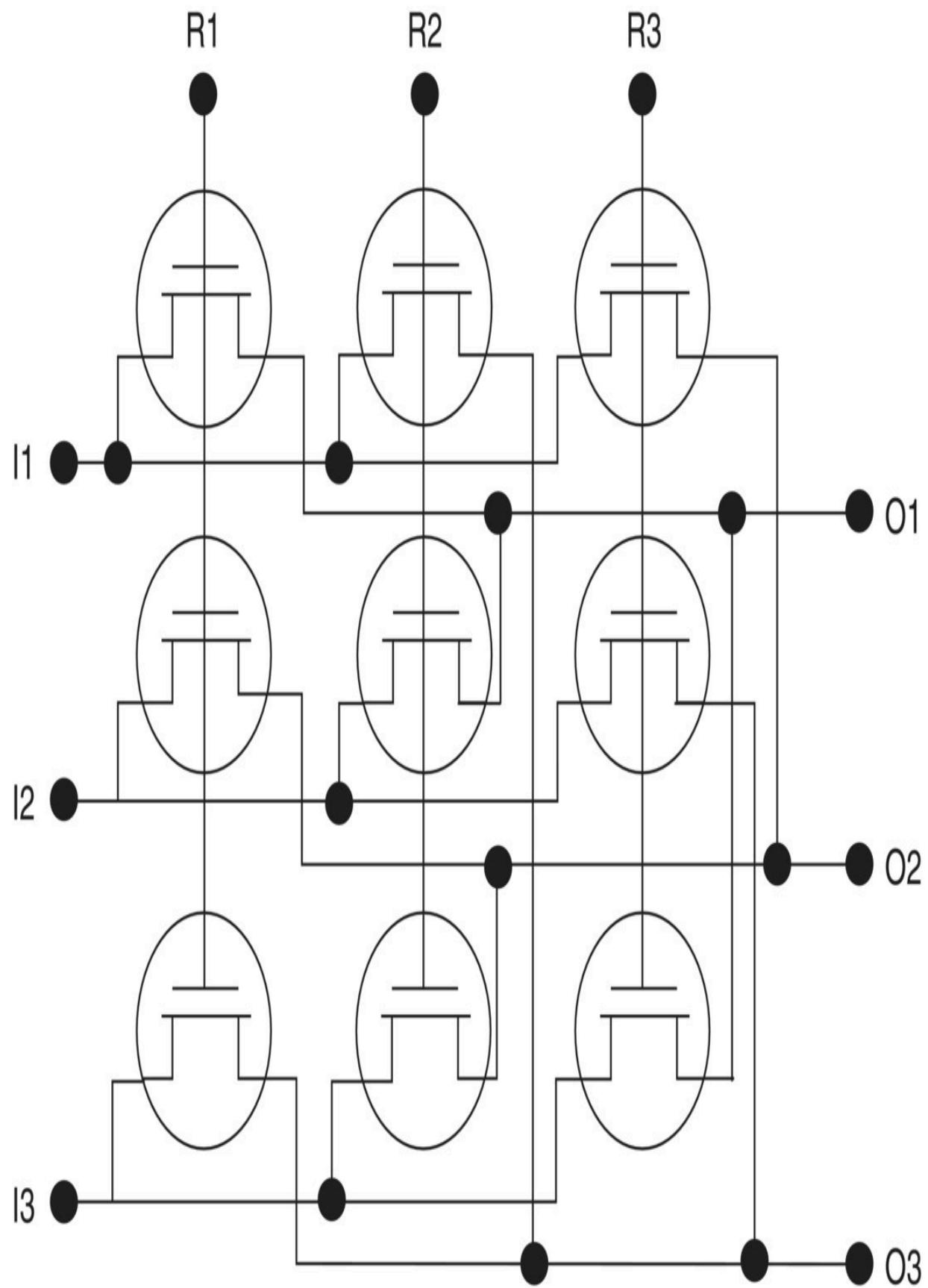

Figure 11.26 A  $3 \times 3$  shift register.

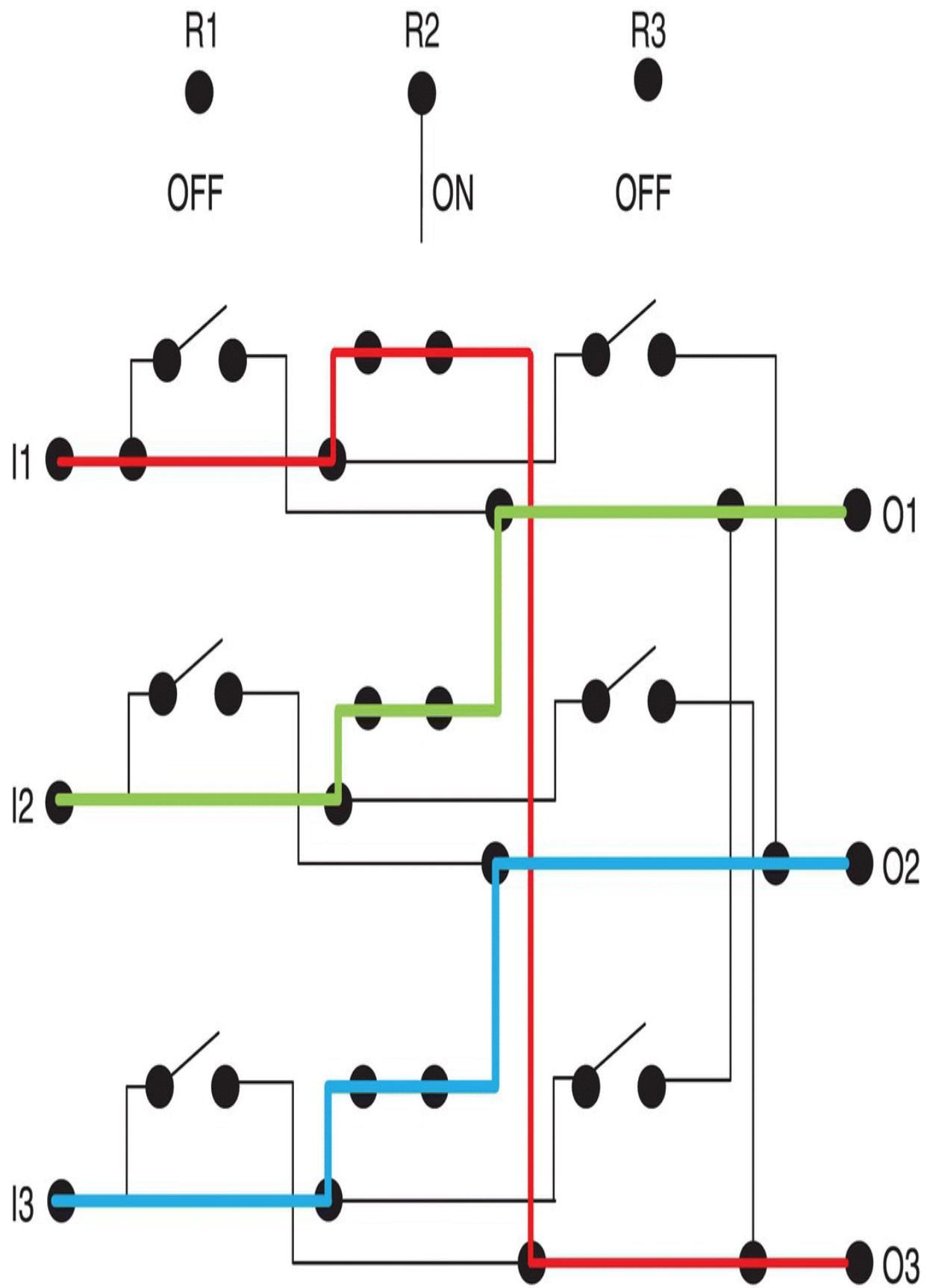

Figure 11.27 Electrical path of Figure 11.26 when R2 is ON and all the other...

Figure 11.28 The multiplication of two digital numbers is the same as in the...

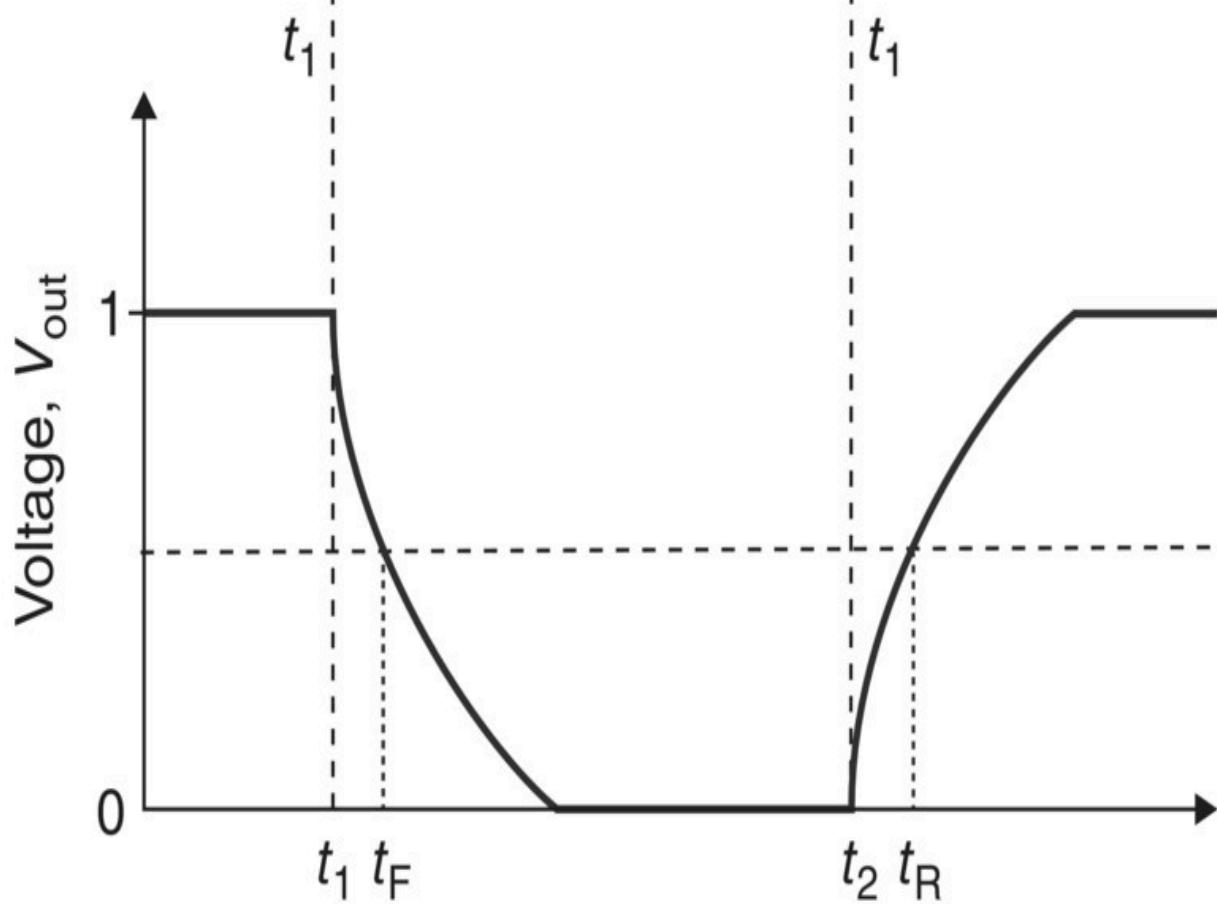

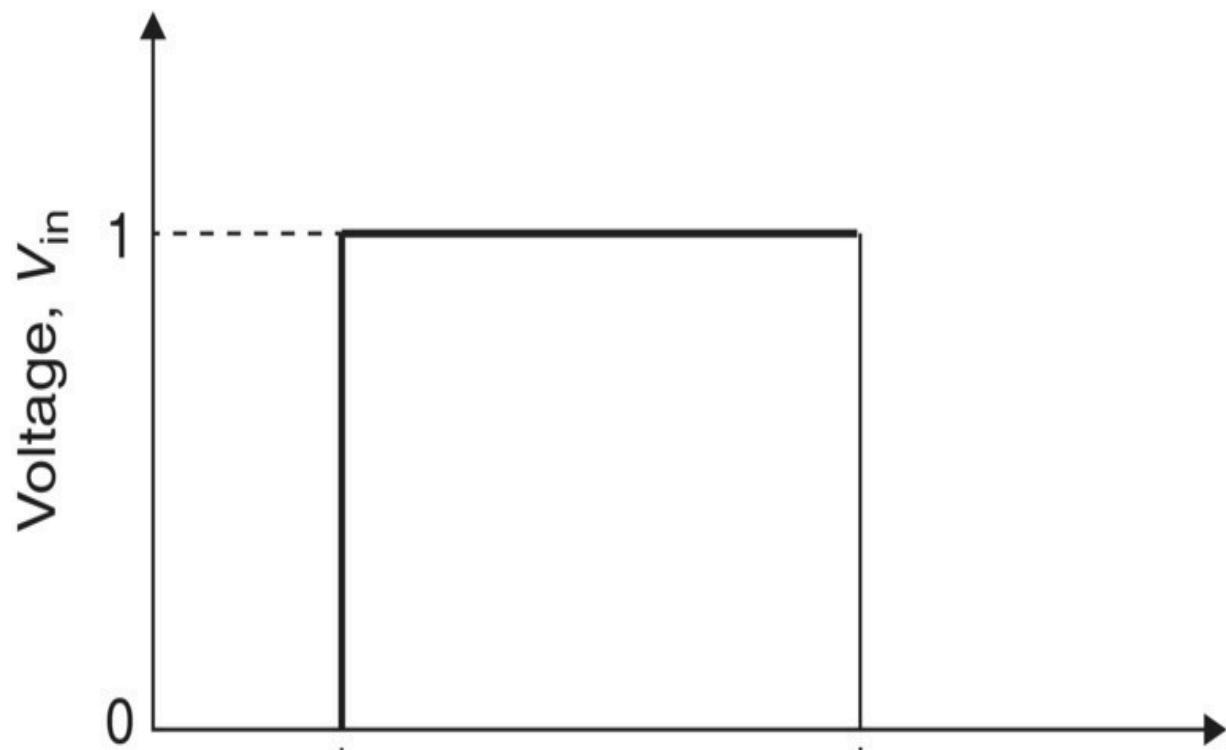

Figure 11.29 The output of a device driven by a perfect square input pulse (...)

[Figure 11.30 The half adder module.](#)

[Figure 11.31 The development of the truth table of the full adder.](#)

[Figure 11.32 A full adder with the option to add or subtract the numbers dep...](#)

[Figure 11.33 How we divide in the decimal \(left\) and the digital \(right\) sys...](#)

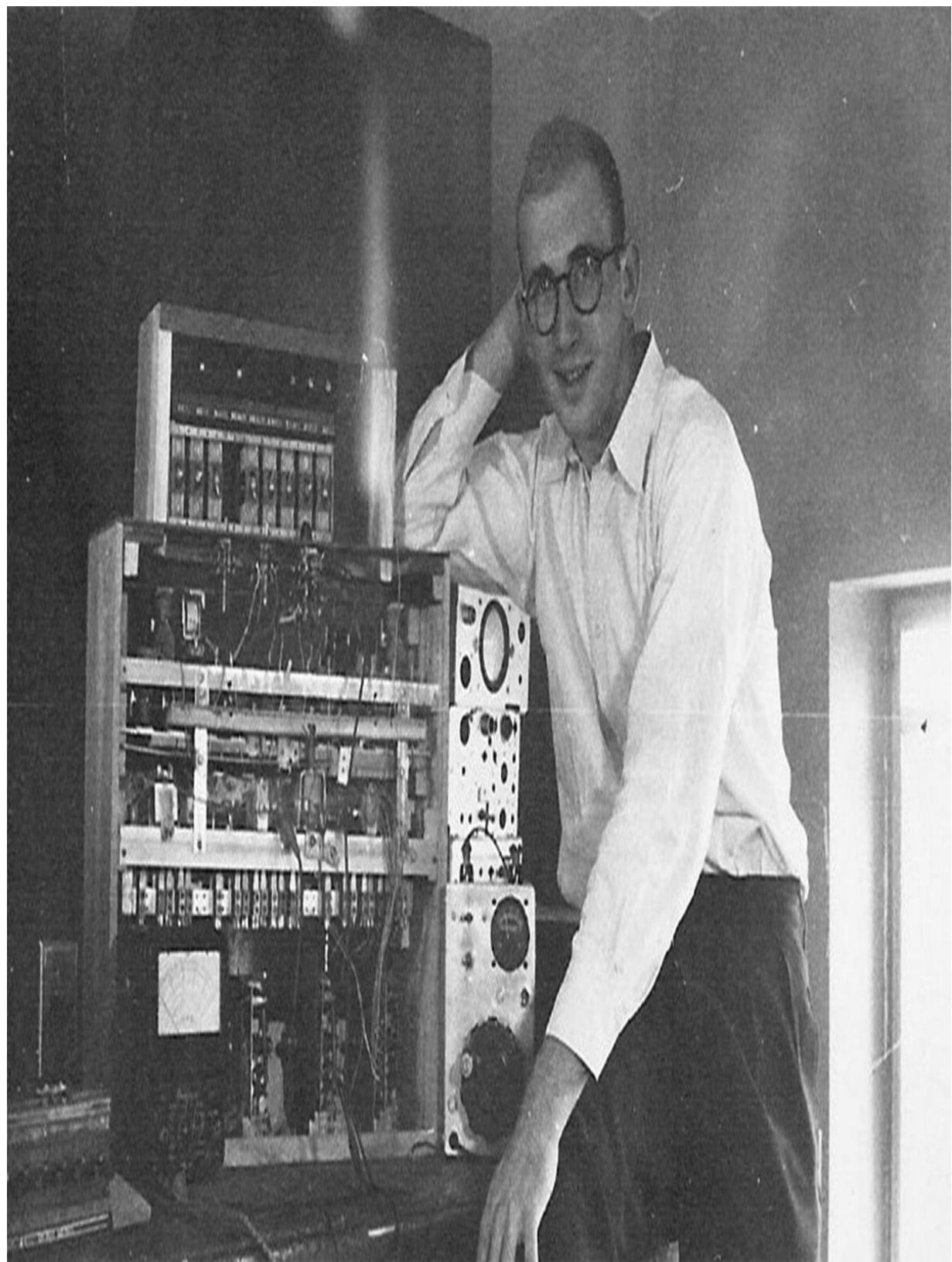

[Figure 11.34 The author with a symbolic logic machine designed in 1962 using...](#)

Chapter 12

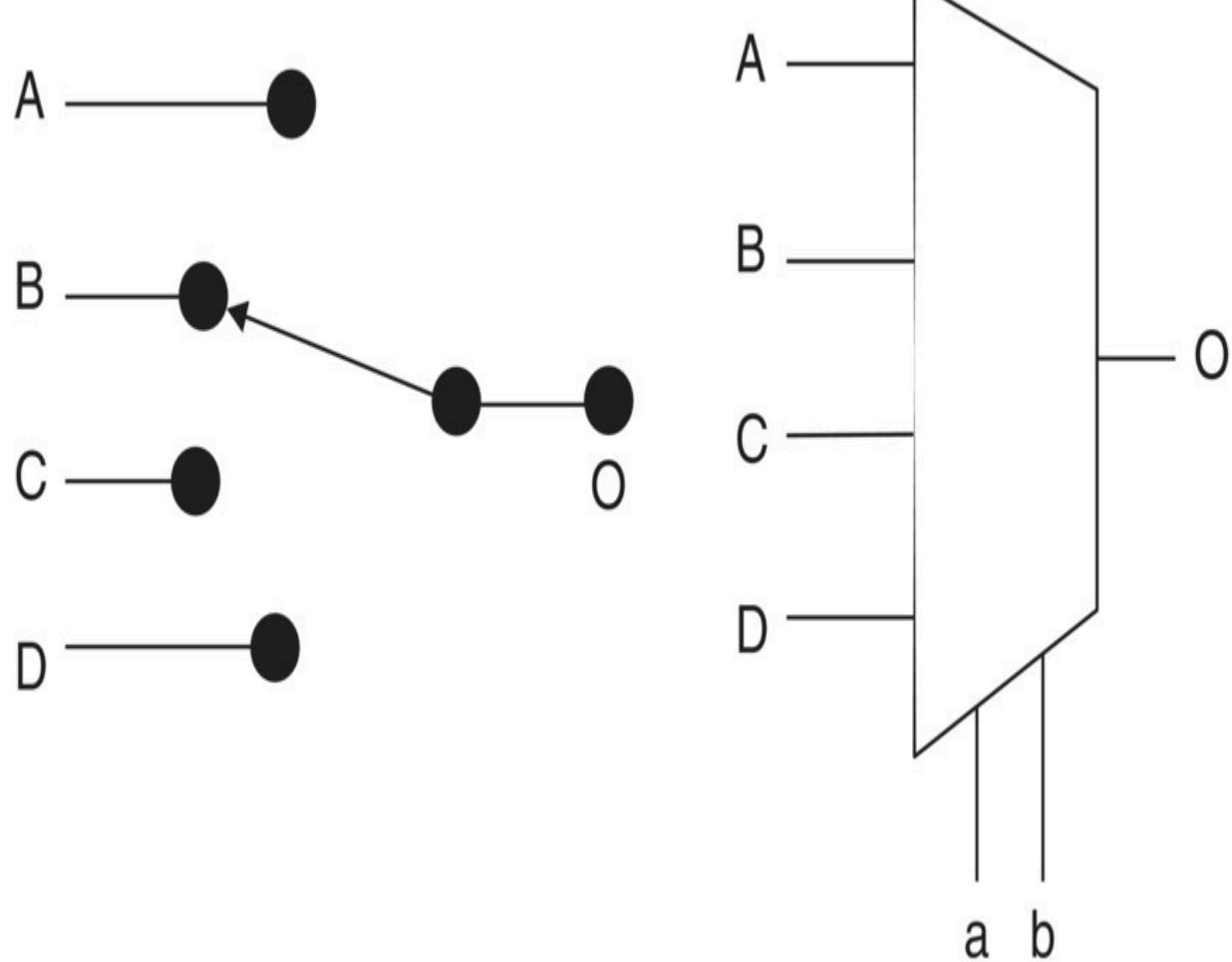

[Figure 12.1 A MUX selects one of the many inputs, like a rotary switch. The ...](#)

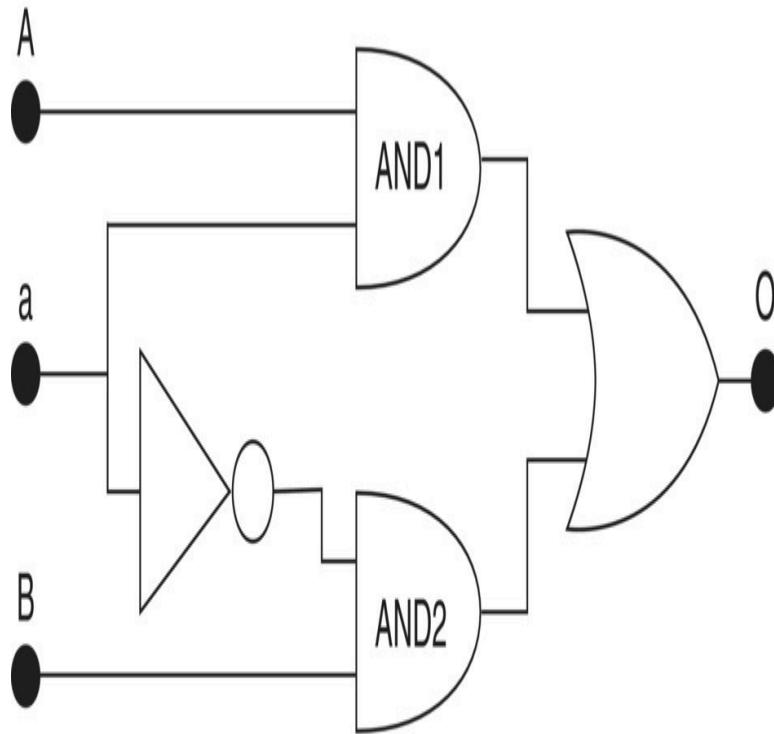

[Figure 12.2 A 2 to 1 MUX implementation using two ANDs, one NOT, and one OR ...](#)

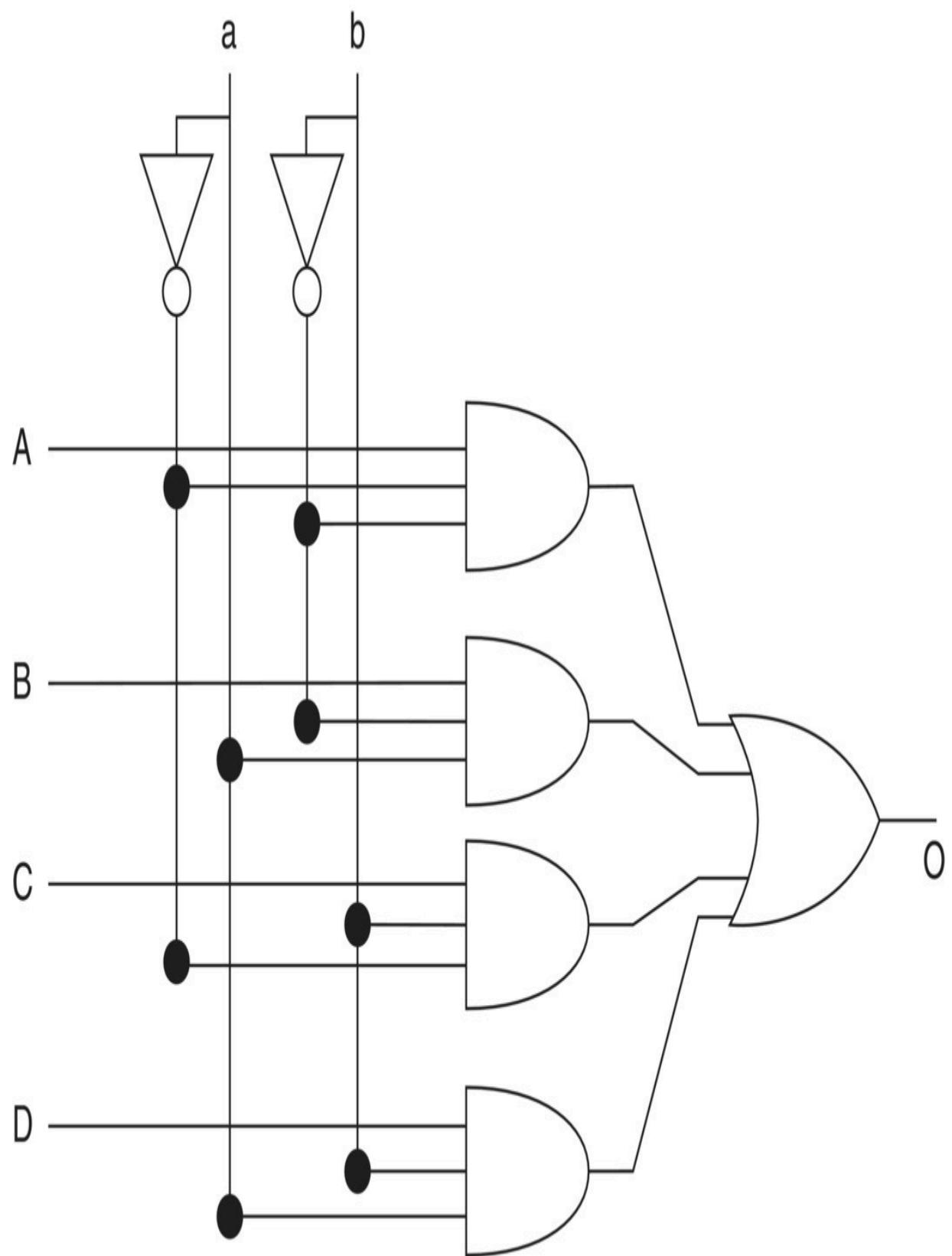

[Figure 12.3 Implementation of a 4 to 1 MUX, using ANDs and NOTs. The two con...](#)

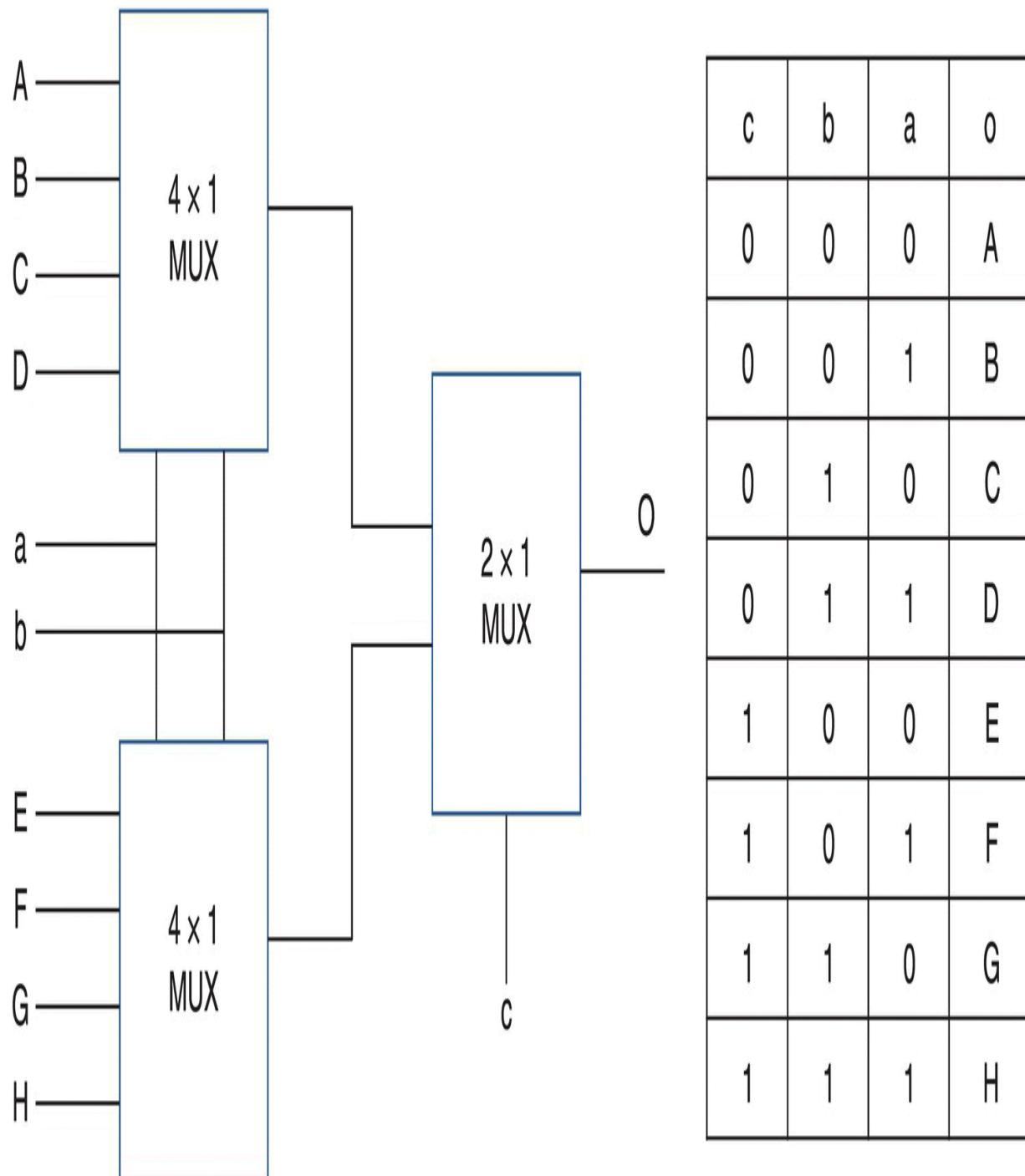

[Figure 12.4 An 8 to 1 MUX can be implemented by using smaller MUXs. Control ...](#)

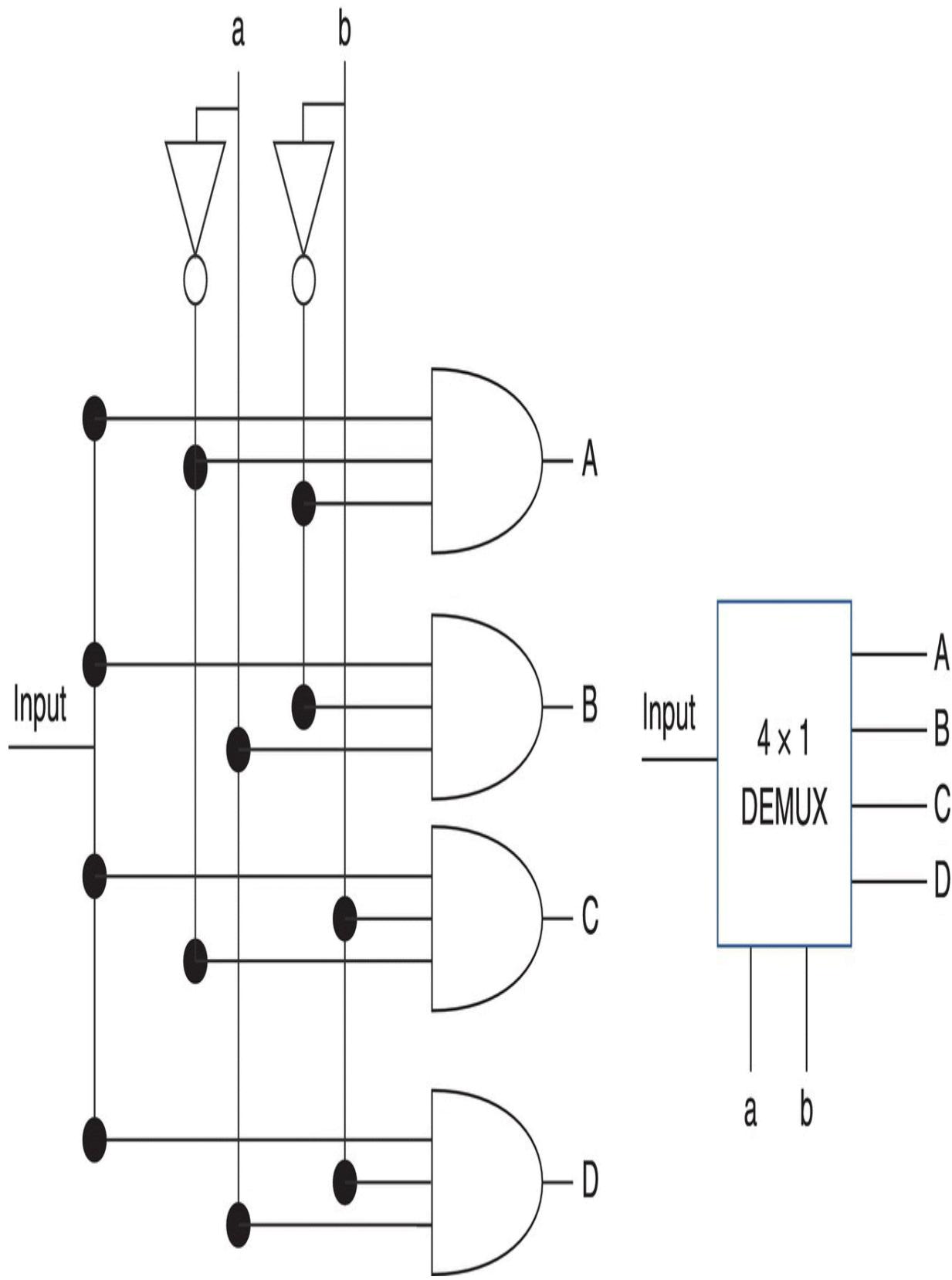

[Figure 12.5 A 1 to 4 DEMUX using AND and NOT modules with the symbol on the ...](#)

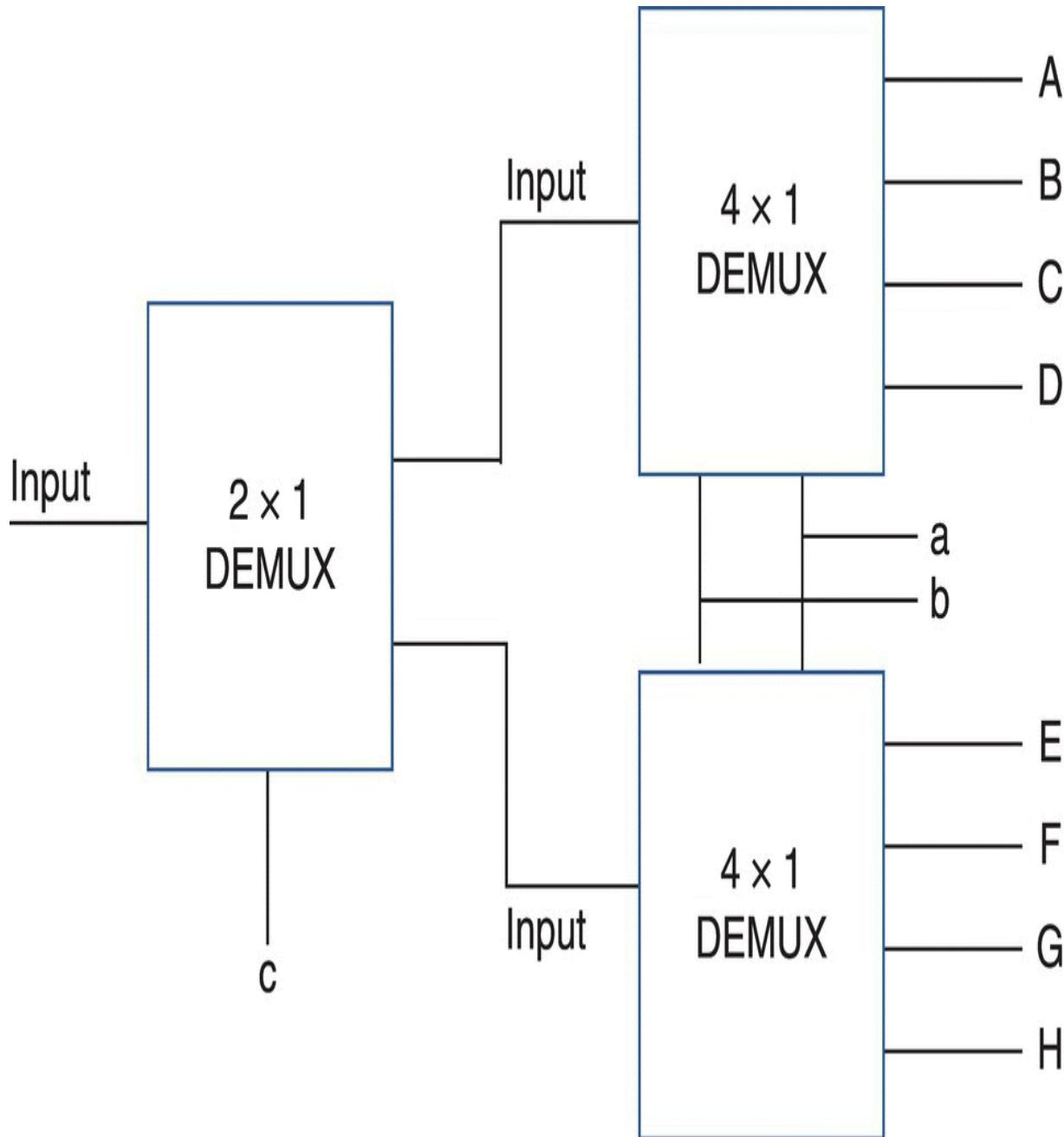

[Figure 12.6 8 to 1 DEMUX constructed using smaller size DEMUXs.](#)

[Figure 12.7 The register is composed of many latches with the non-asterisk o...](#)

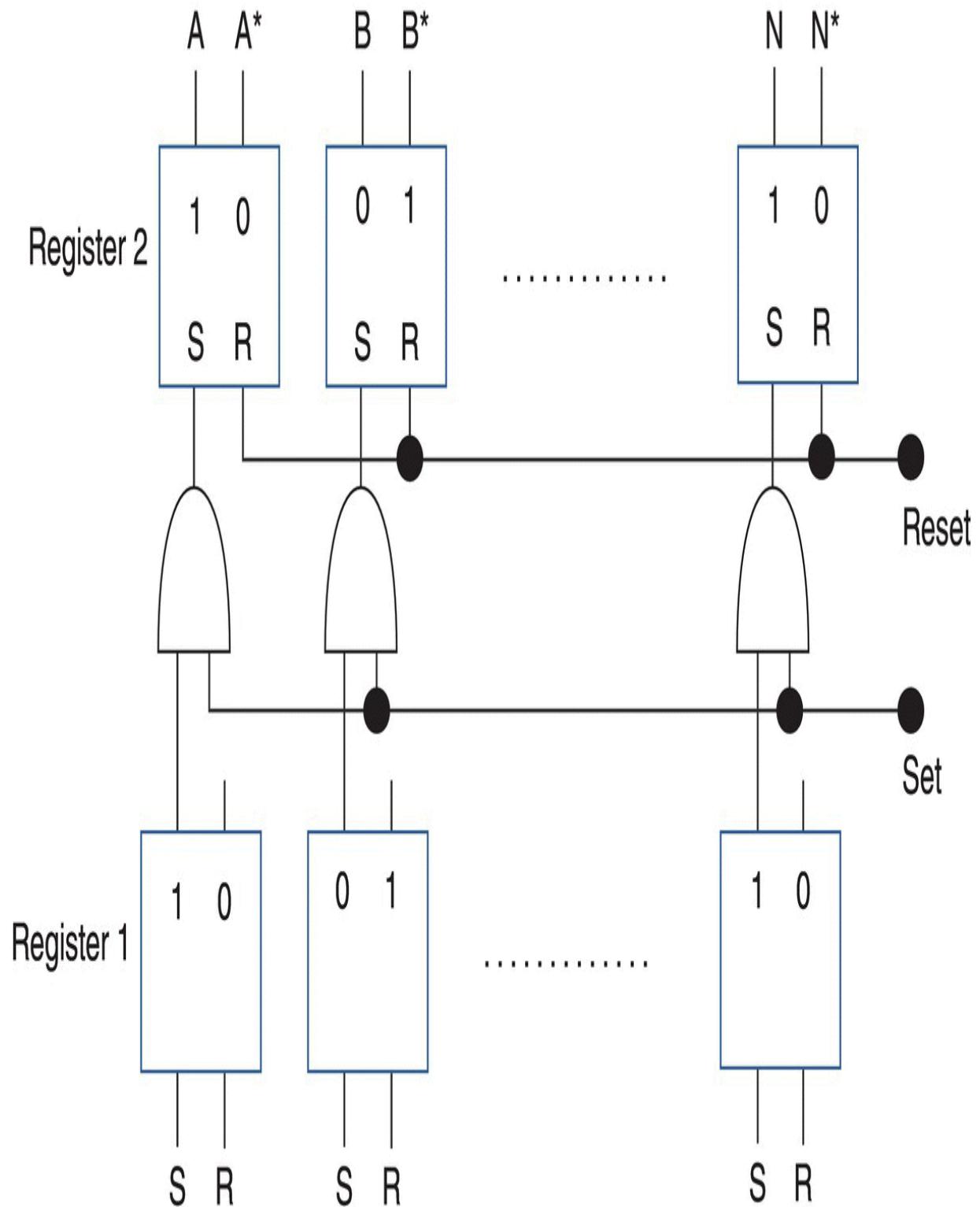

[Figure 12.8 To transfer data from register 1 to register 2, we turn ON the s...](#)

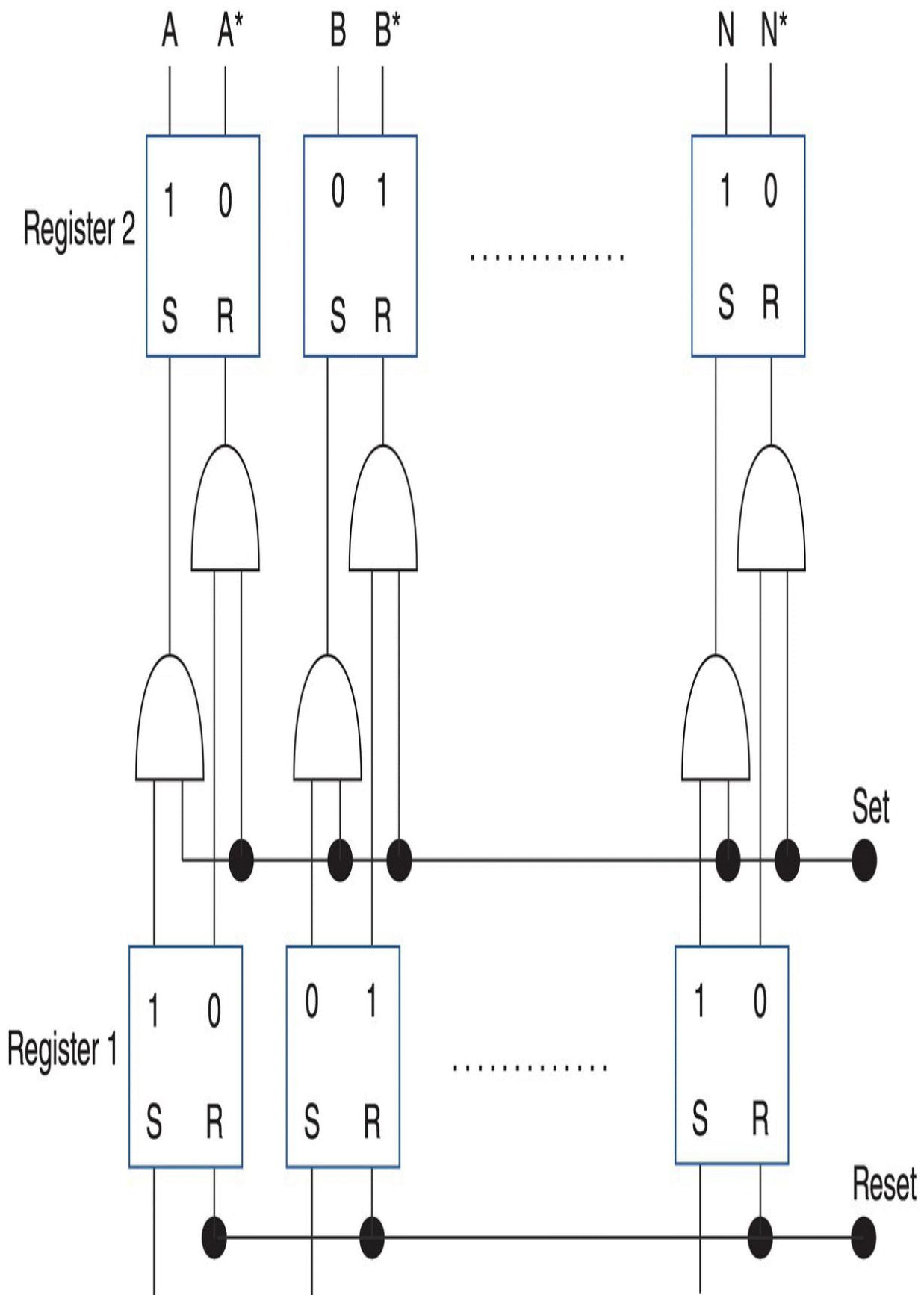

[Figure 12.9 We can transfer the data faster from one register to another by ...](#)

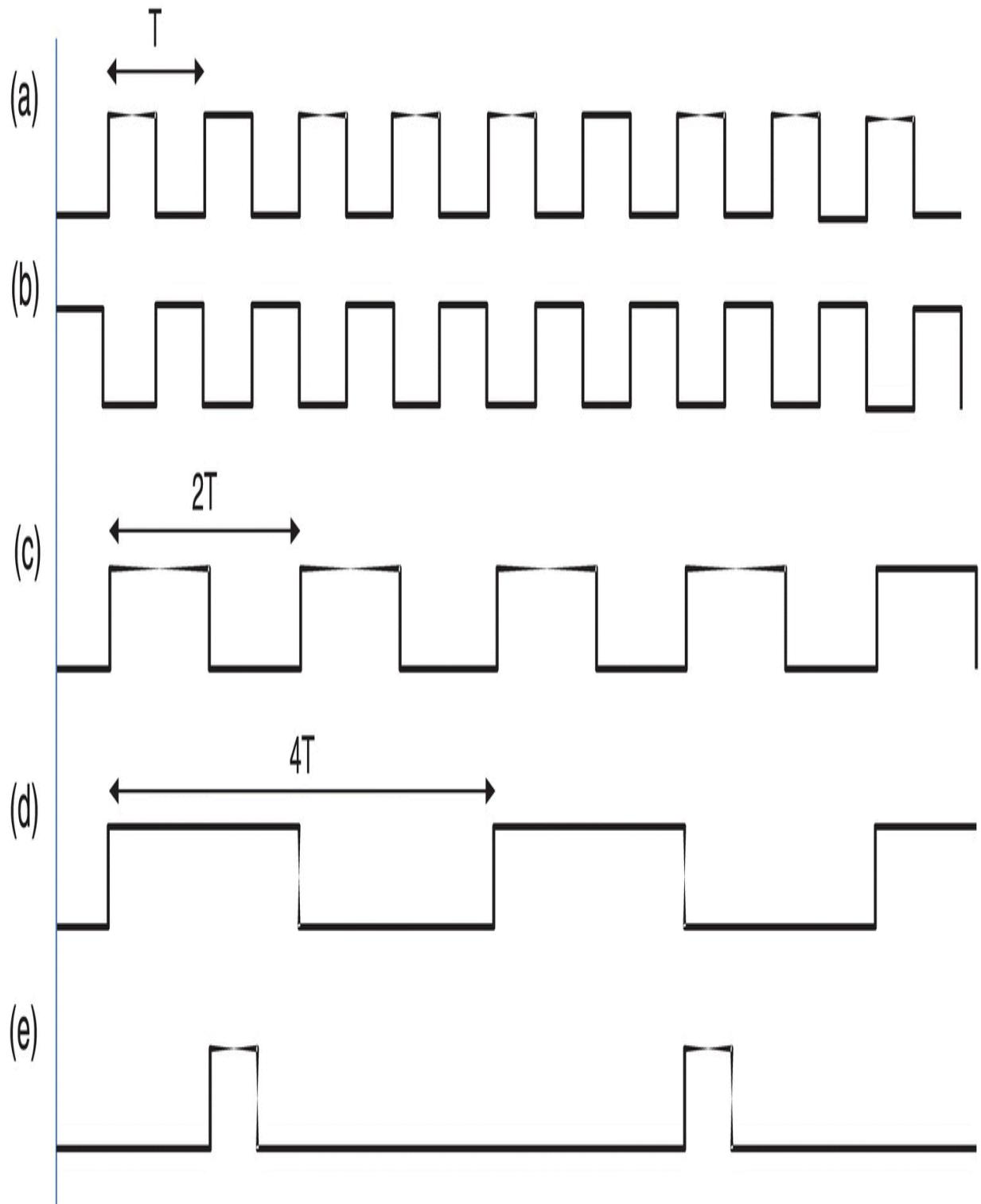

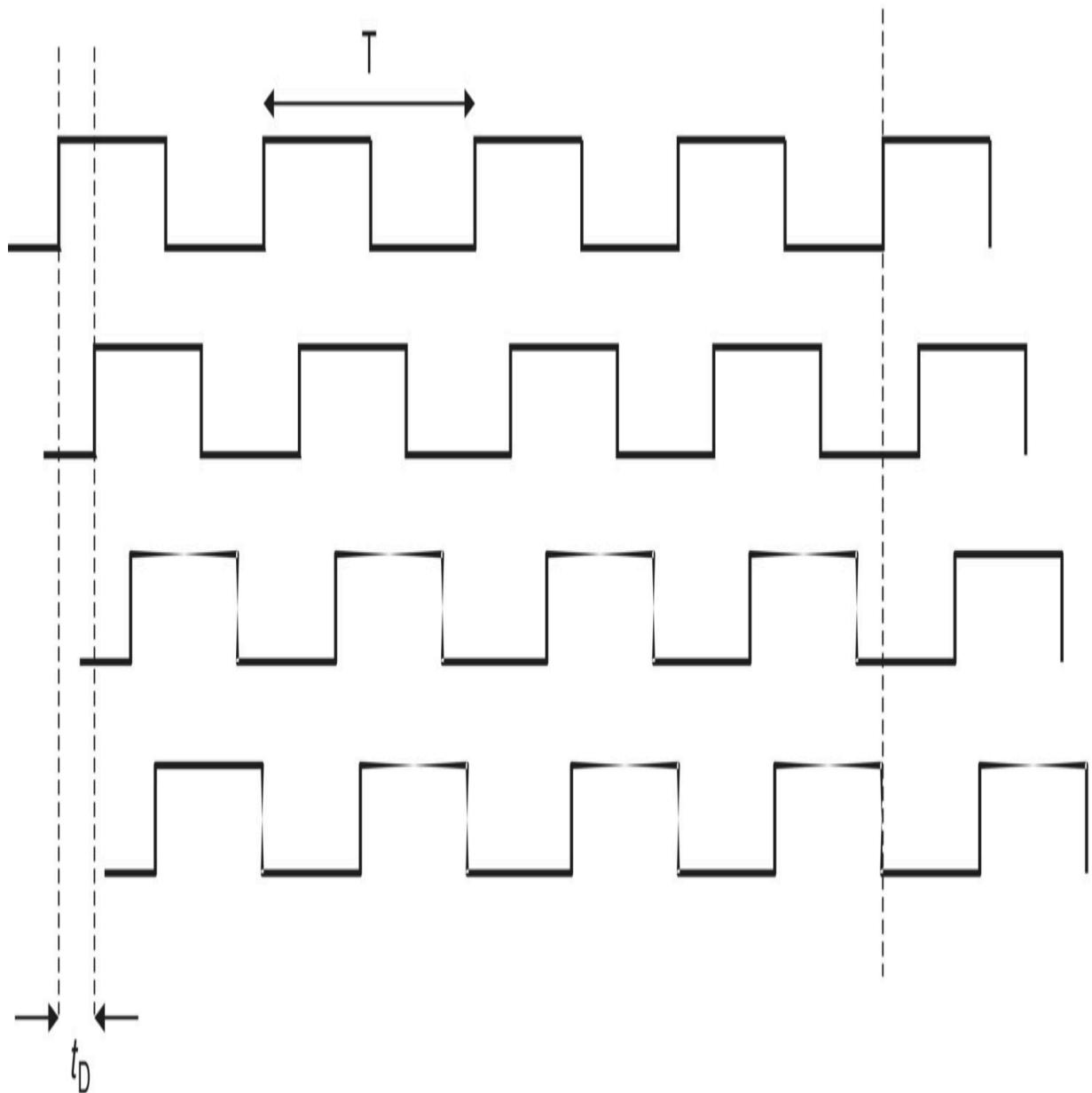

[Figure 12.10 Many waveforms can be generated from the main system clock, the...](#)

[Figure 12.11 As waveforms move across the electronic system, there are timin...](#)

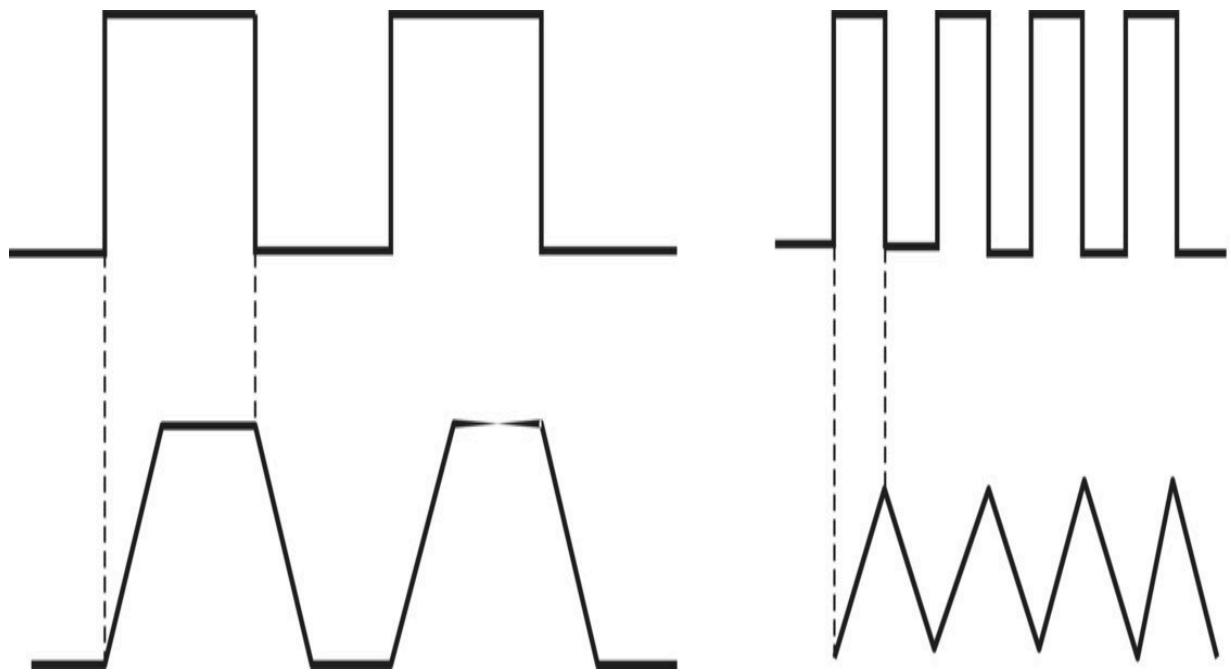

[Figure 12.12 The rise and fall times of pulses limit the speed of the electr...](#)

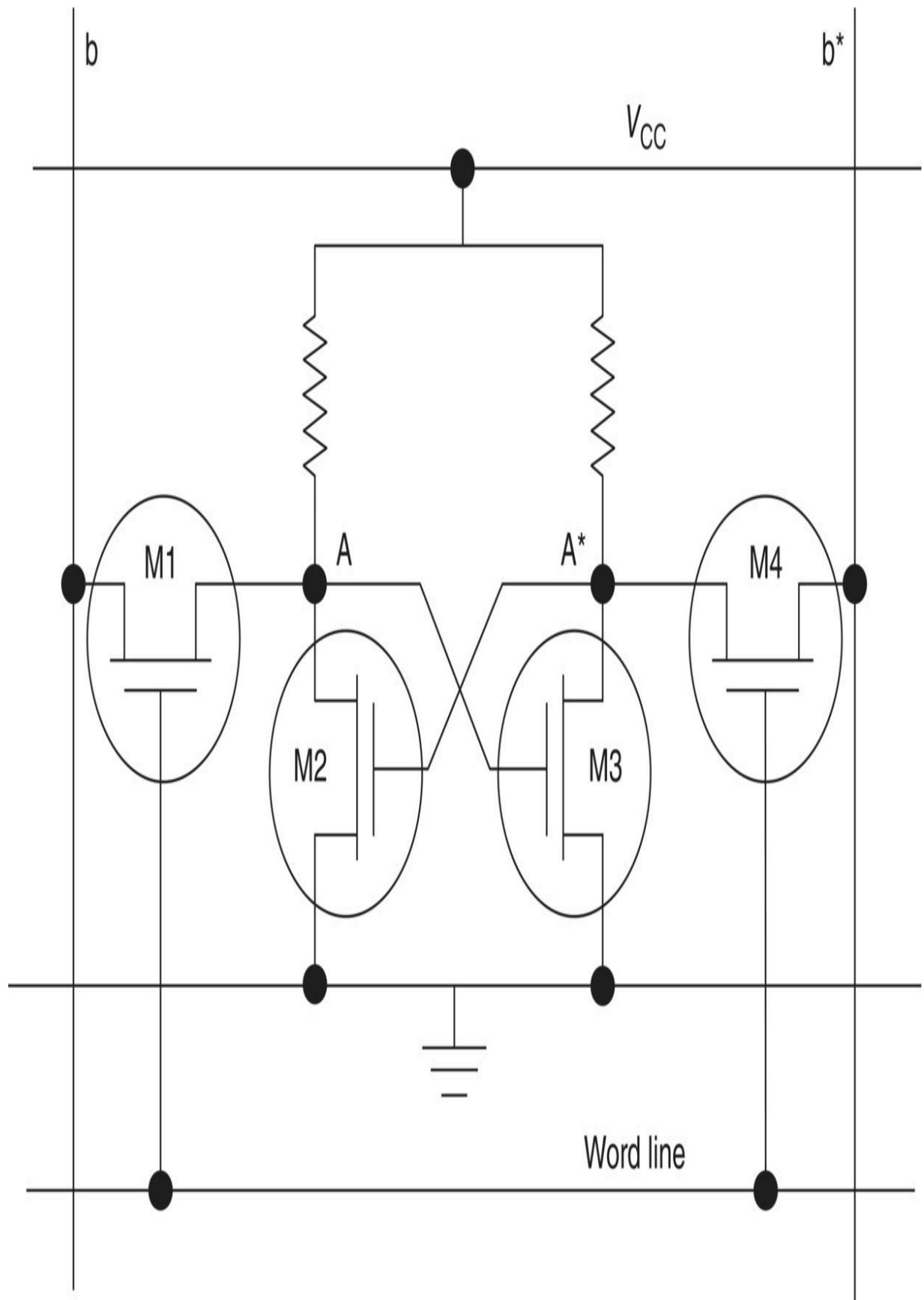

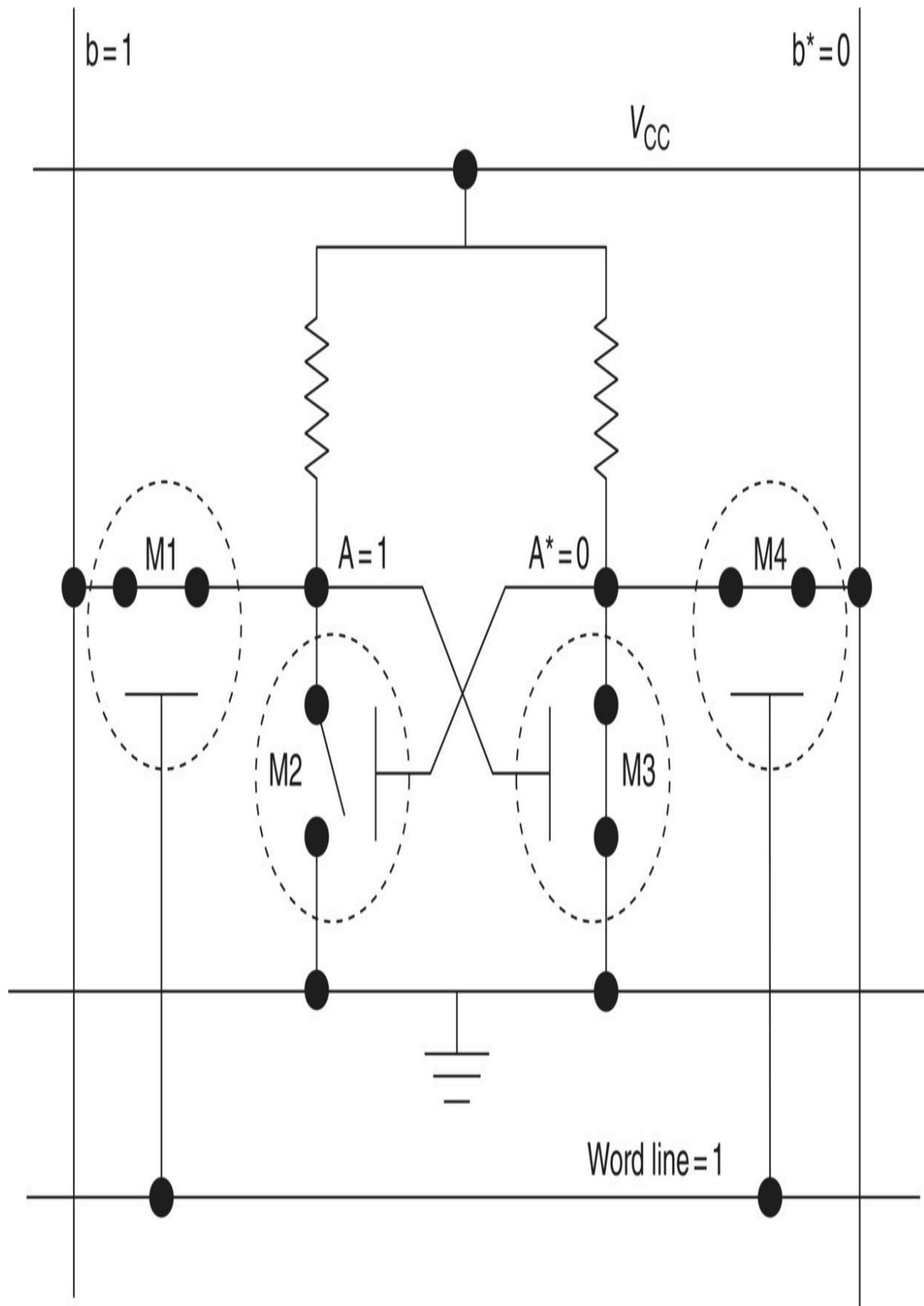

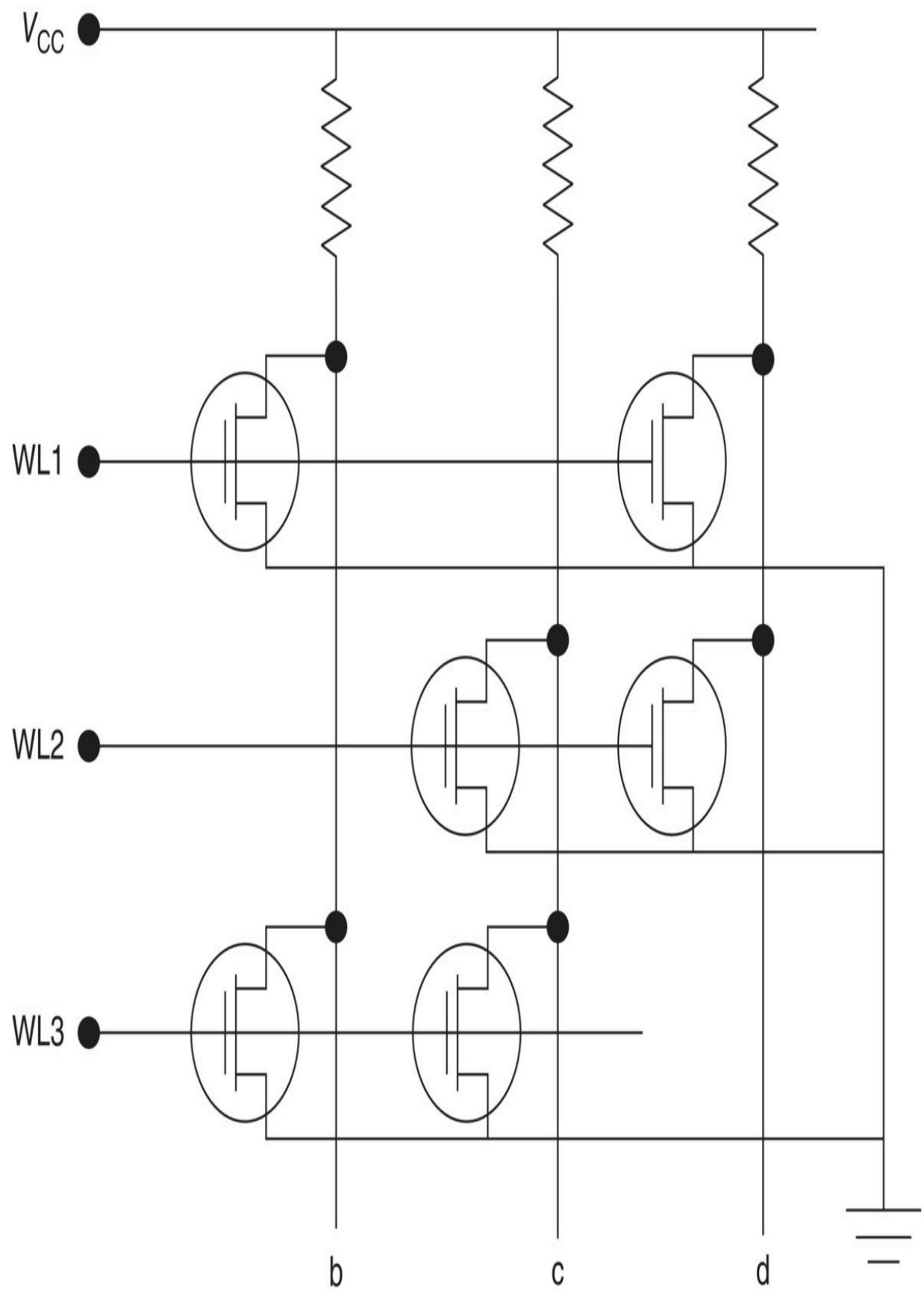

[Figure 12.13 A typical memory unit cell consists of a flip-flop in the cente...](#)

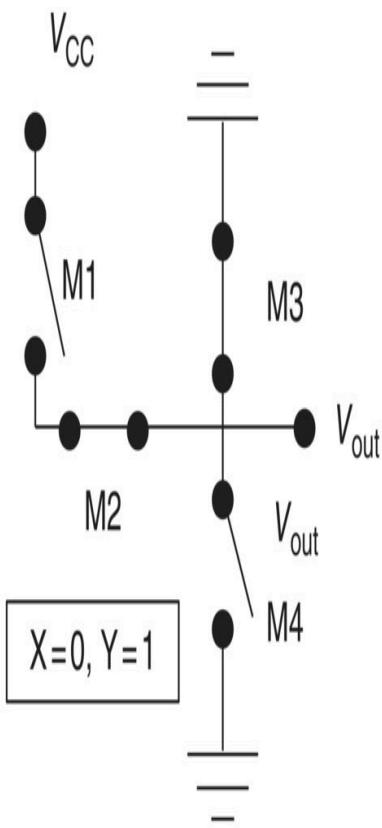

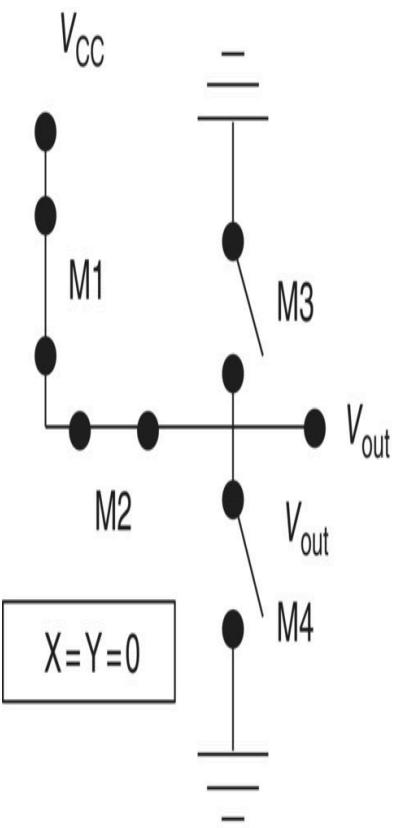

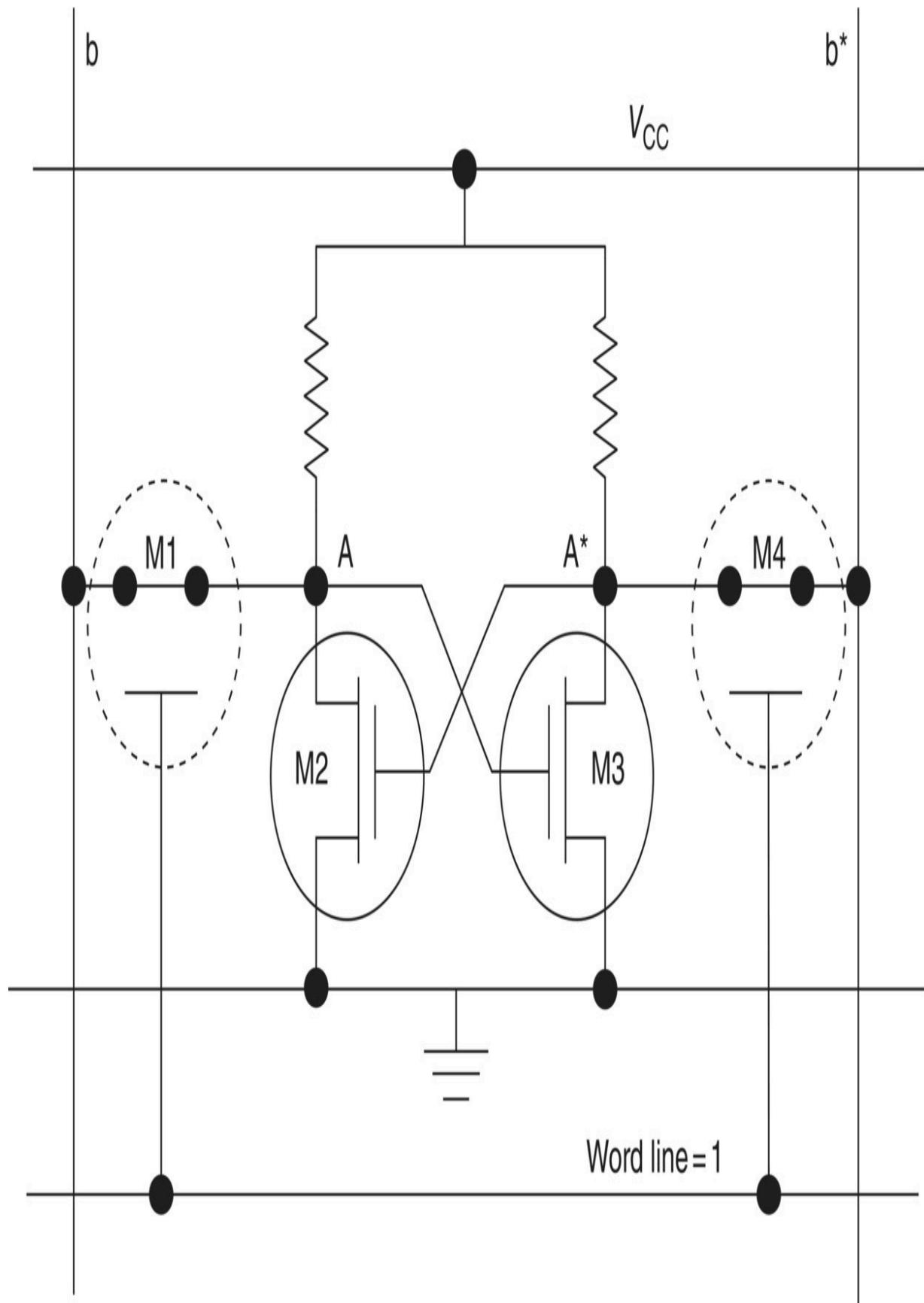

[Figure 12.14 When the word line is 1, the CMOSs M1 and M4 are shorted, and t....](#)

[Figure 12.15 The CMOS in Figures 12.13 and 12.14 are replaced by switches. W...](#)

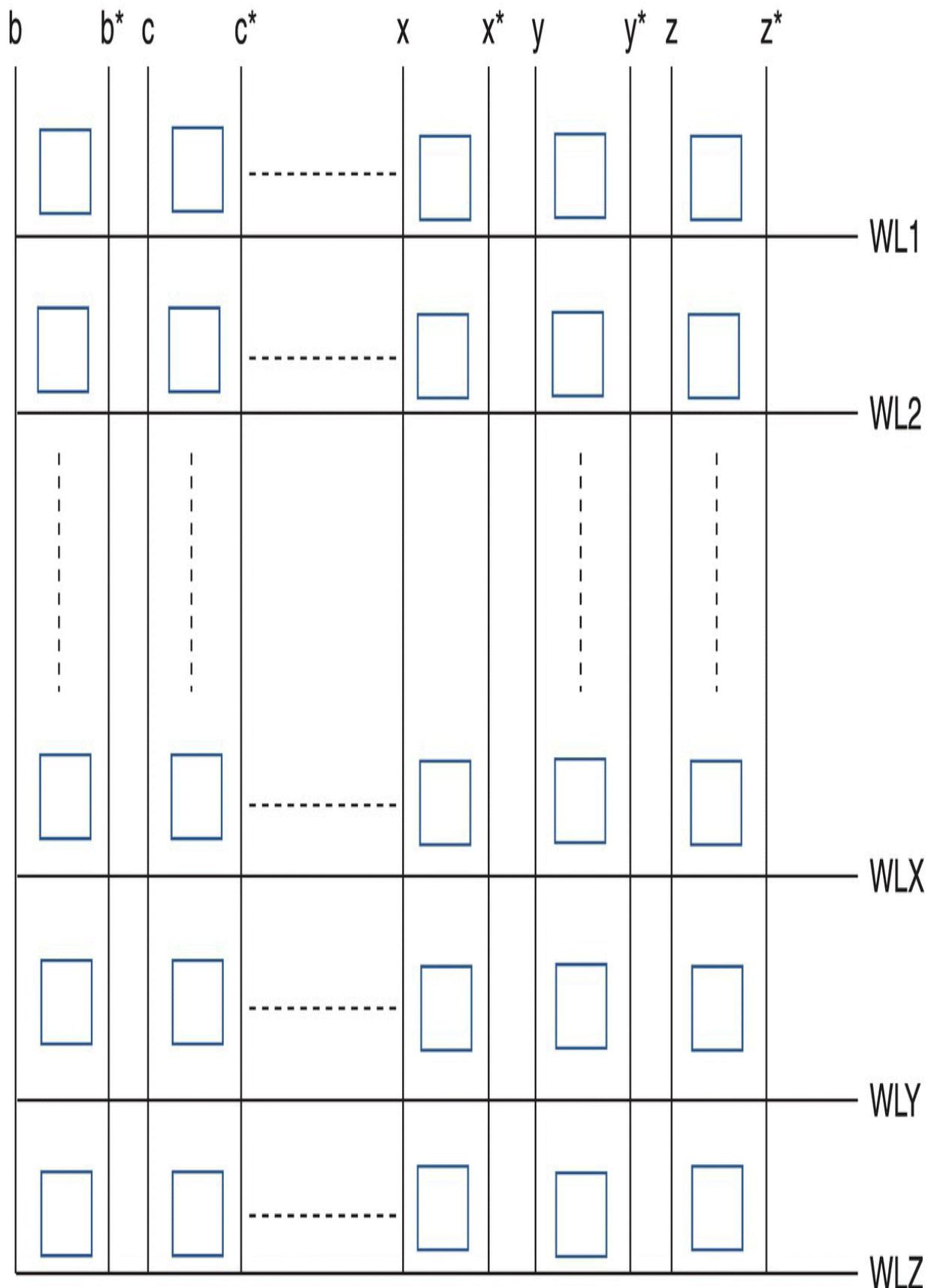

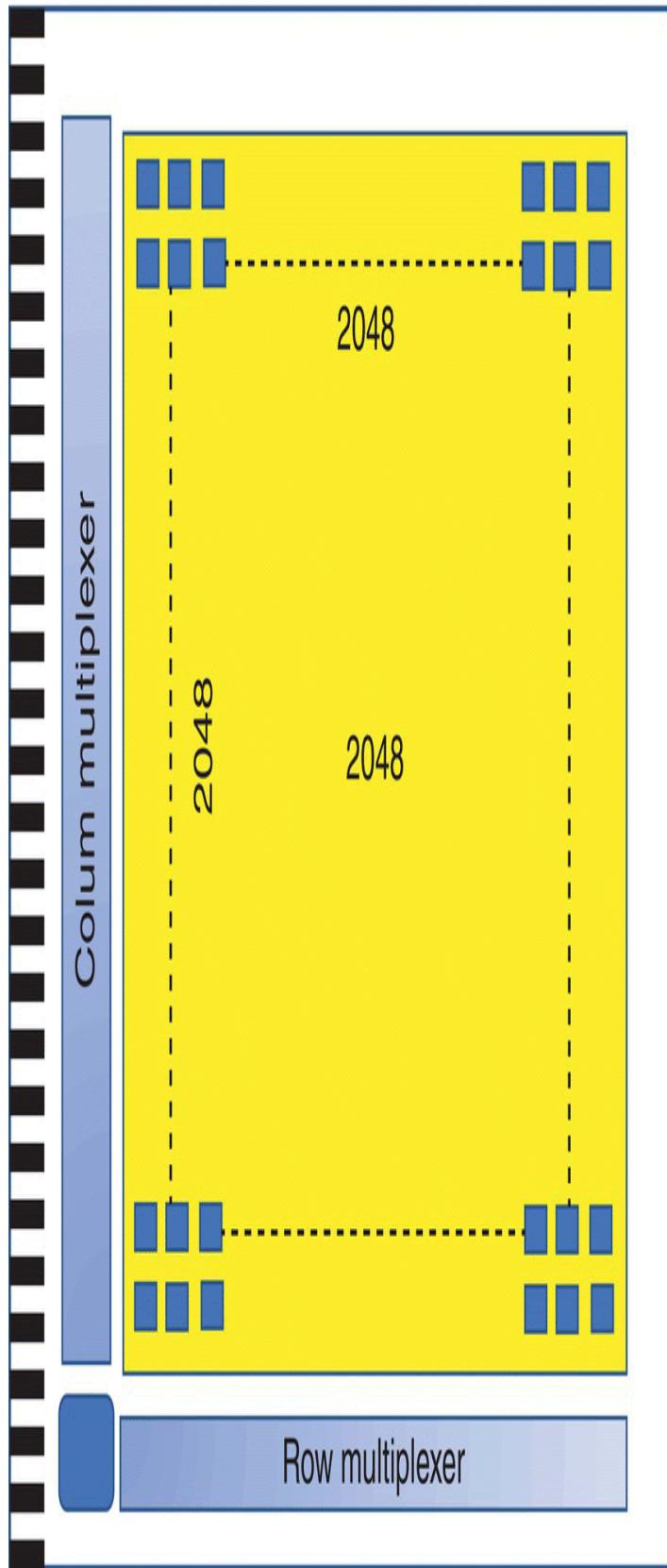

[Figure 12.16 A memory chip architecture consists of a matrix of unit cells \(...](#)

[Figure 12.17 The array of DRAM cells is addressed by a single input line \(ho...](#)

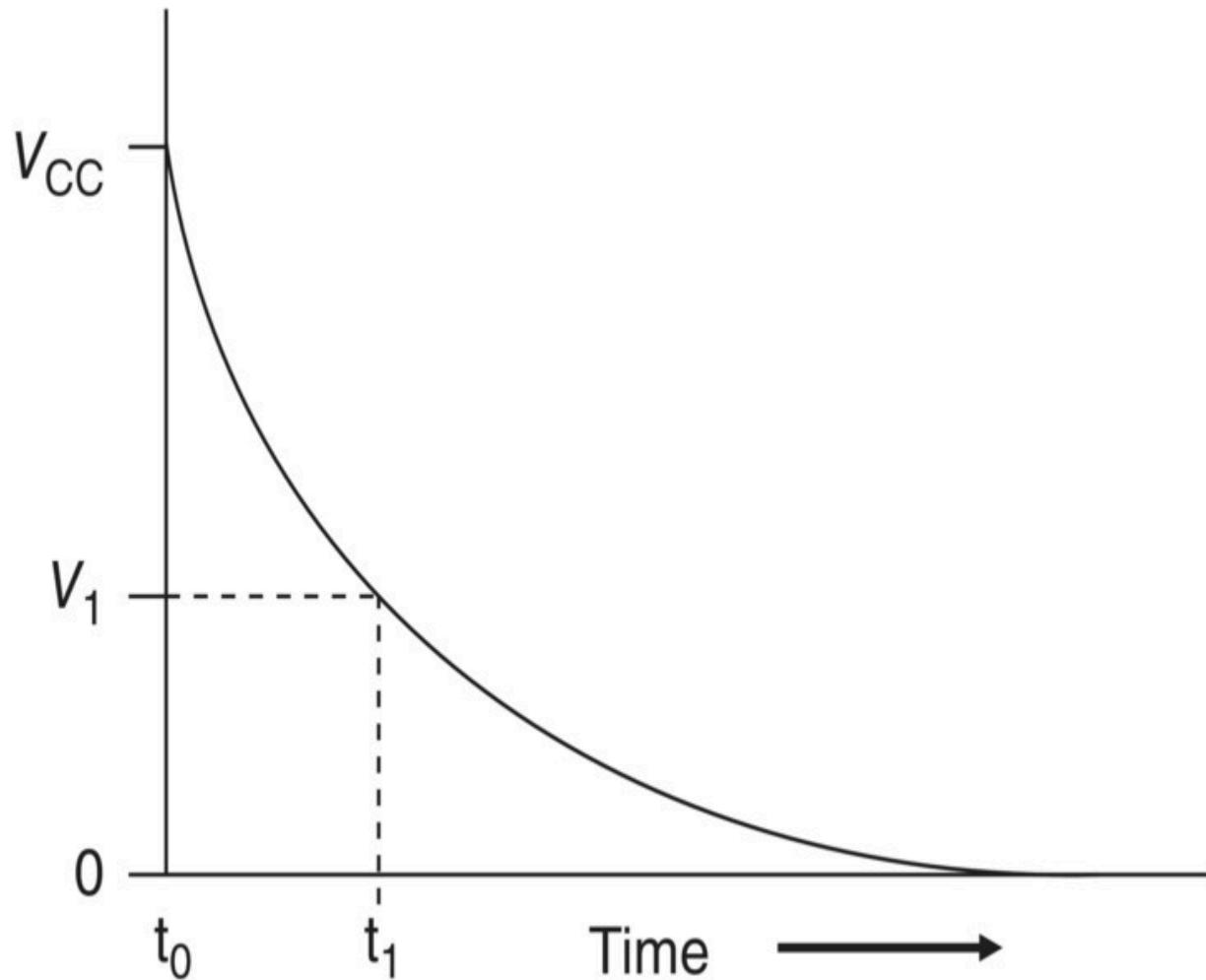

[Figure 12.18 The capacitor charges initially to the full voltage,  \$V\_{CC}\$ , but i...](#)

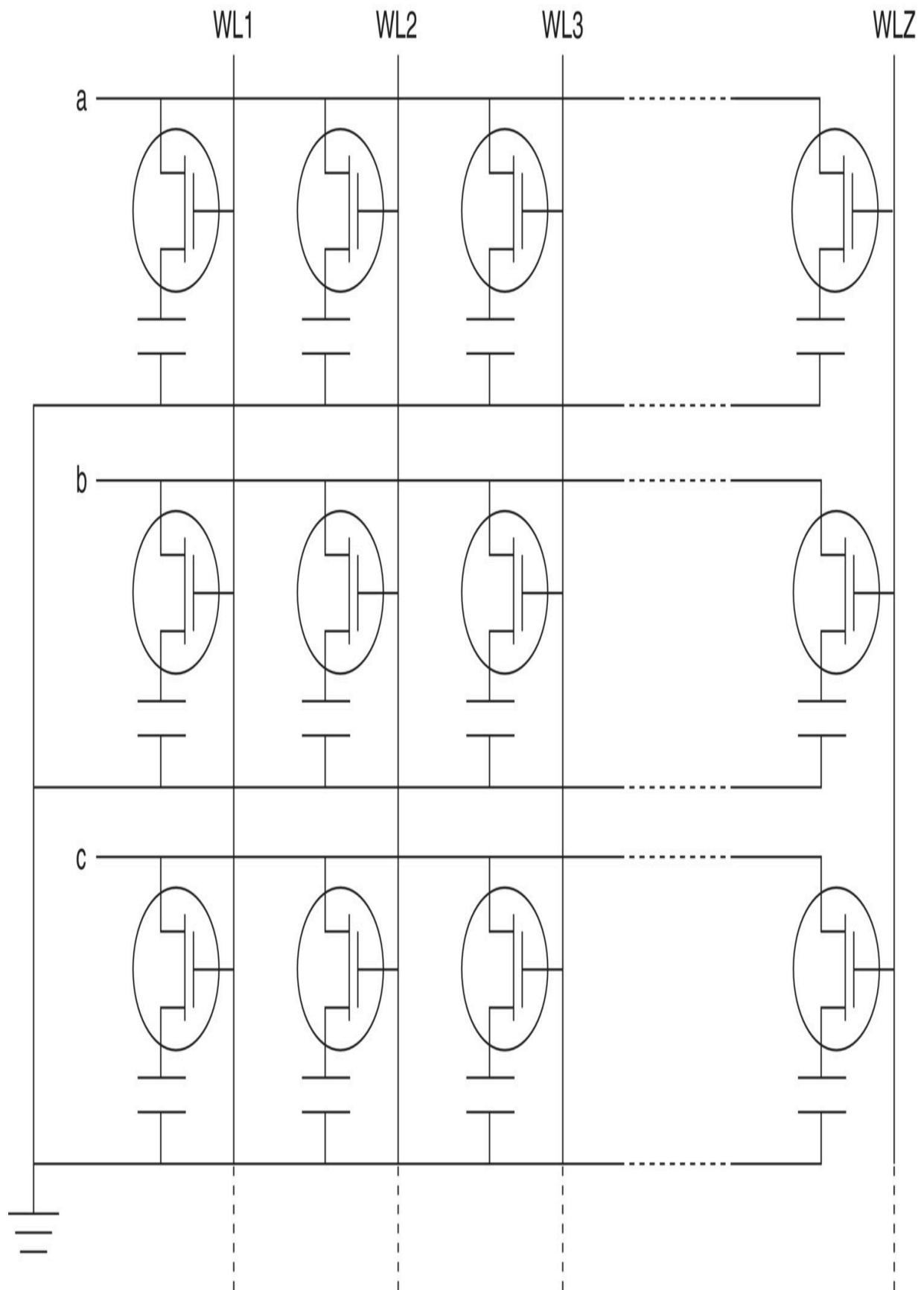

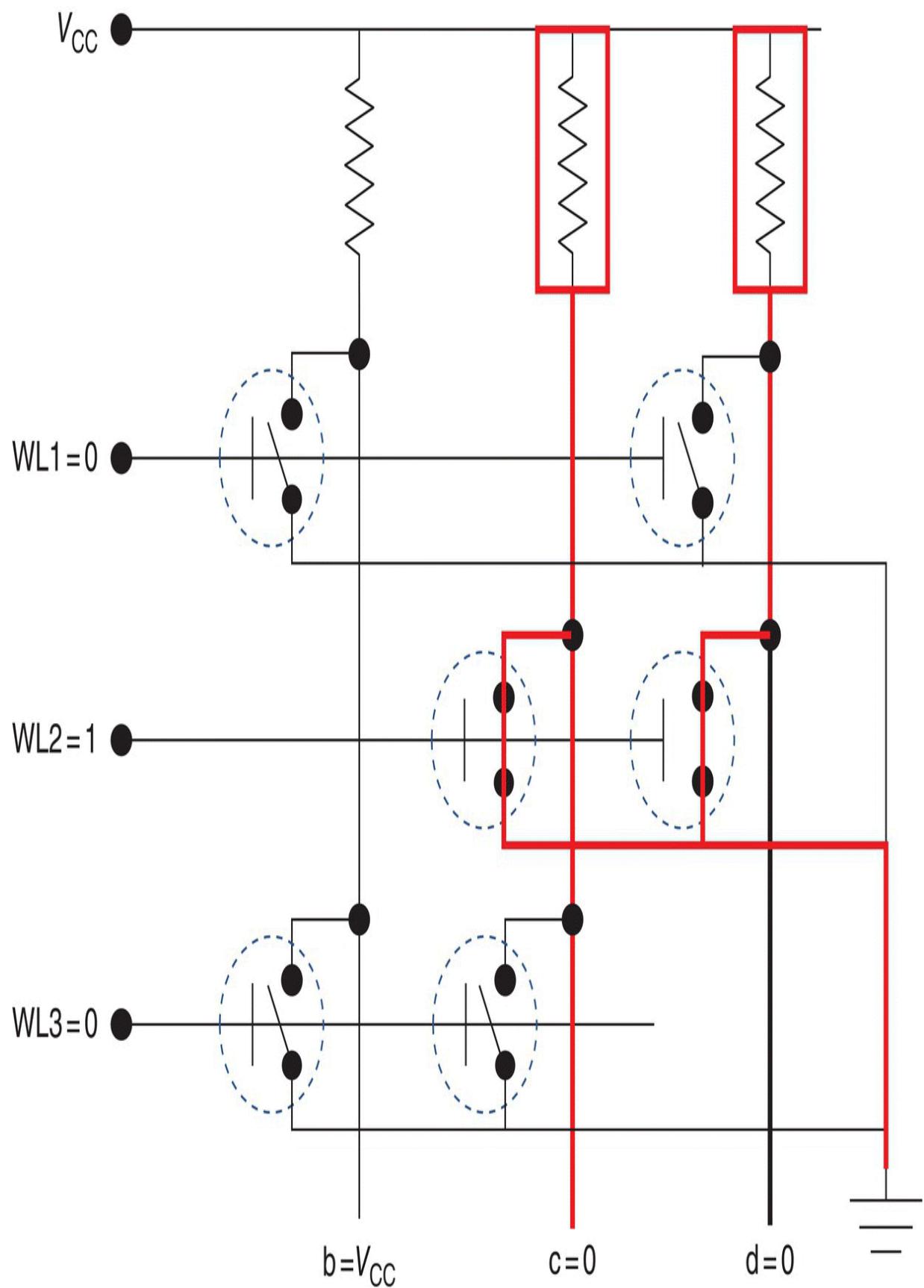

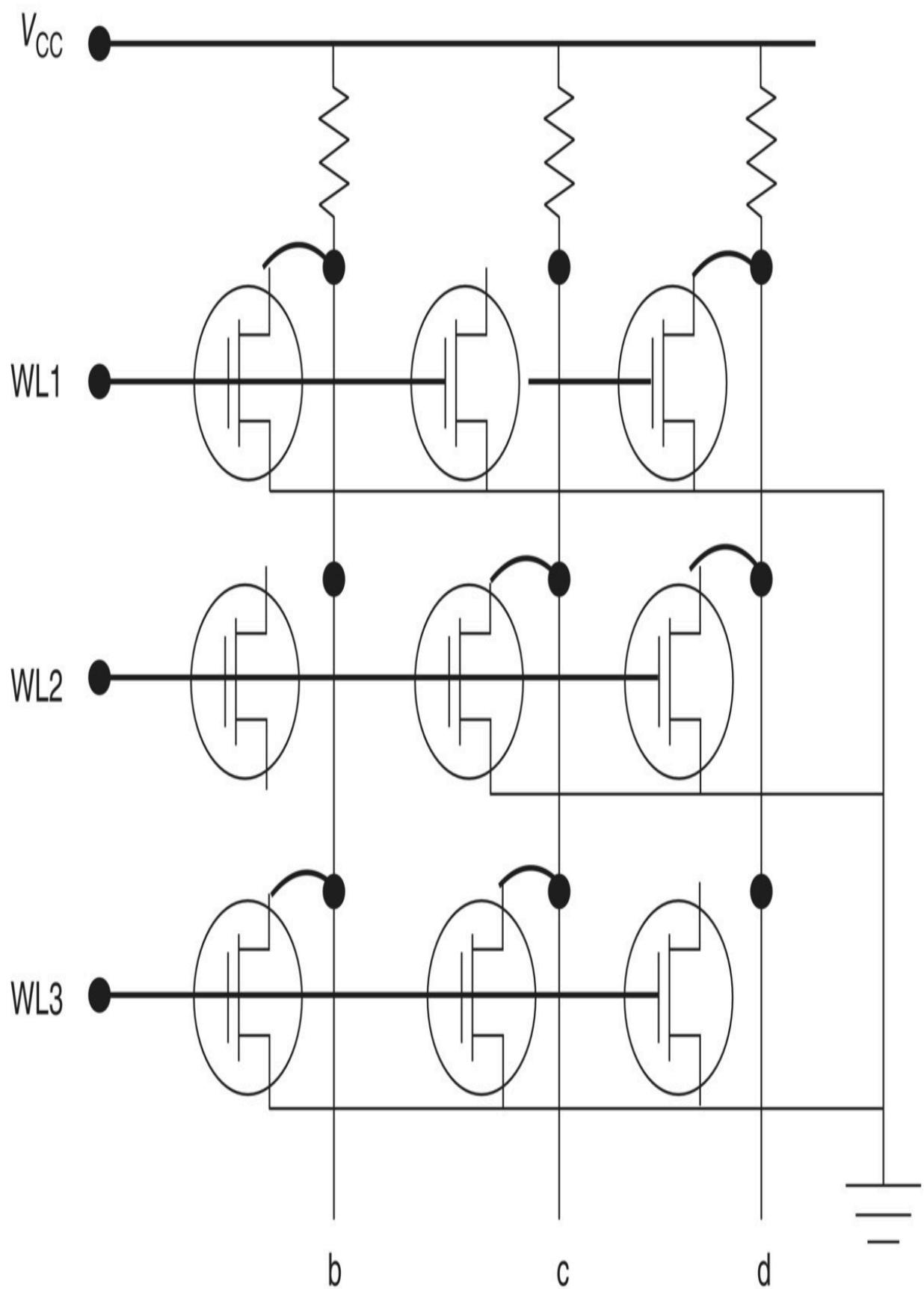

[Figure 12.19 A ROM consists of CMOS arranged in such a way as to ensure that...](#)

[Figure 12.20 Switch representation of the ROM when one of the word lines, WL...](#)

[Figure 12.21 A PROM has fuses connecting the sources to the bit lines. These...](#)

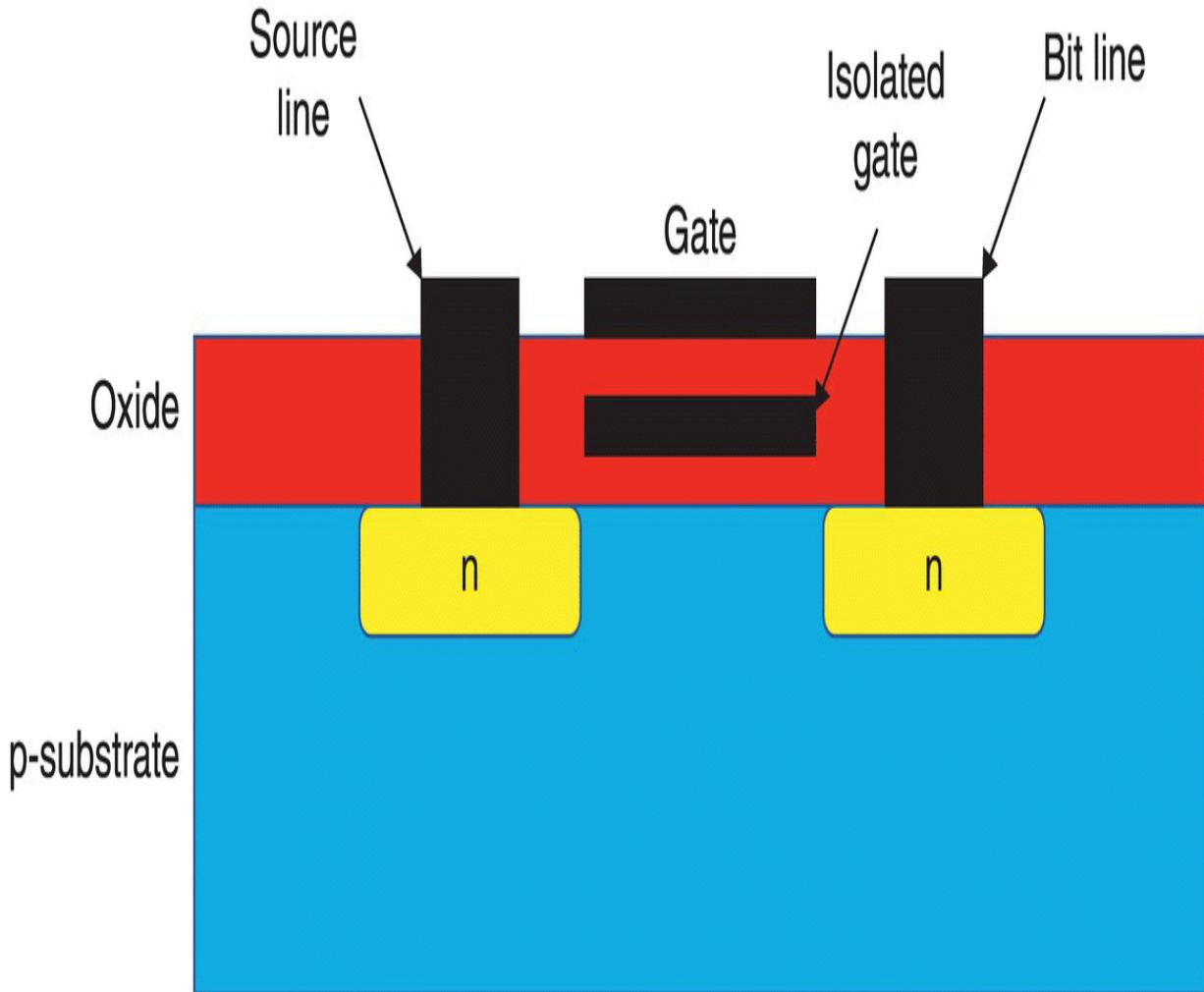

[Figure 12.22 The EPROM consists of a regular MOSFET with a completely isolat...](#)

[Figure 12.23 Implementation of a 2 to 1 MUX using three NANDs and one NOT mo...](#)

Chapter 13

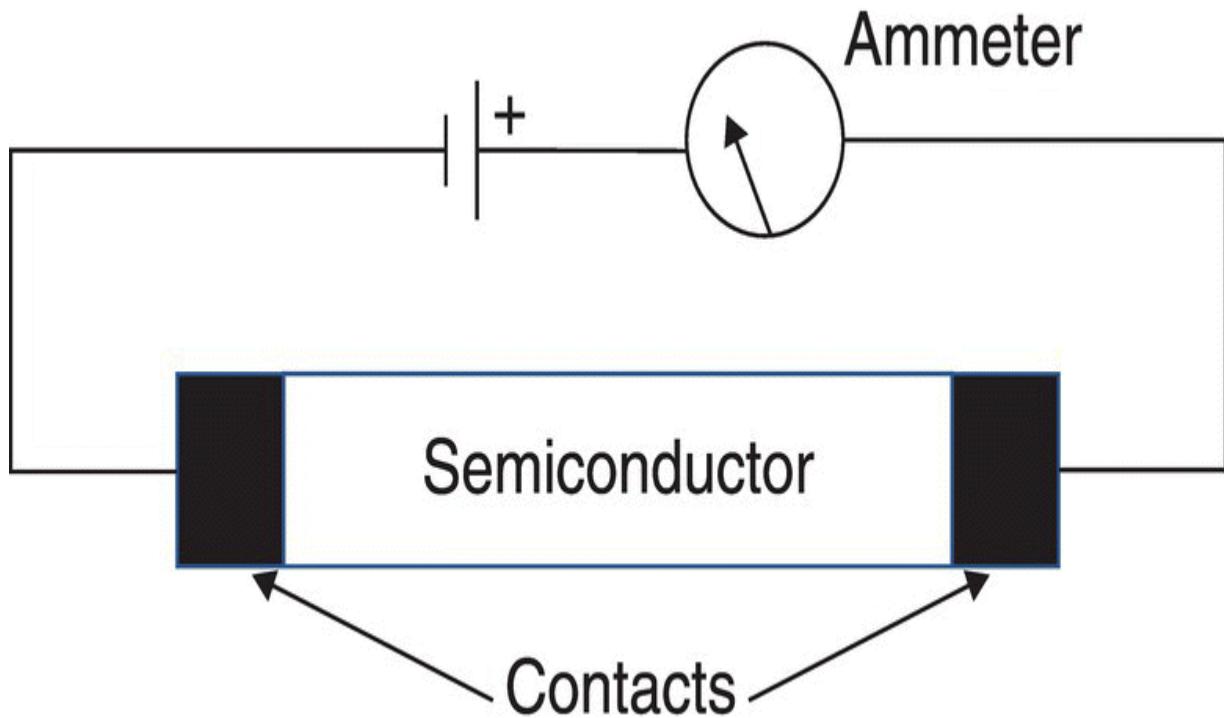

[Figure 13.1 A simple photoconductor consists of a semiconductor with two con...](#)

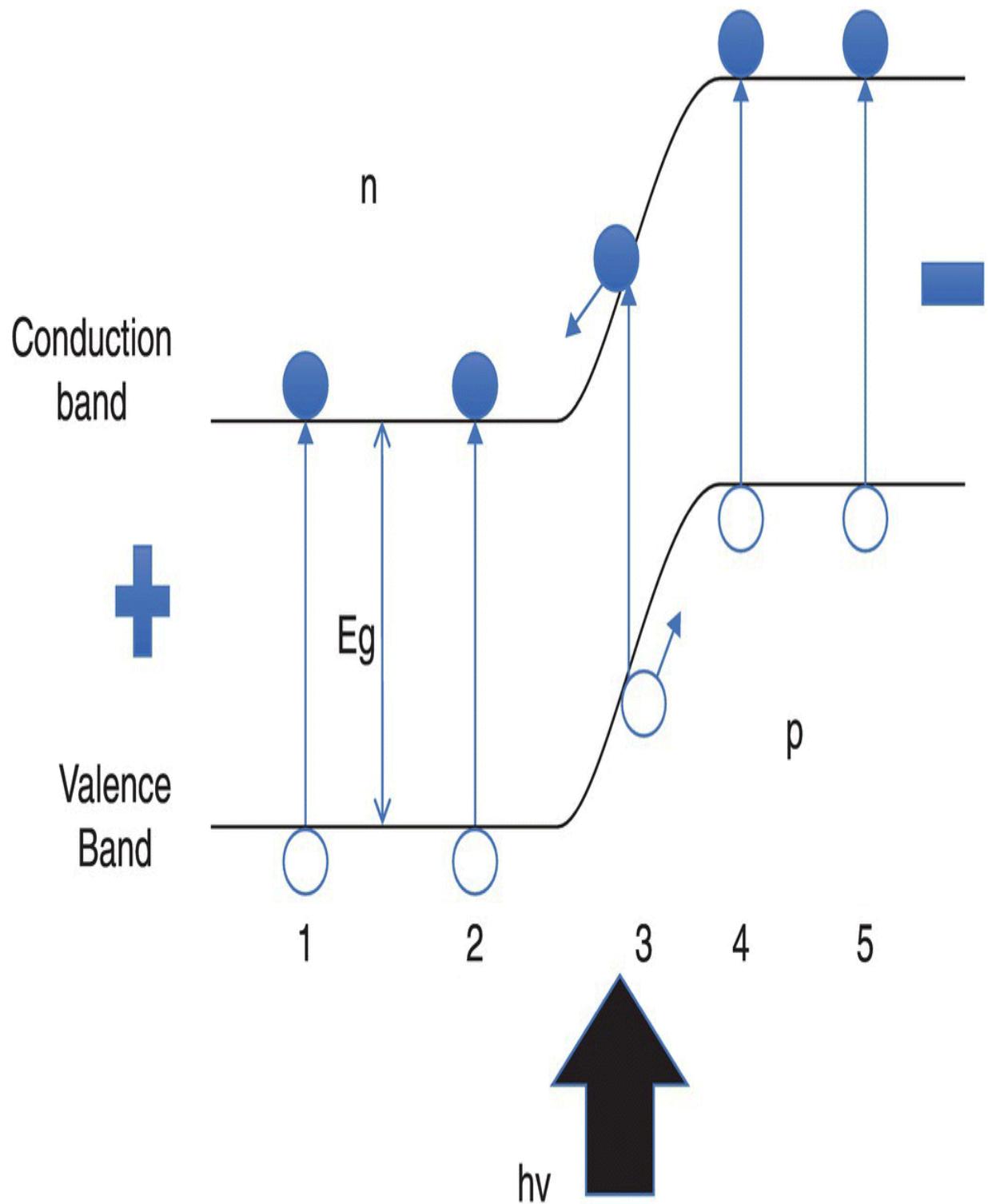

[Figure 13.2 Radiation shining on a reversed-biased diode creates an electron...](#)

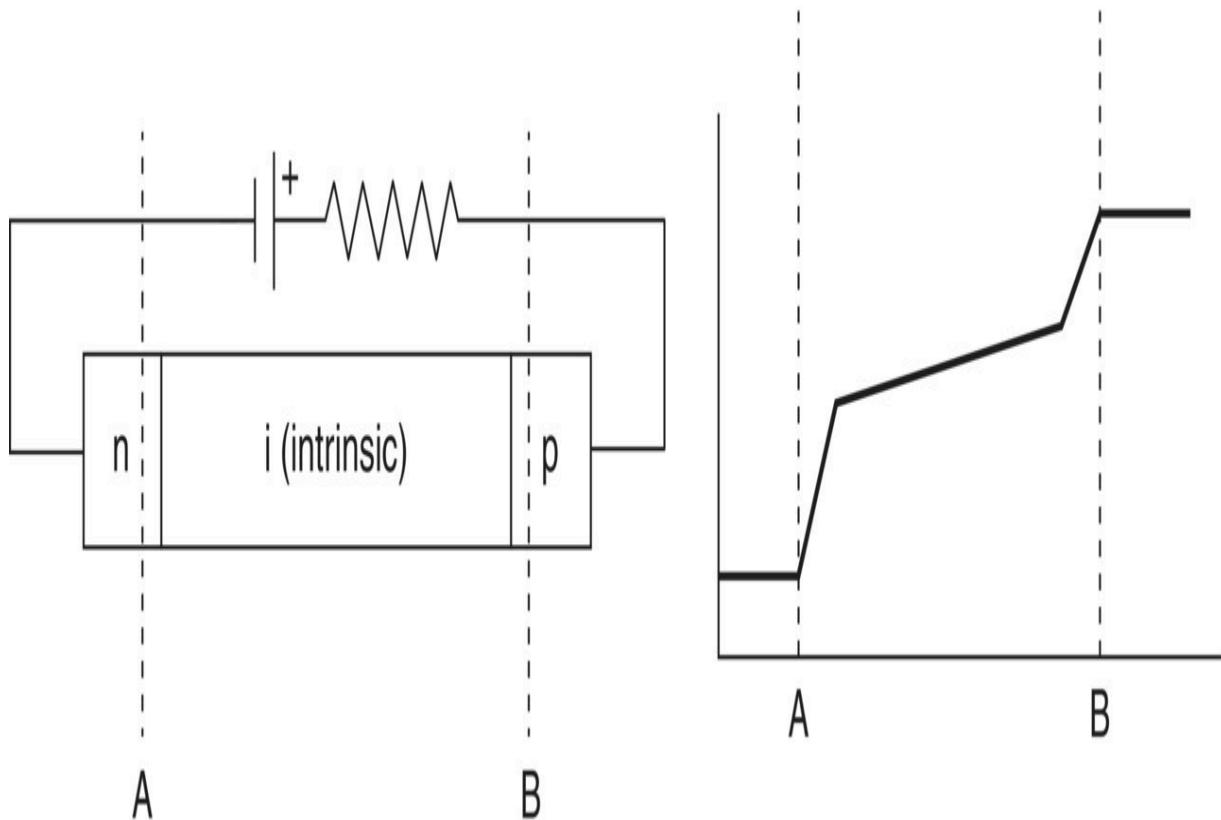

[Figure 13.3 The PIN diode structure consist of a p- and an n-region separate...](#)

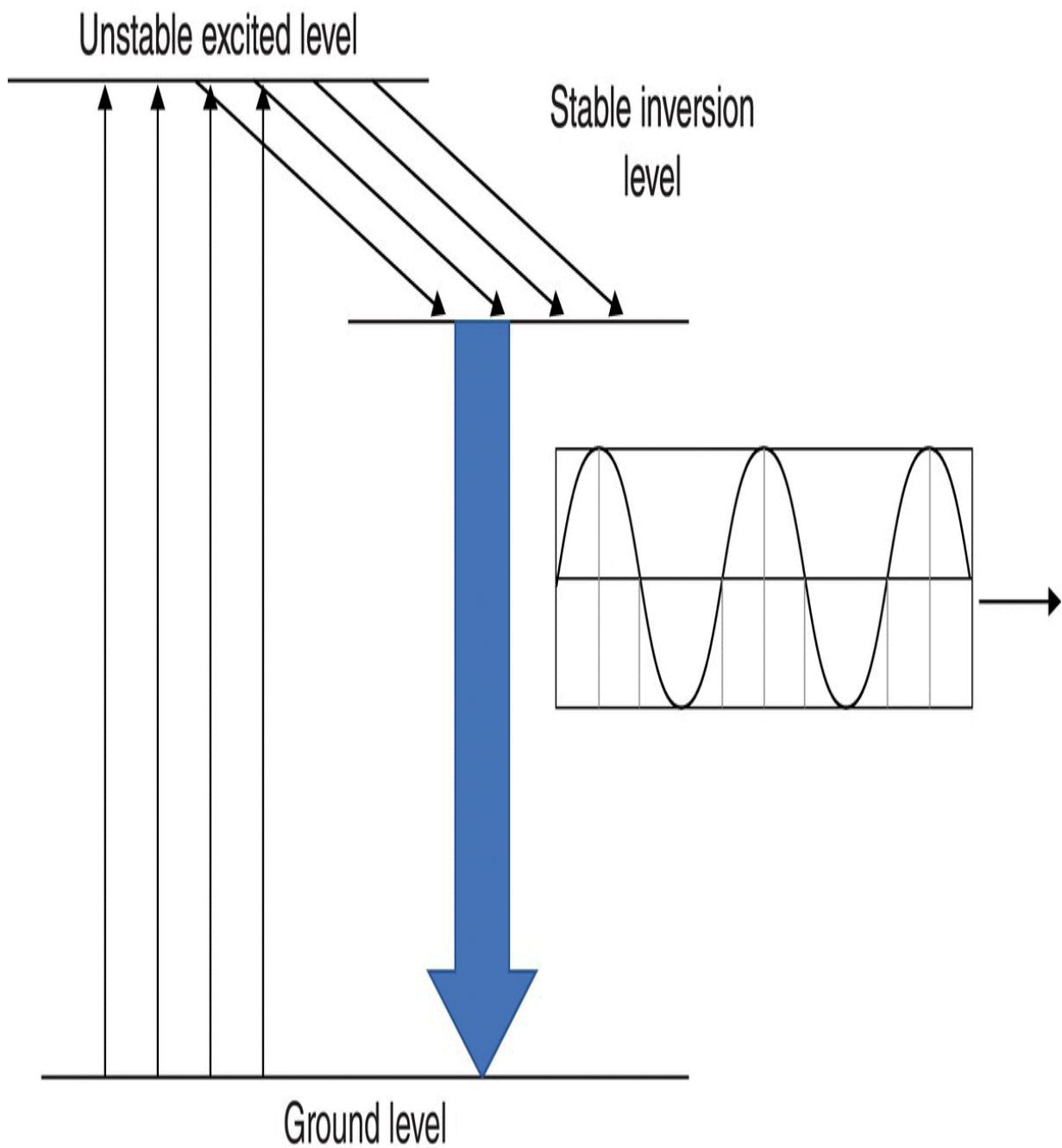

[Figure 13.4 Both MASERs and LASERs work with the idea that electrons that ar...](#)

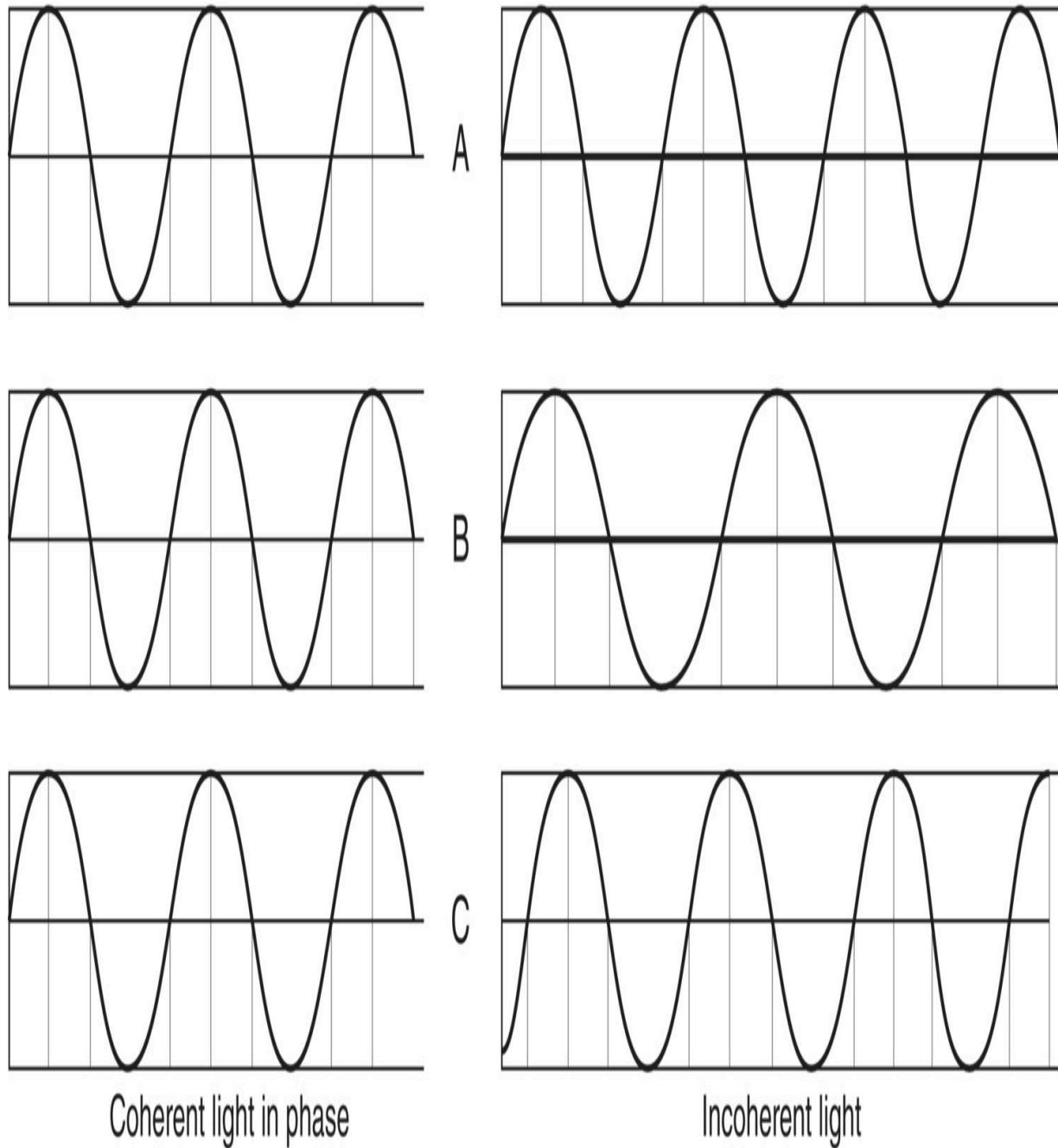

[Figure 13.5 In a coherent light \(left\) all the waves A, B, and C are exactly...](#)

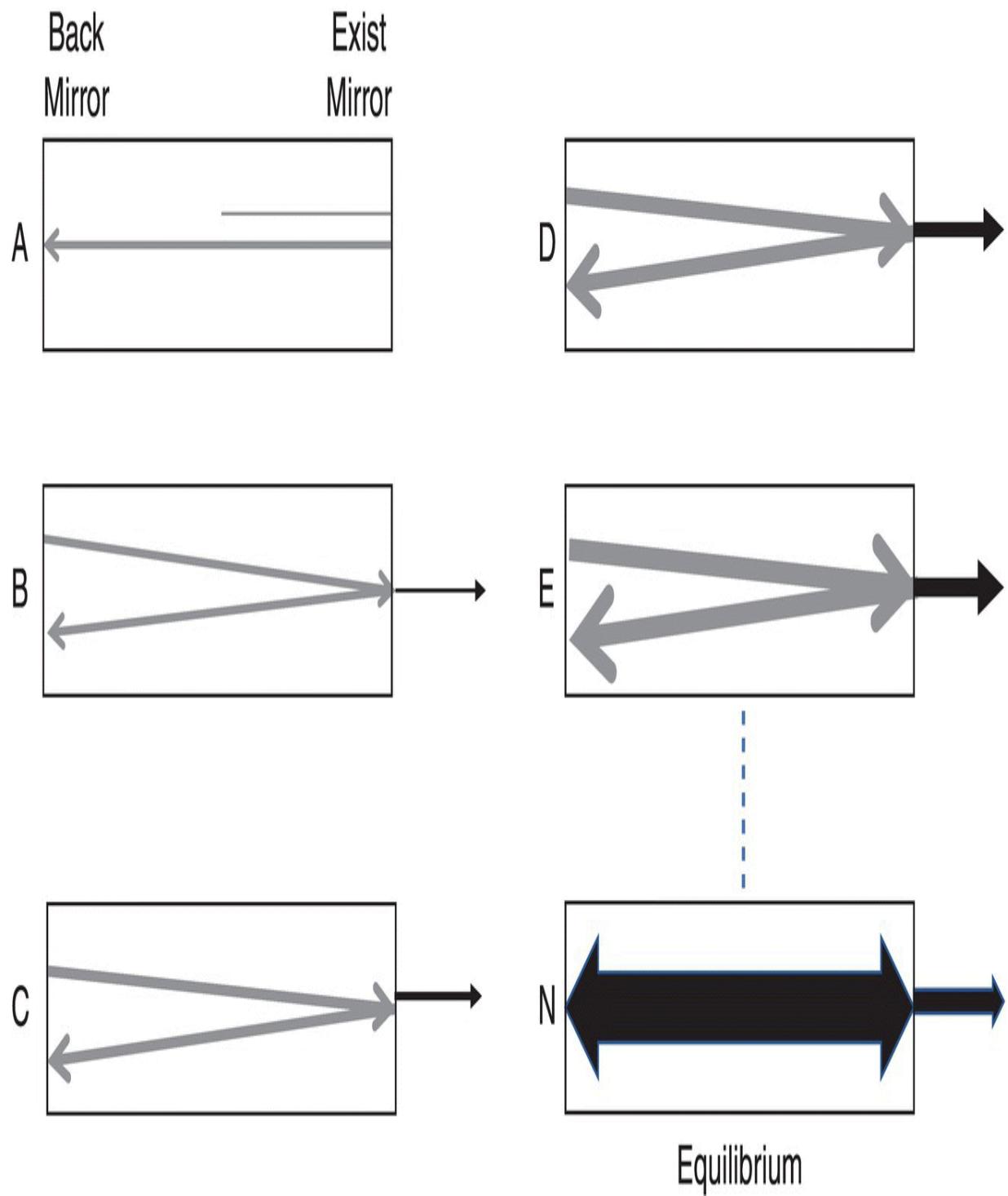

[Figure 13.6 The beam of light bounces inside the cavity with one fully refle...](#)

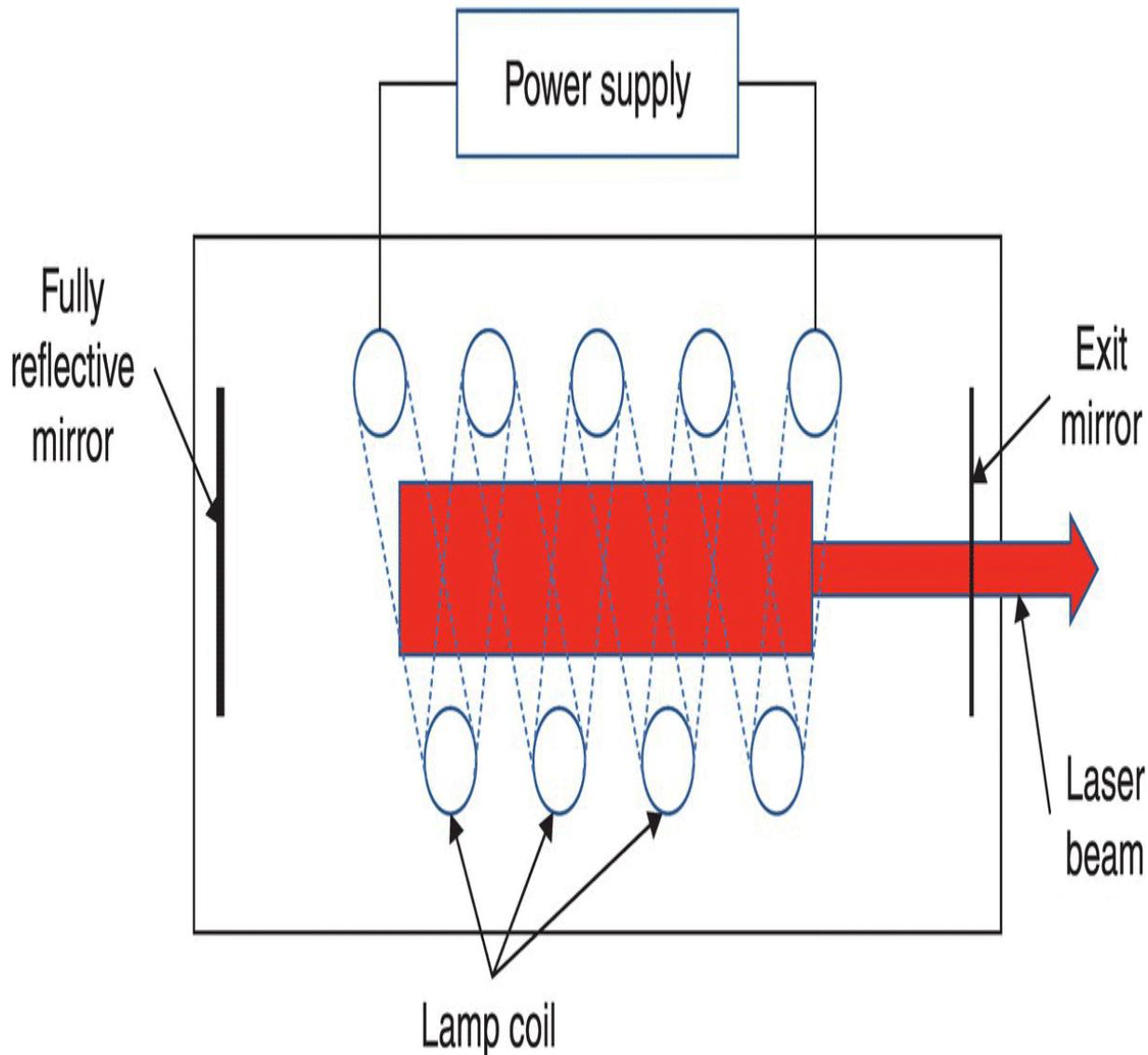

[Figure 13.7 A ruby LASER in a reflective cavity surrounded by a light coil t...](#)

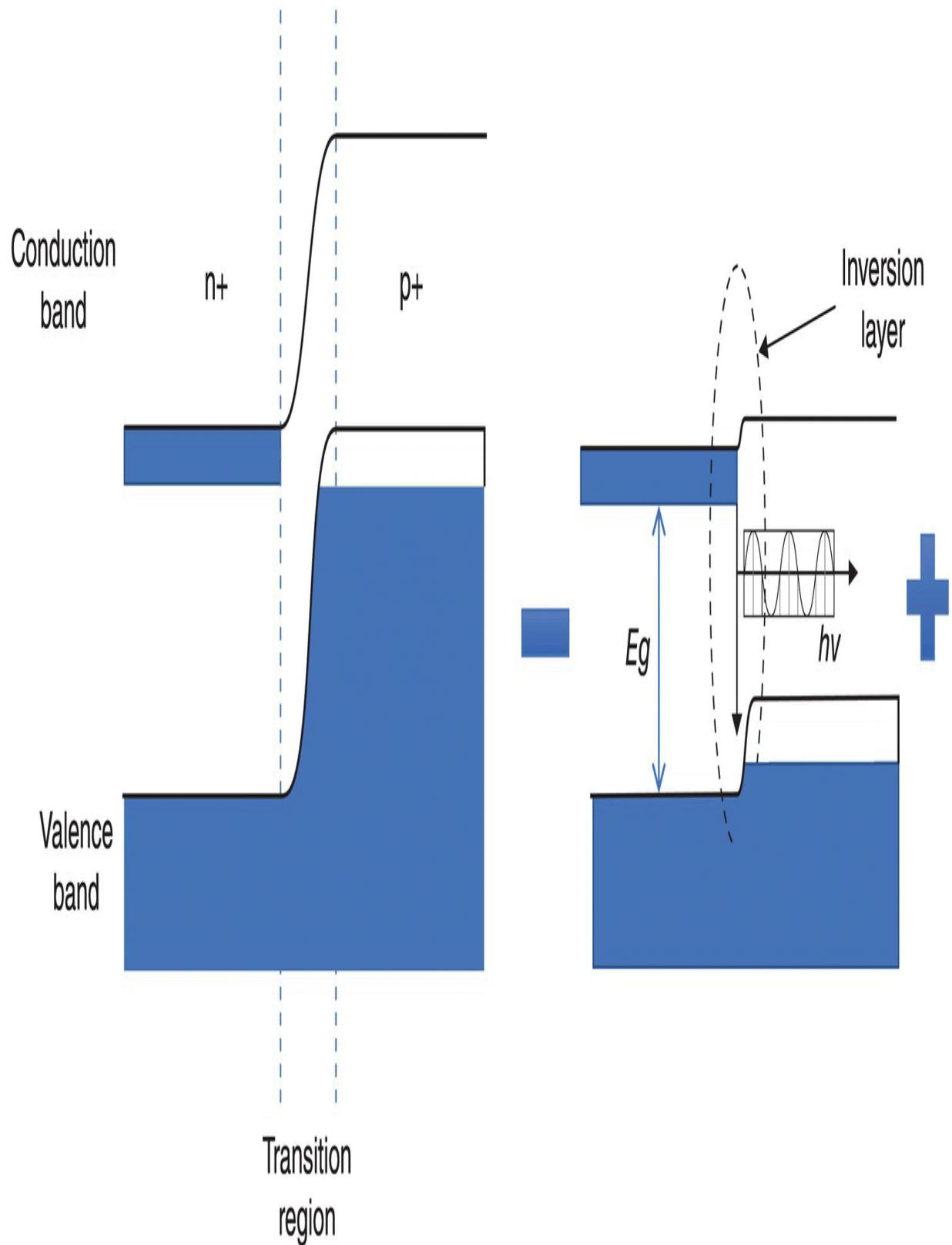

[Figure 13.8 The internal voltage for a degenerate semiconductor diode is lar...](#)

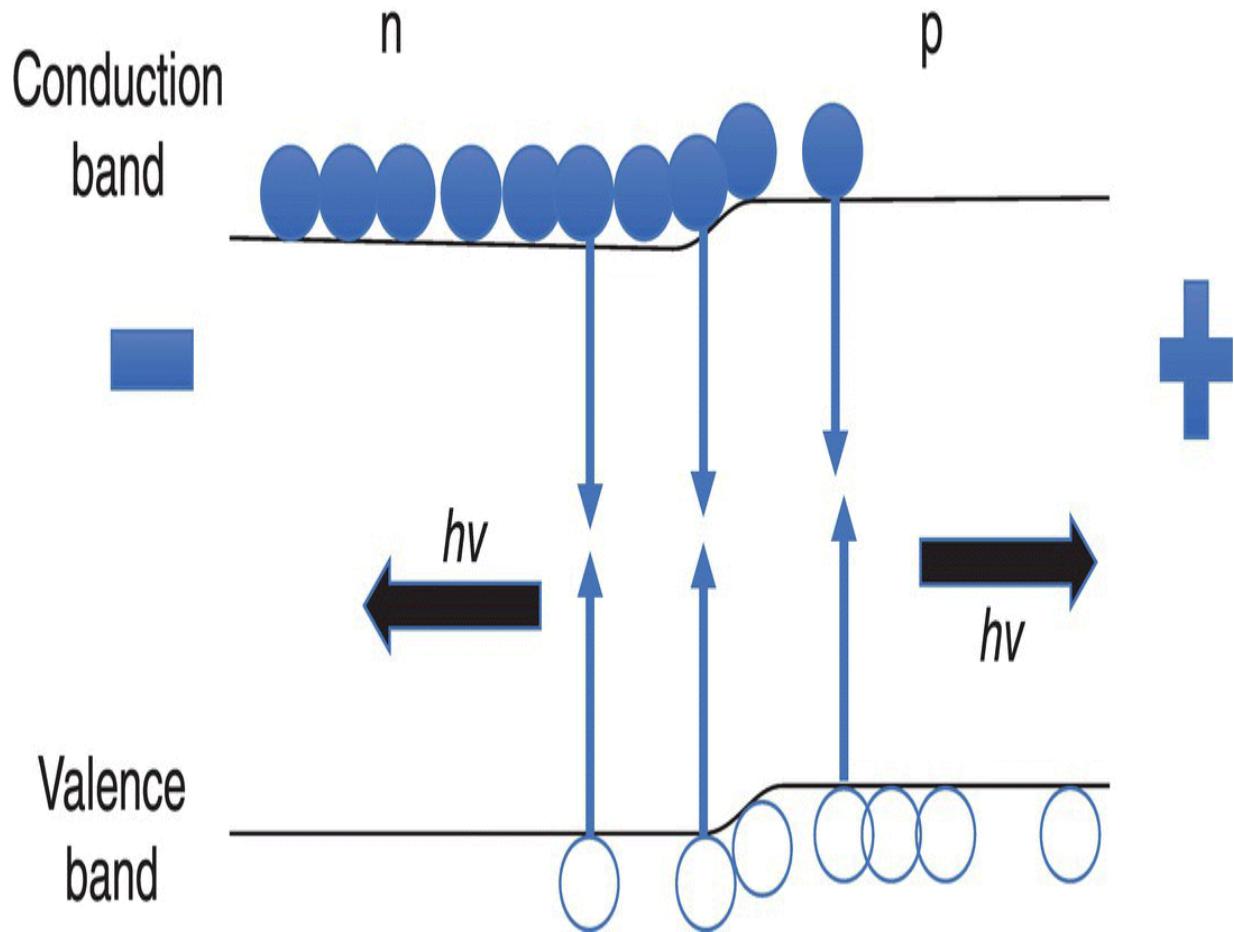

[Figure 13.9 On the left we have a highly doped pn-junction. When we forward ...](#)

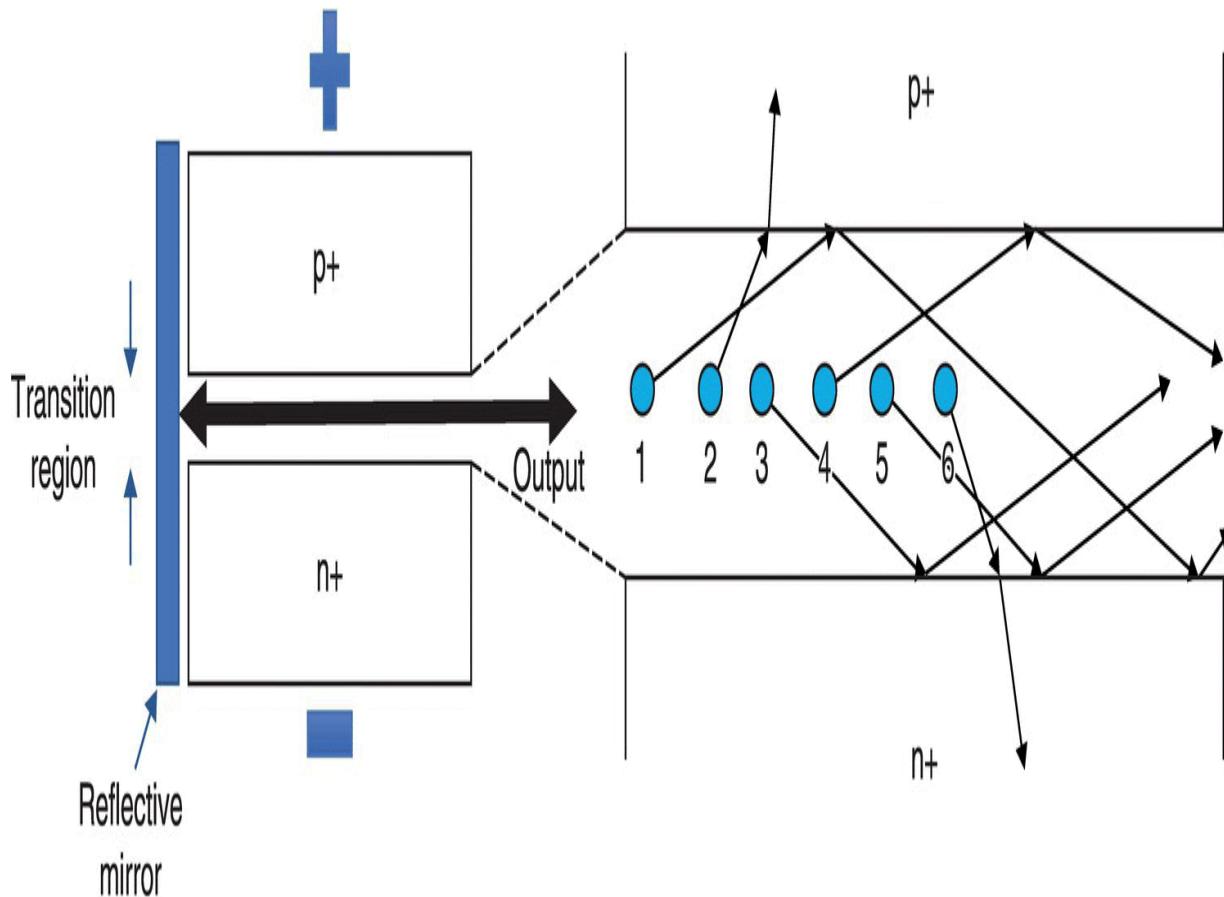

[Figure 13.10 In a LASER semiconductor, the reflective properties of the tran...](#)

[Figure 13.11 Some methods to confine the beam inside the semiconductor cavit...](#)

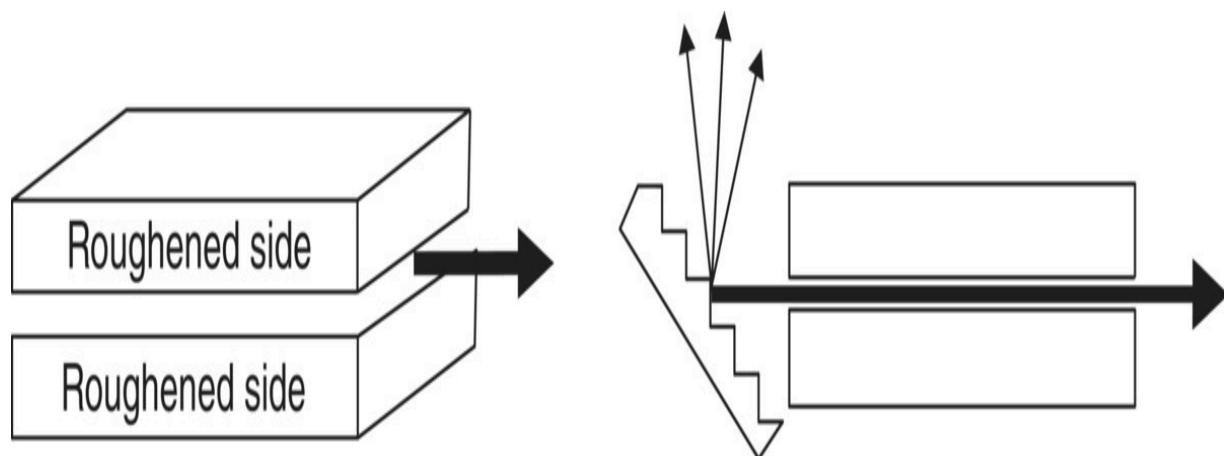

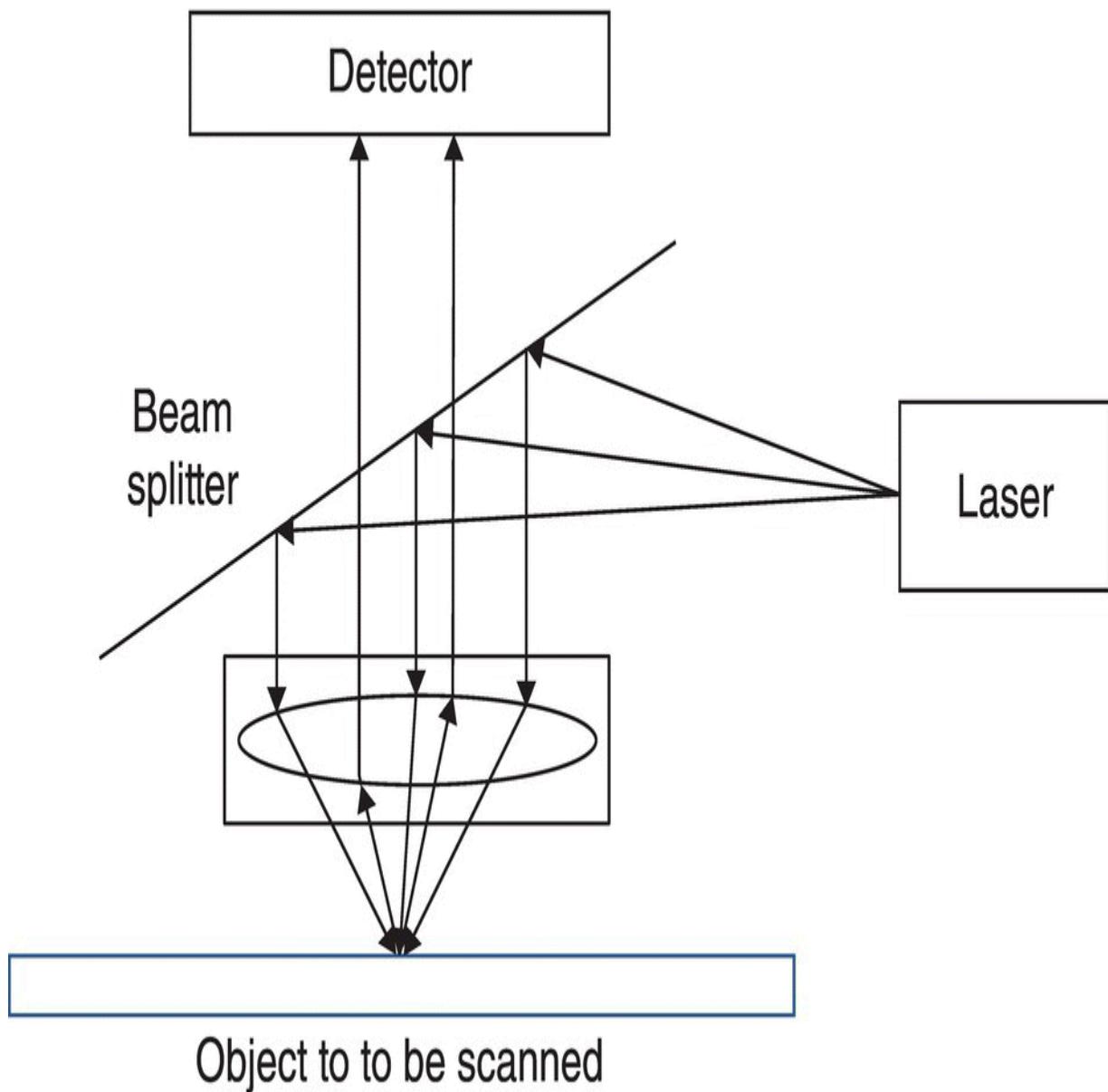

[Figure 13.12 Typical system for LASER scanning.](#)

[Figure 13.13 The spontaneous recombination of electrons and holes at the jun...](#)

[Figure 13.14 A typical detector readout array with as many inputs as detecto...](#)

Chapter 14

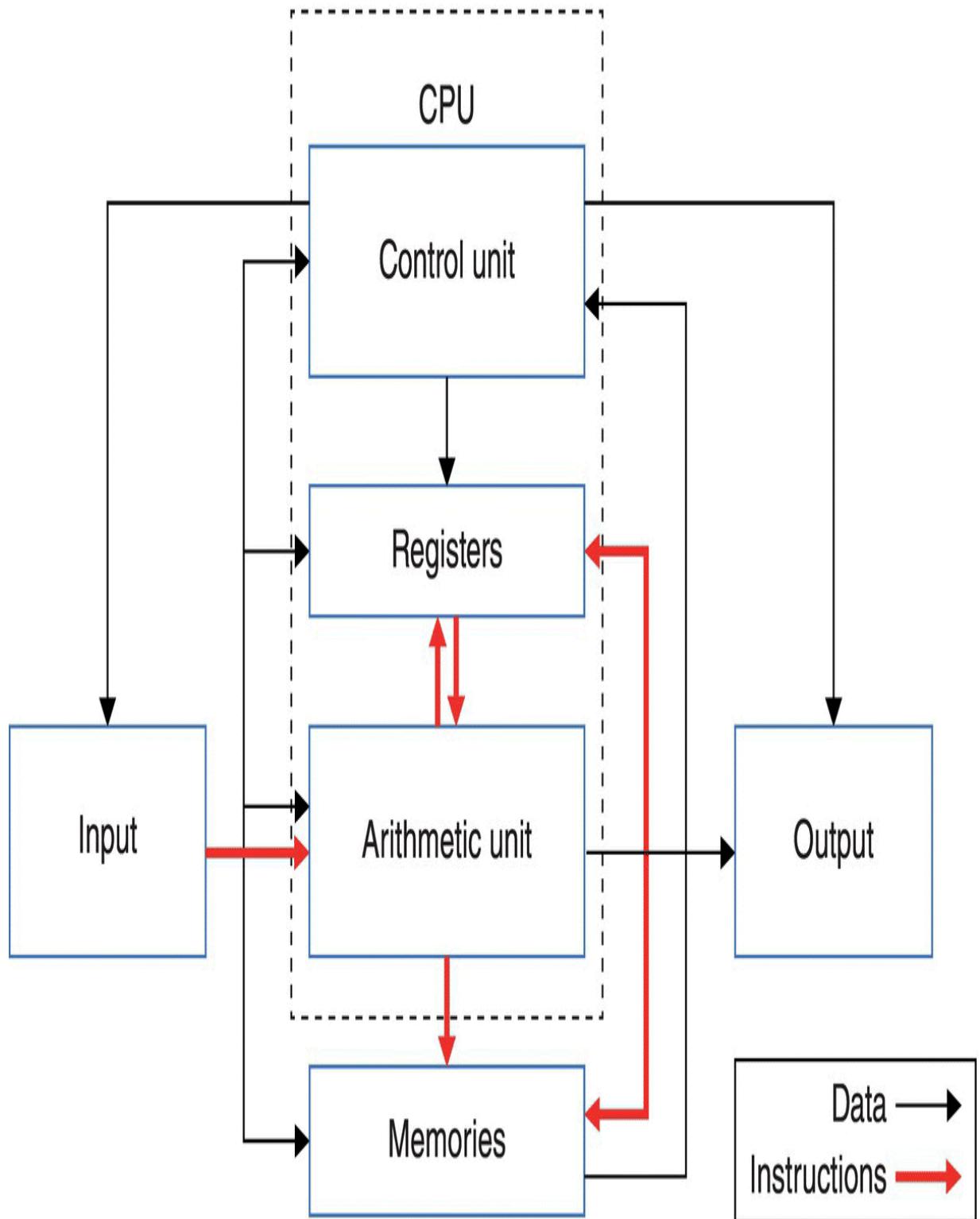

[Figure 14.1 Basic components and interconnections of a modern computer.](#)

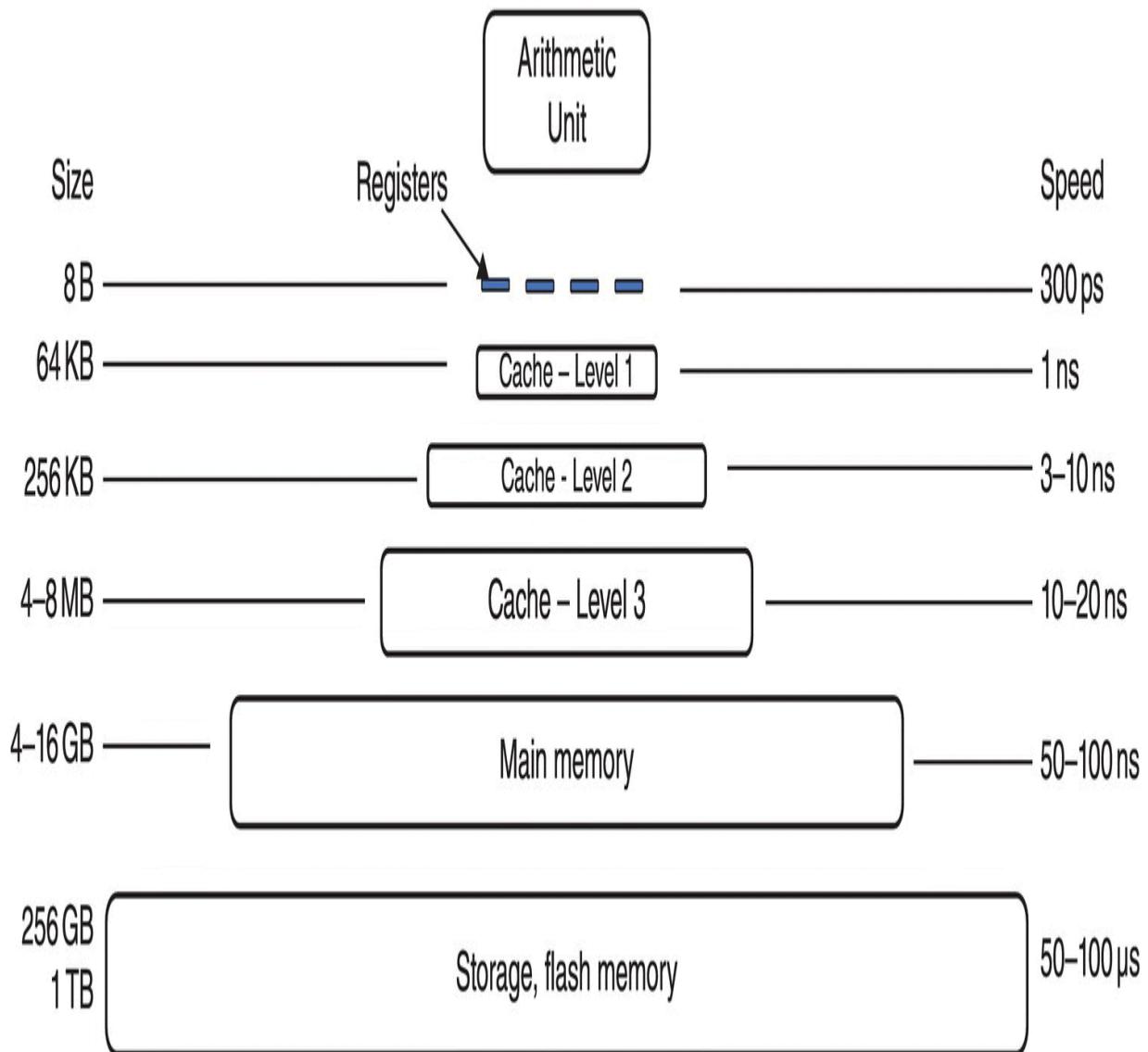

[Figure 14.2 Memories in a typical laptop. The closer the memories are to the...](#)

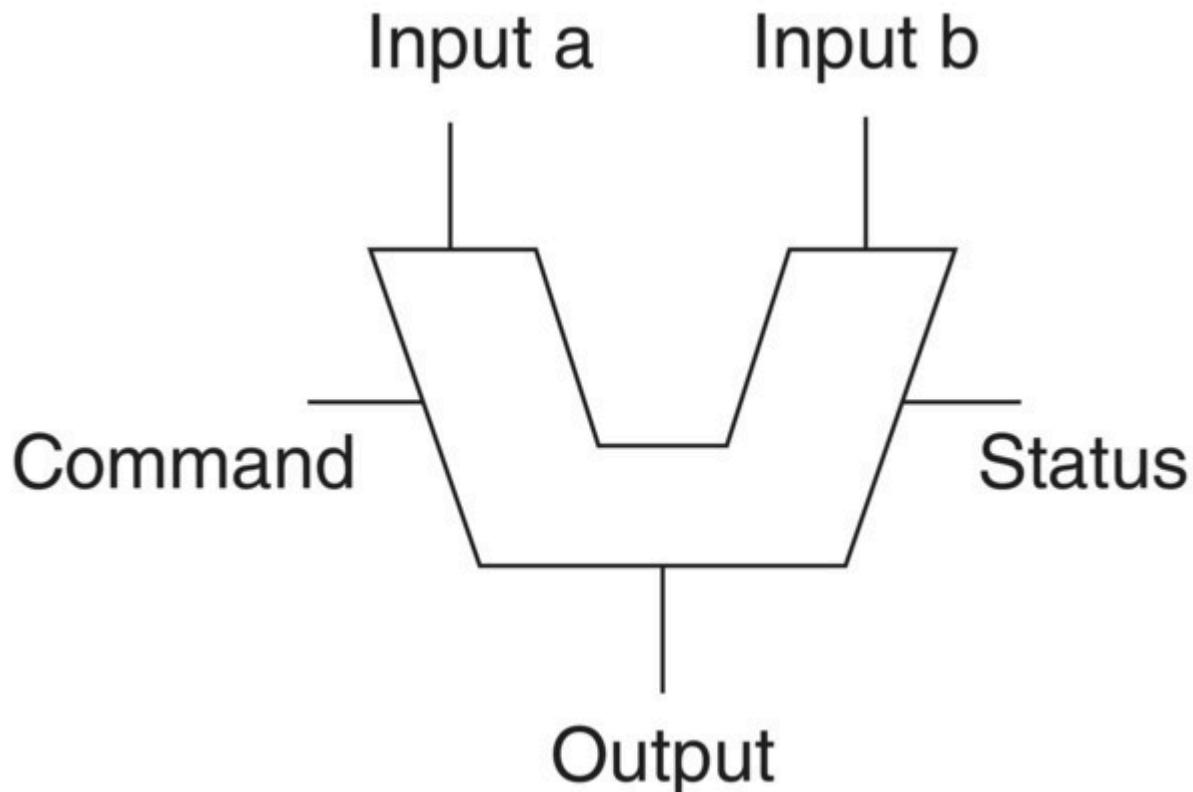

[Figure 14.3 Symbol for the ALU.](#)

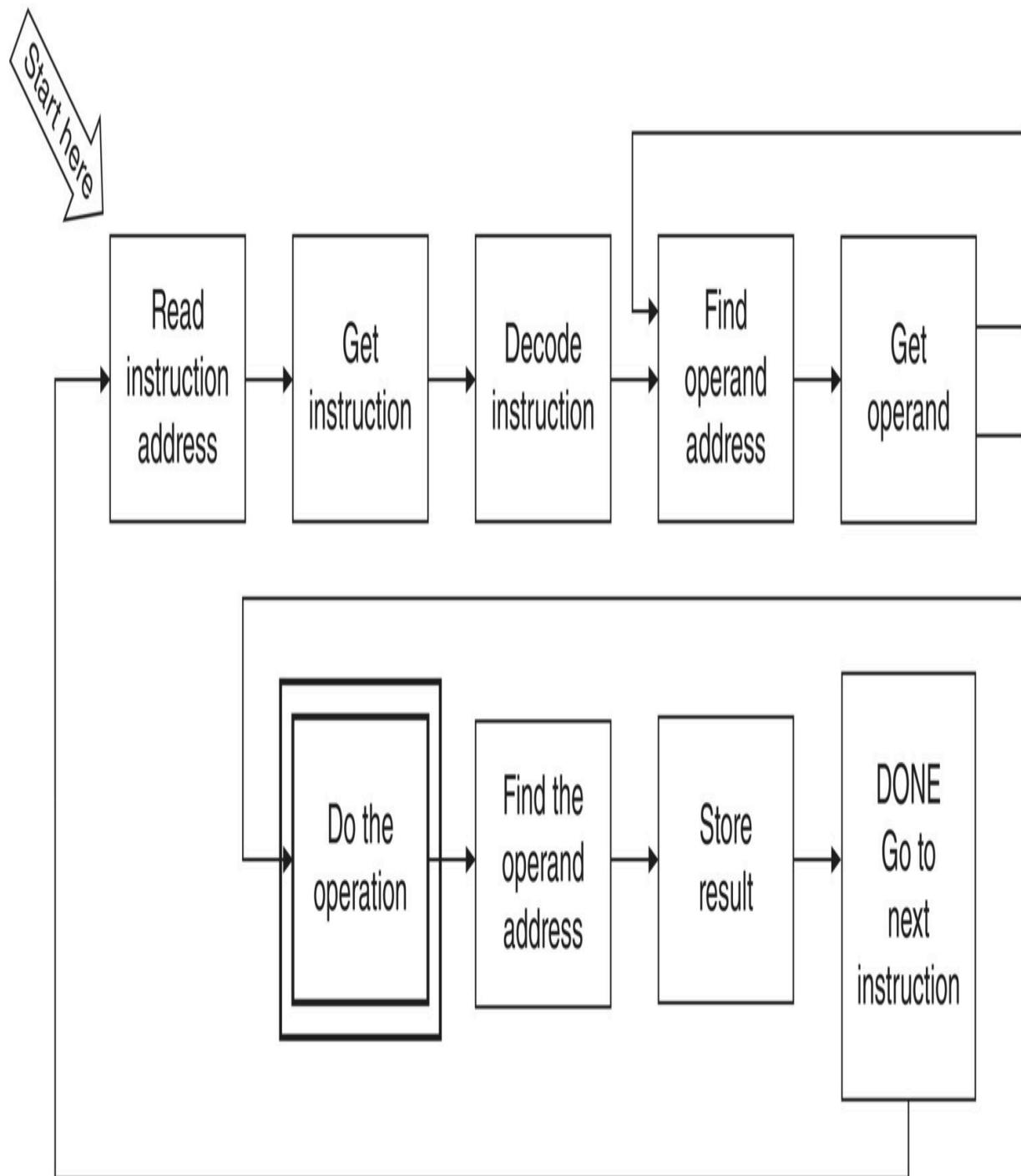

[Figure 14.4 The CPU processes an operation sequentially and when it finishes...](#)

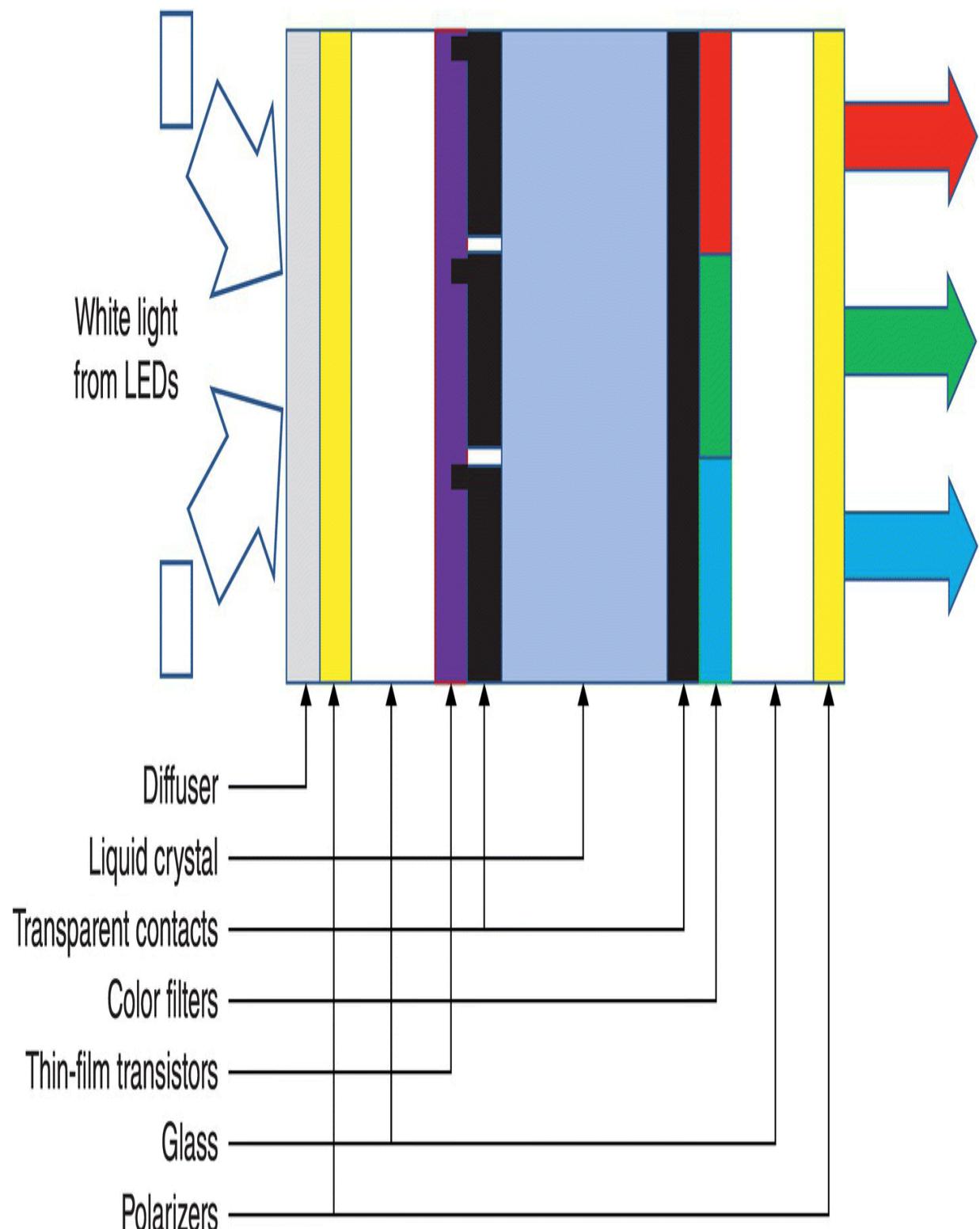

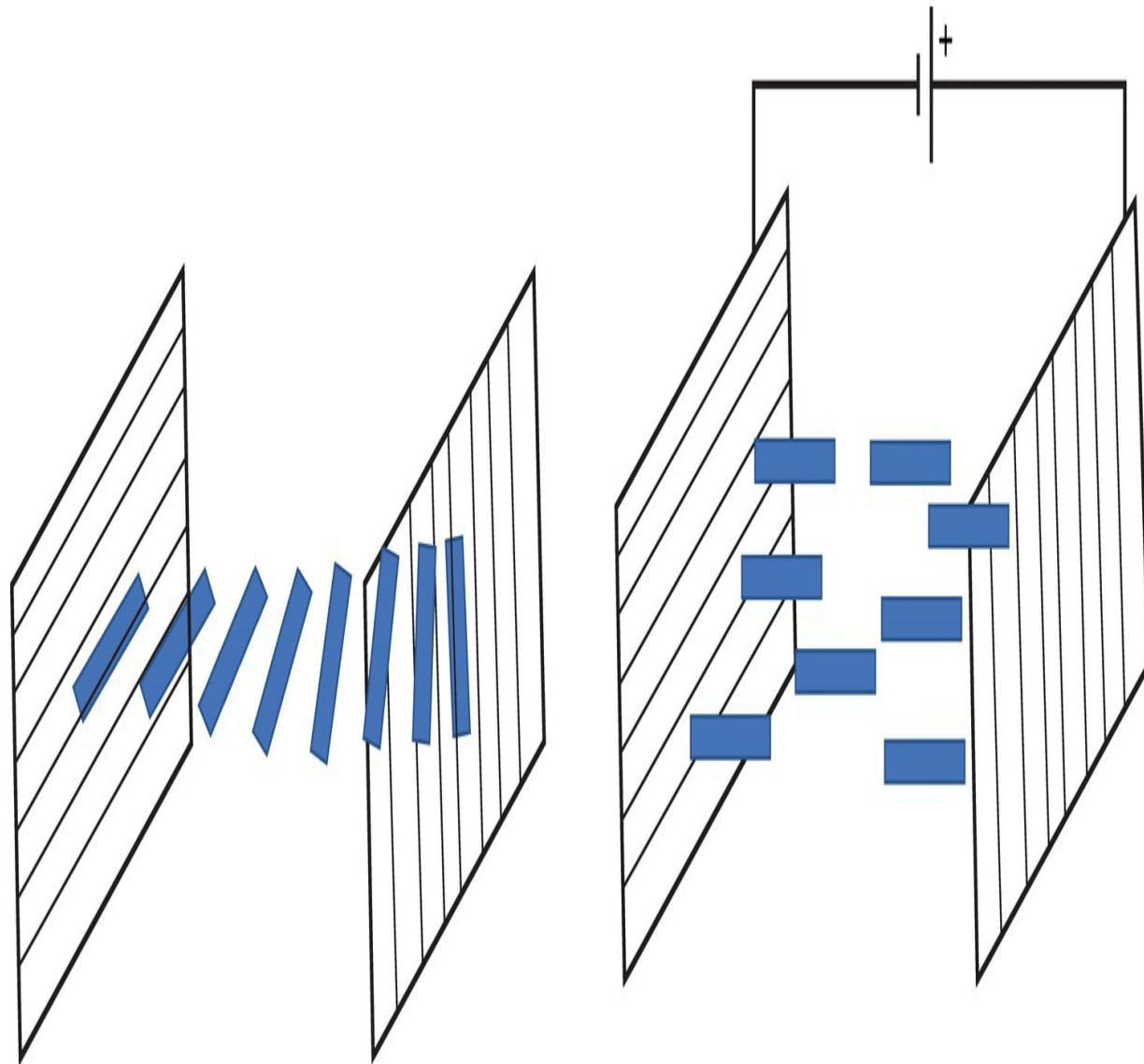

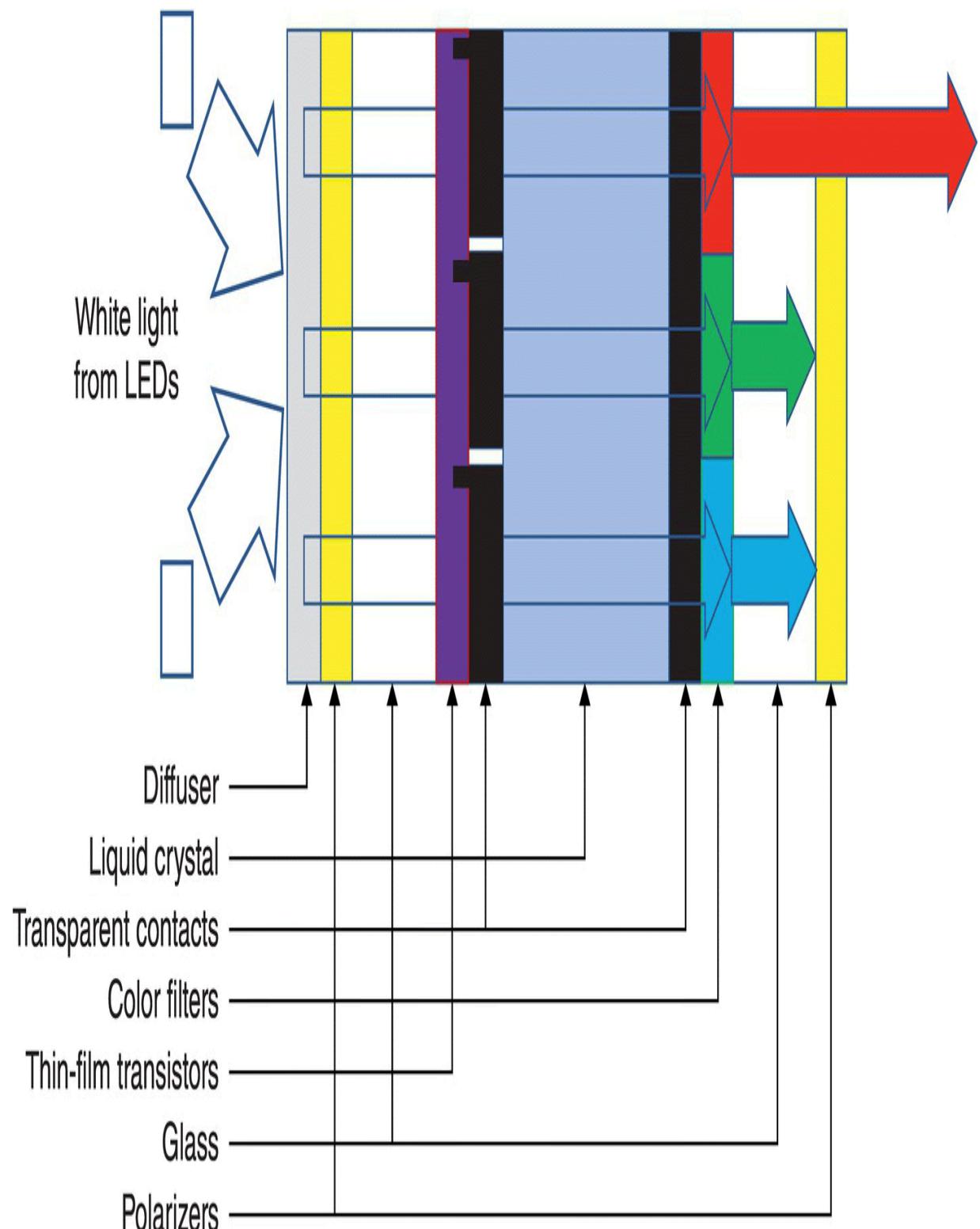

[Figure 14.5 The main components of an LCD. The liquid crystal is in the midd...](#)

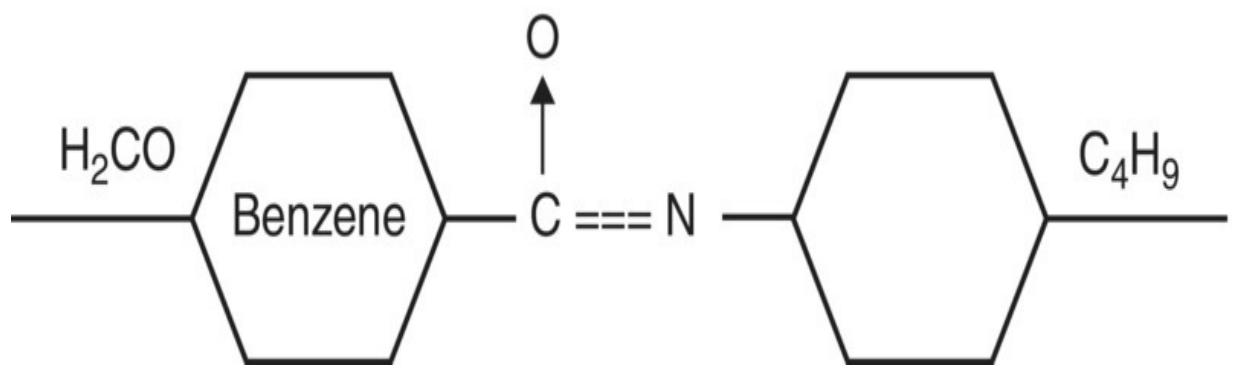

[Figure 14.6 Molecule of a liquid crystal consisting of two hexagonal benzene...](#)

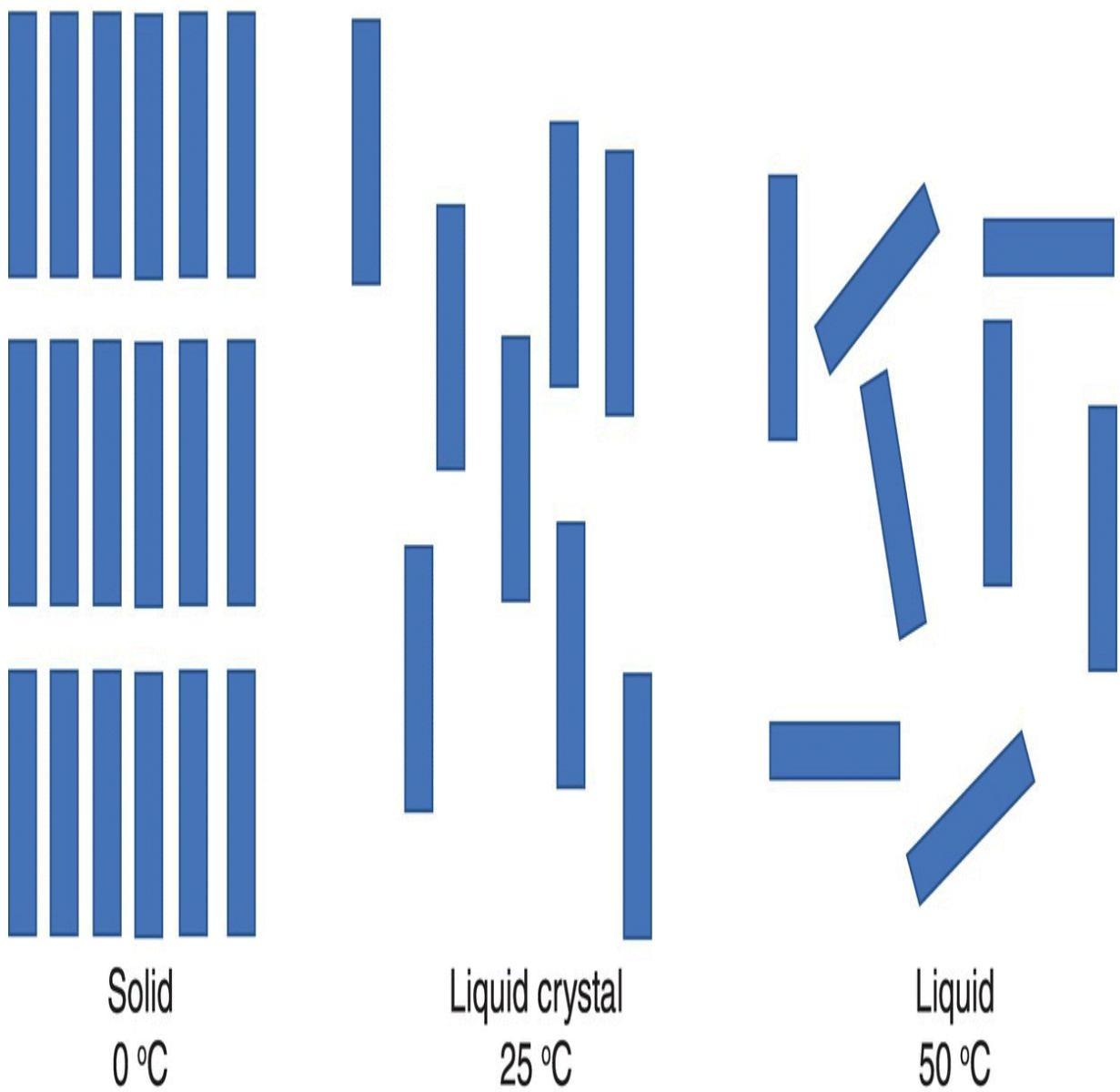

[Figure 14.7 The three phases of a liquid crystal: solid at 0 °C, liquid crys...](#)

[Figure 14.8 The liquid crystal molecules align themselves with the two conta...](#)

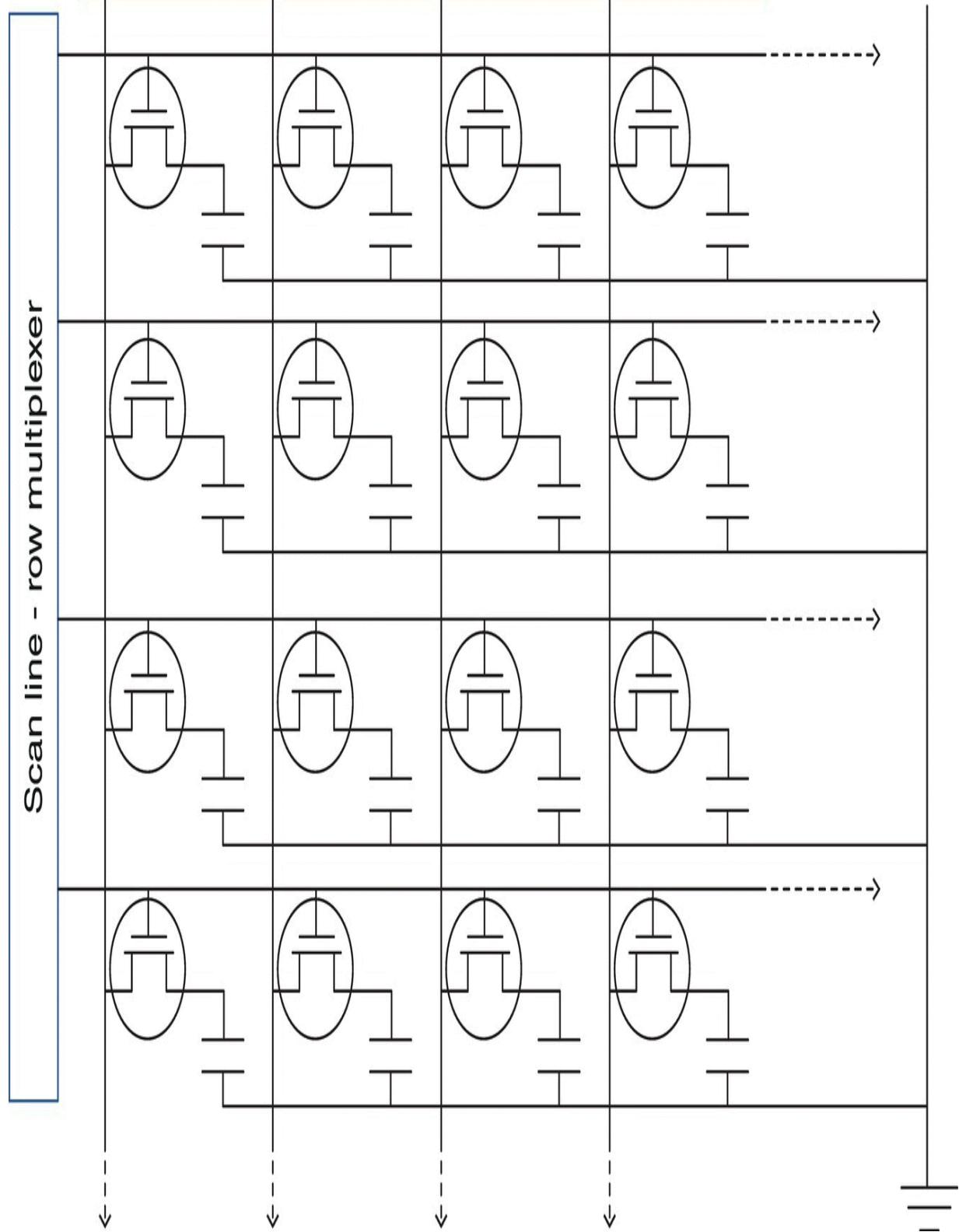

[Figure 14.9 A partial matrix of CMOS switches that turn ON and OFF each of t...](#)

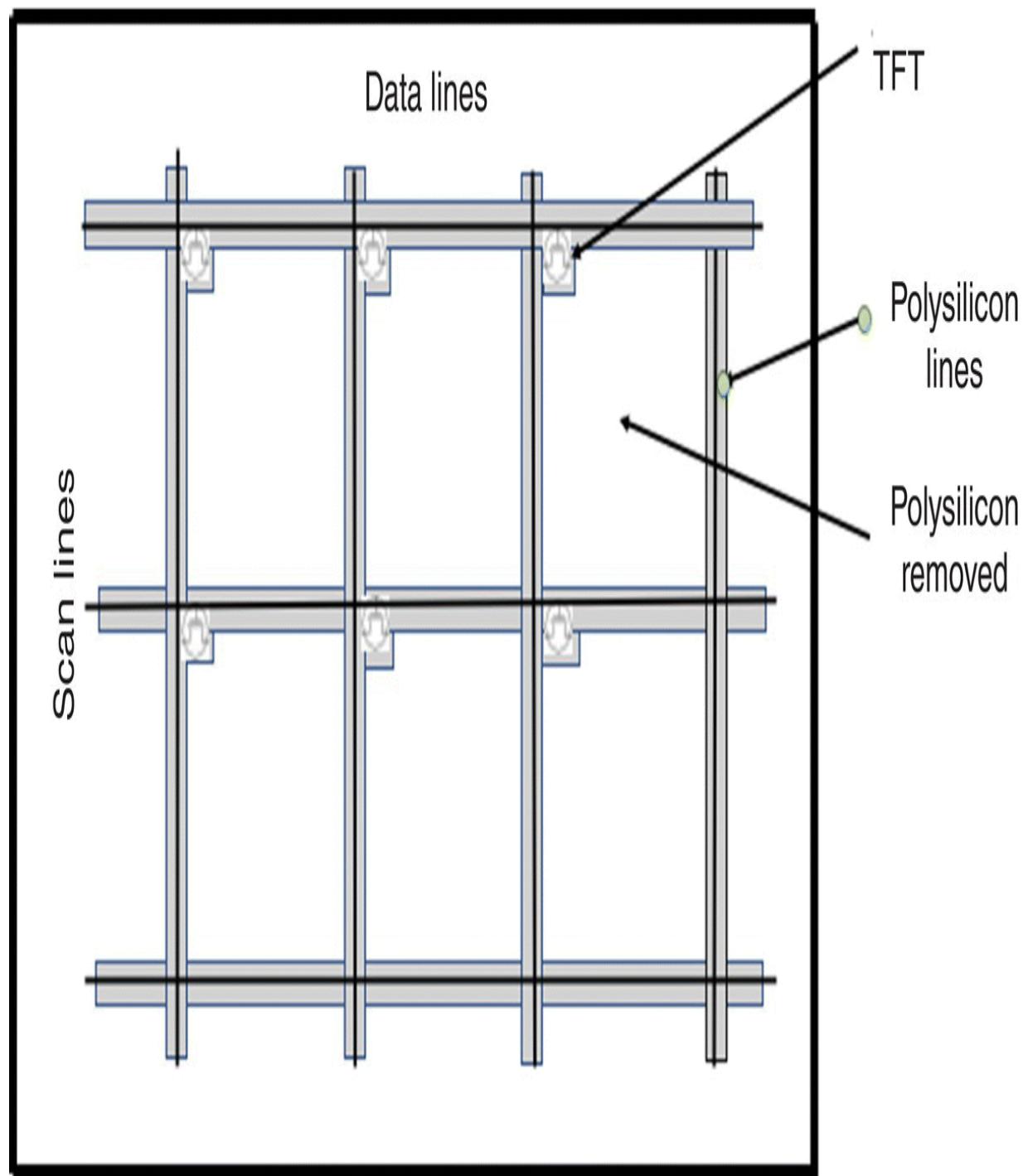

[Figure 14.10 A partial array showing, not to scale, the portions of the poly...](#)

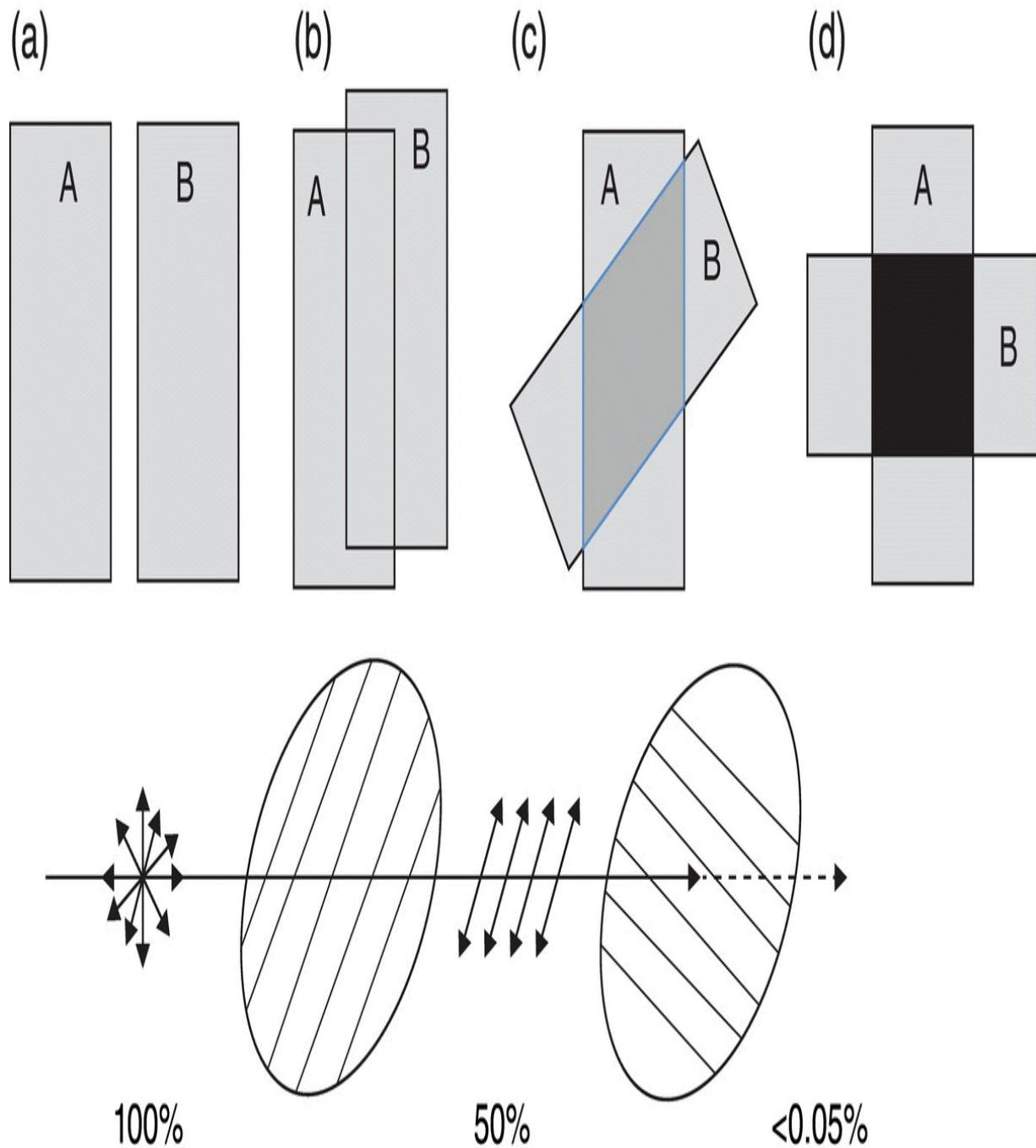

[Figure 14.11 Top: a pair of polarizers, A and B. Both are polarized in the s...](#)

[Figure 14.12 The transistor of the red pixel is OFF, scattering the light in...](#)

Chapter 15

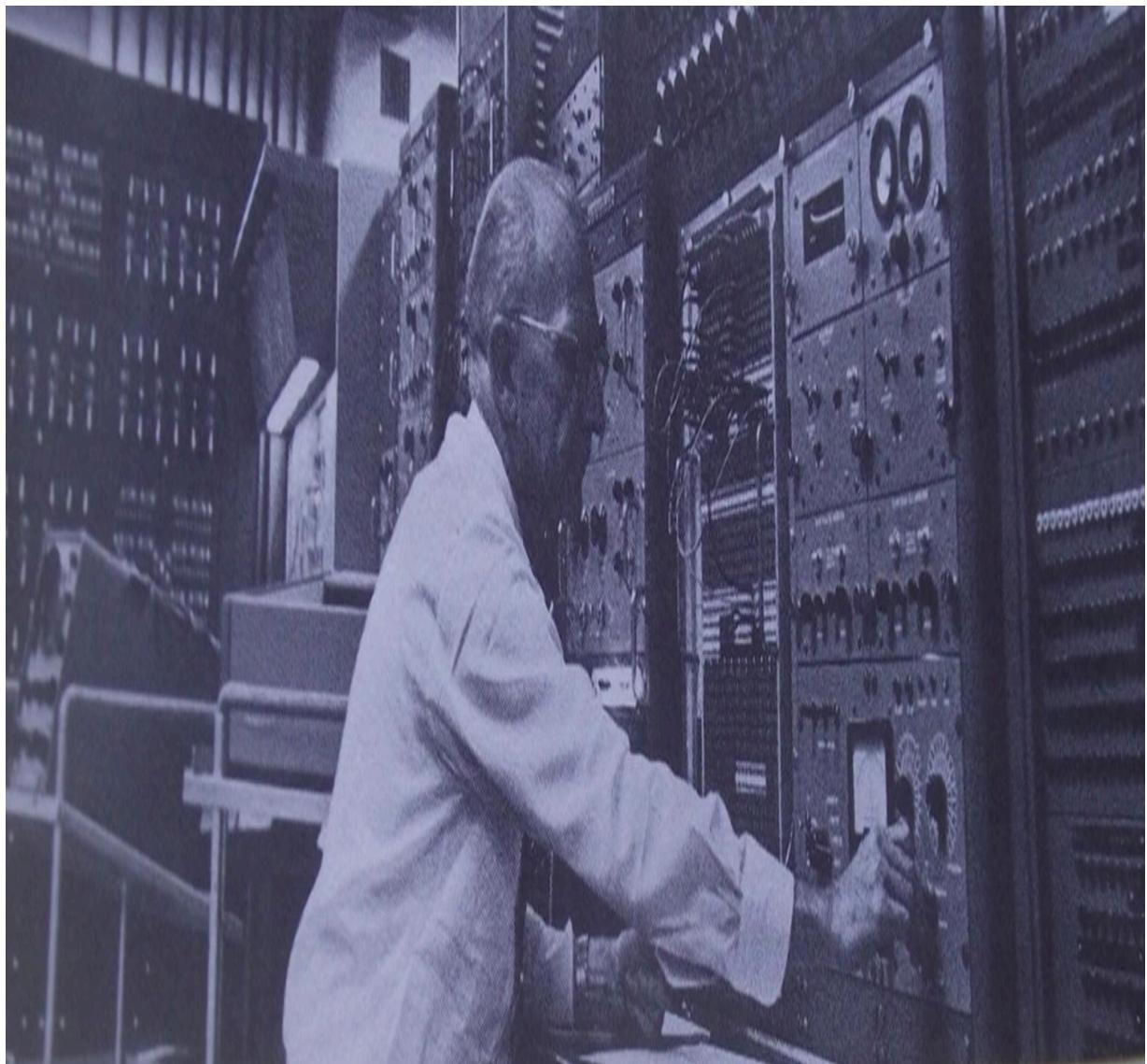

[Figure 15.1 Analogue computer at Northwestern University in the 1960s with D...](#)

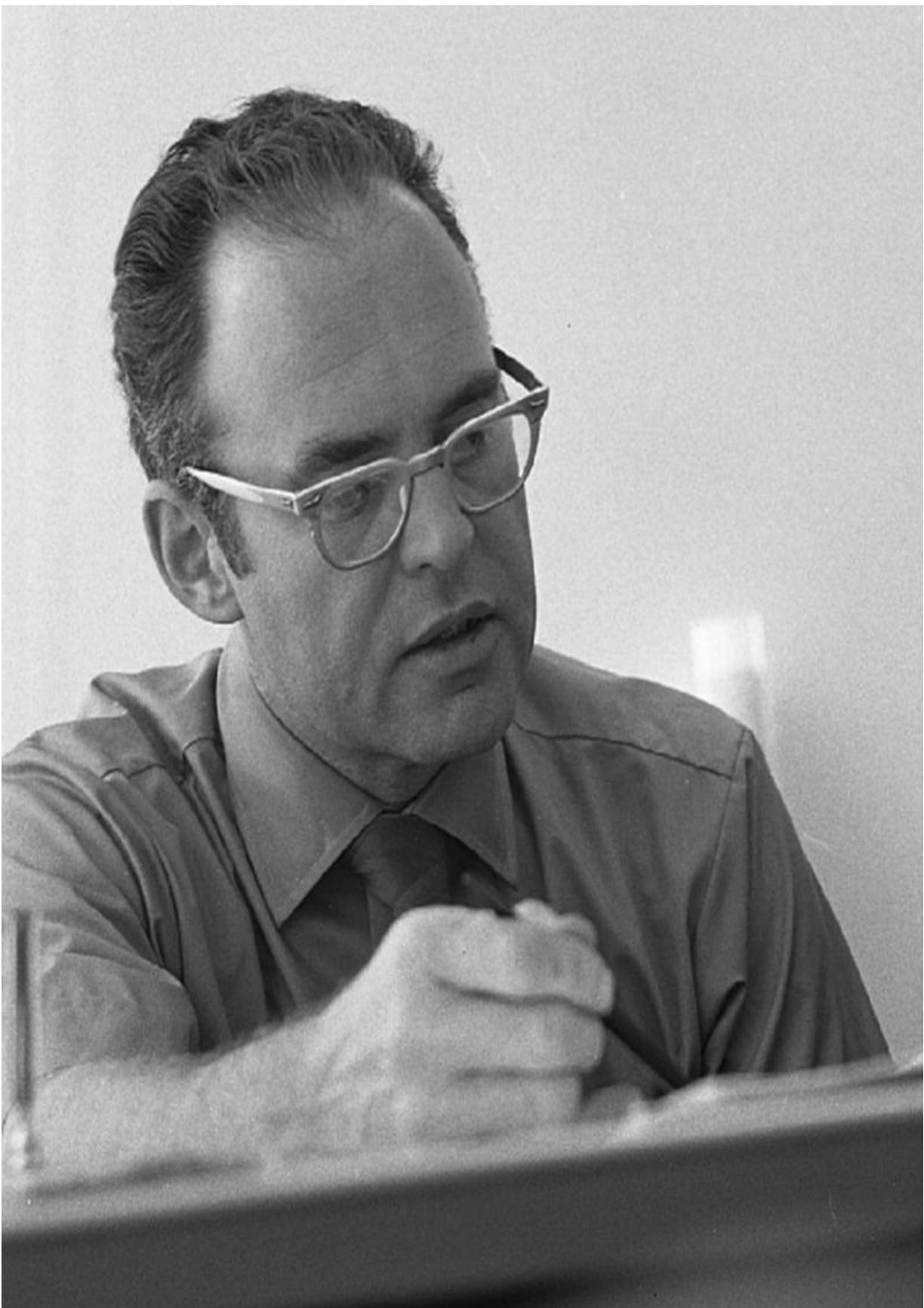

[Figure 15.2 Dr. Gordon Moore, past CEO of Intel, most famous for Moore's law...](#)

[Figure 15.3 The number of transistors in a millimeter square space as a func...](#)

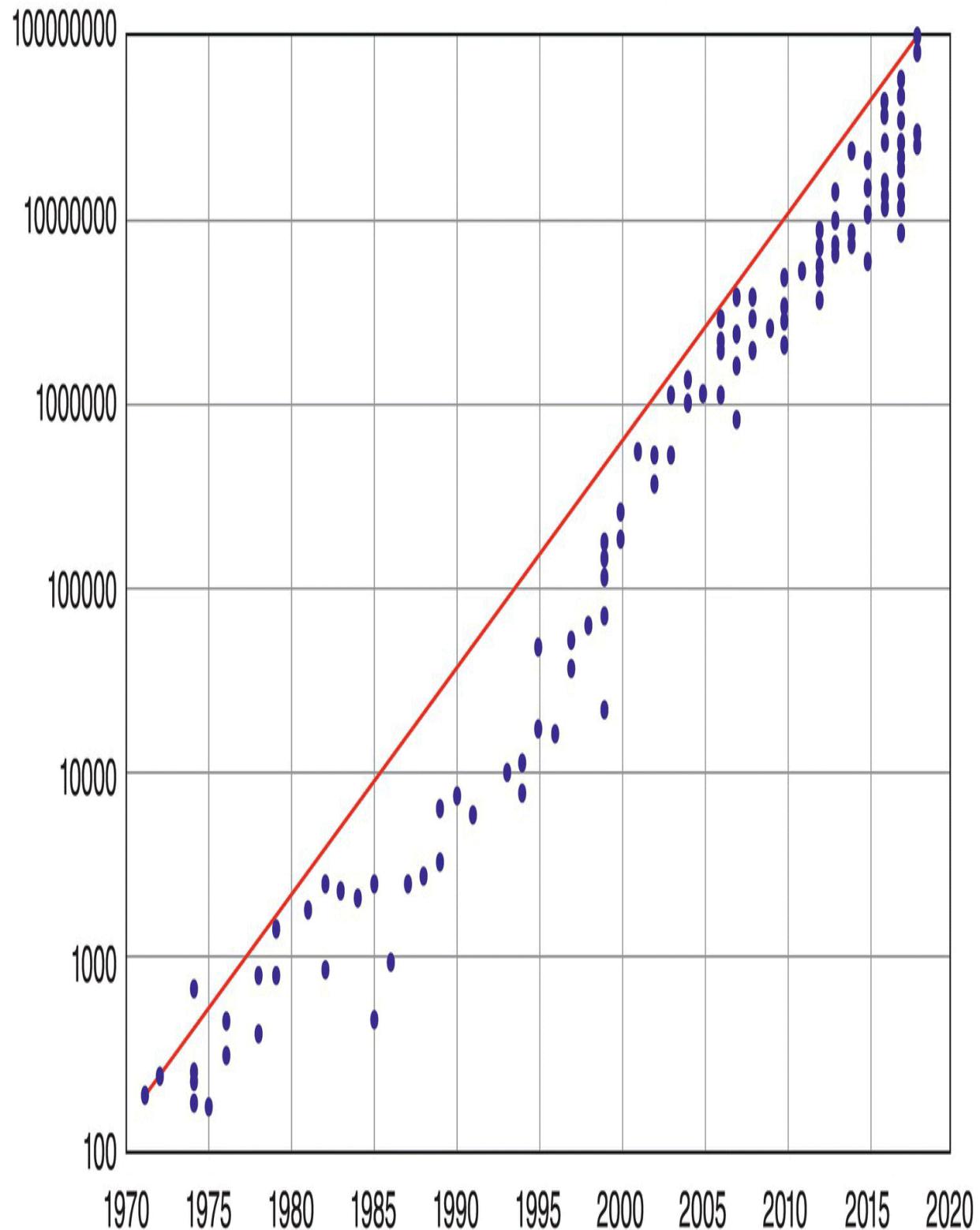

[Figure 15.4 The growth of the number of transistors in an integrated chip be...](#)

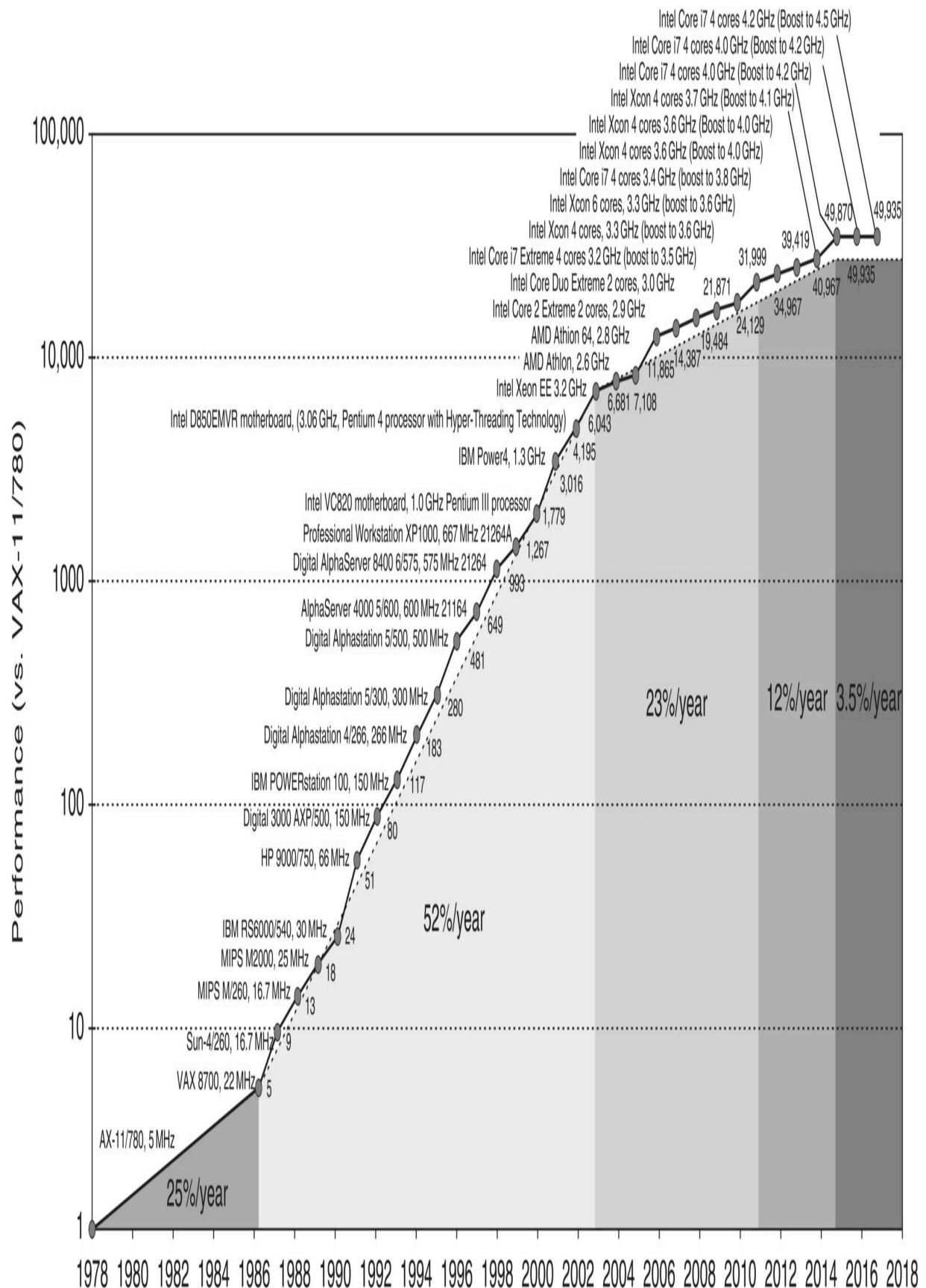

[Figure 15.5 Processor growth in the last 40 years](#)

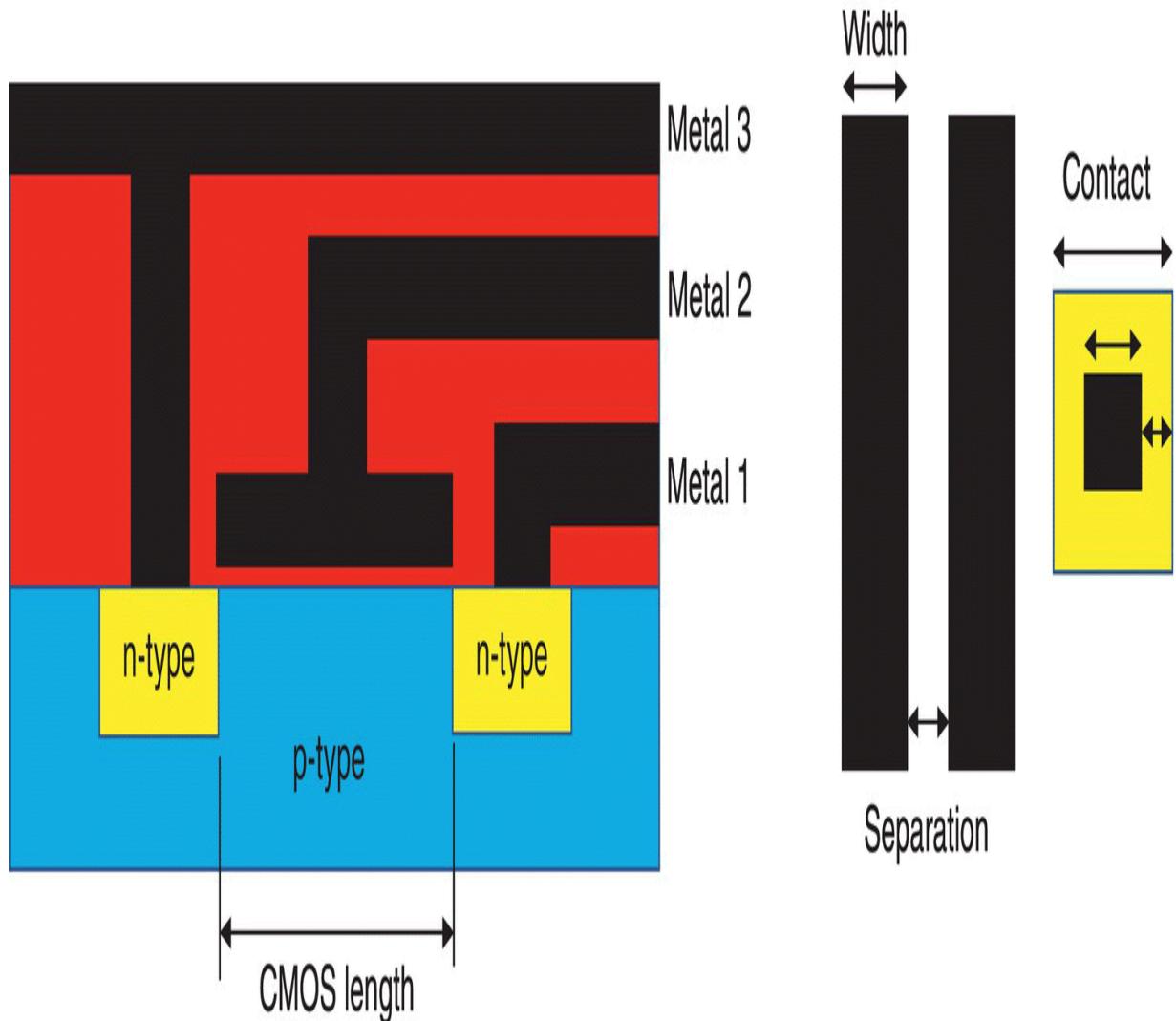

[Figure 15.6 A FET and some designs rules that are needed to ensure that key ...](#)

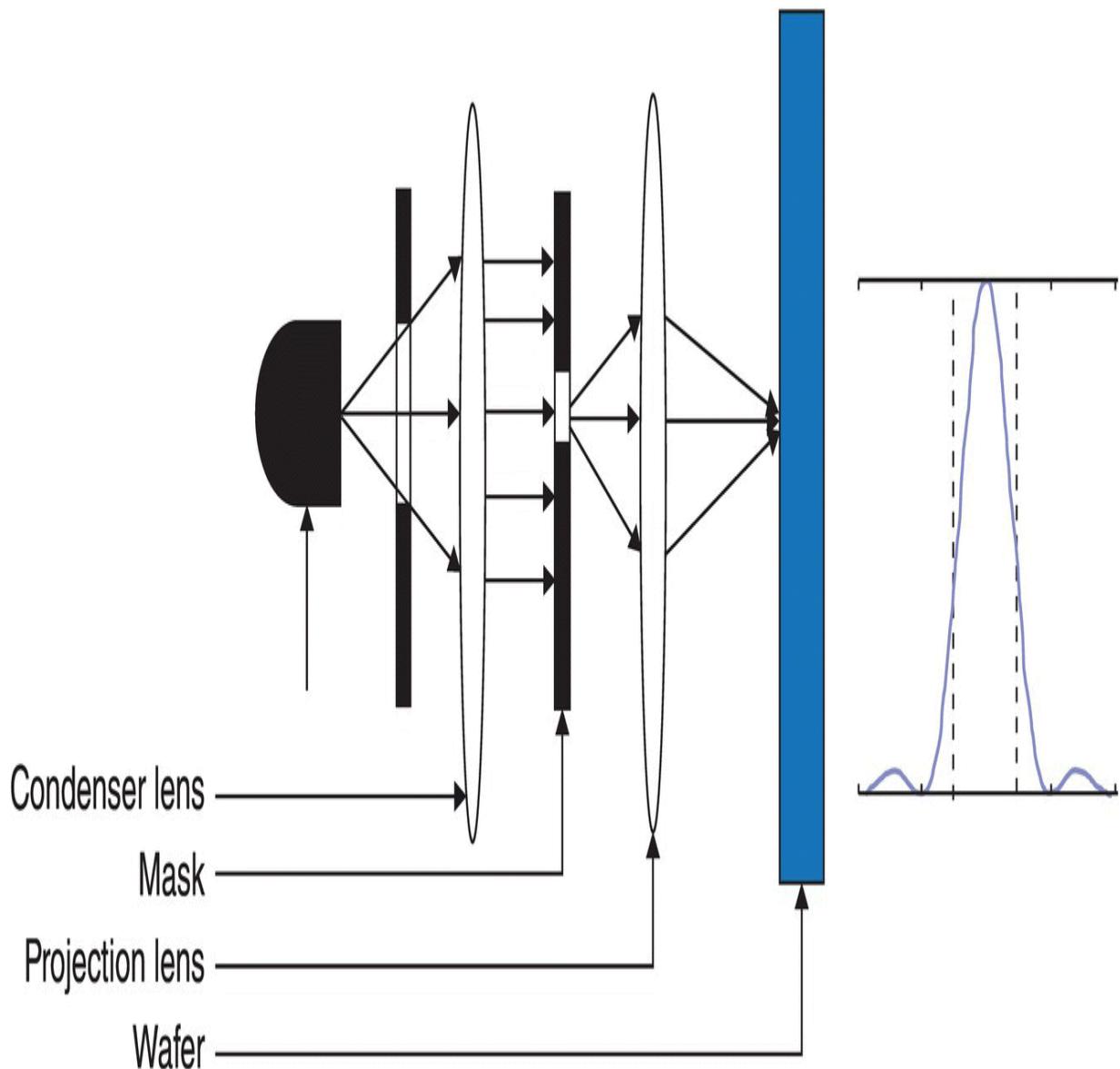

[Figure 15.7 Sketch of an optical projection system \(left\) and the resulting ...](#)

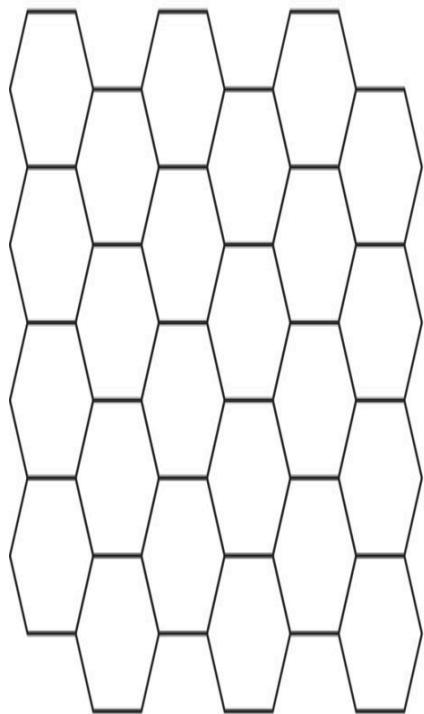

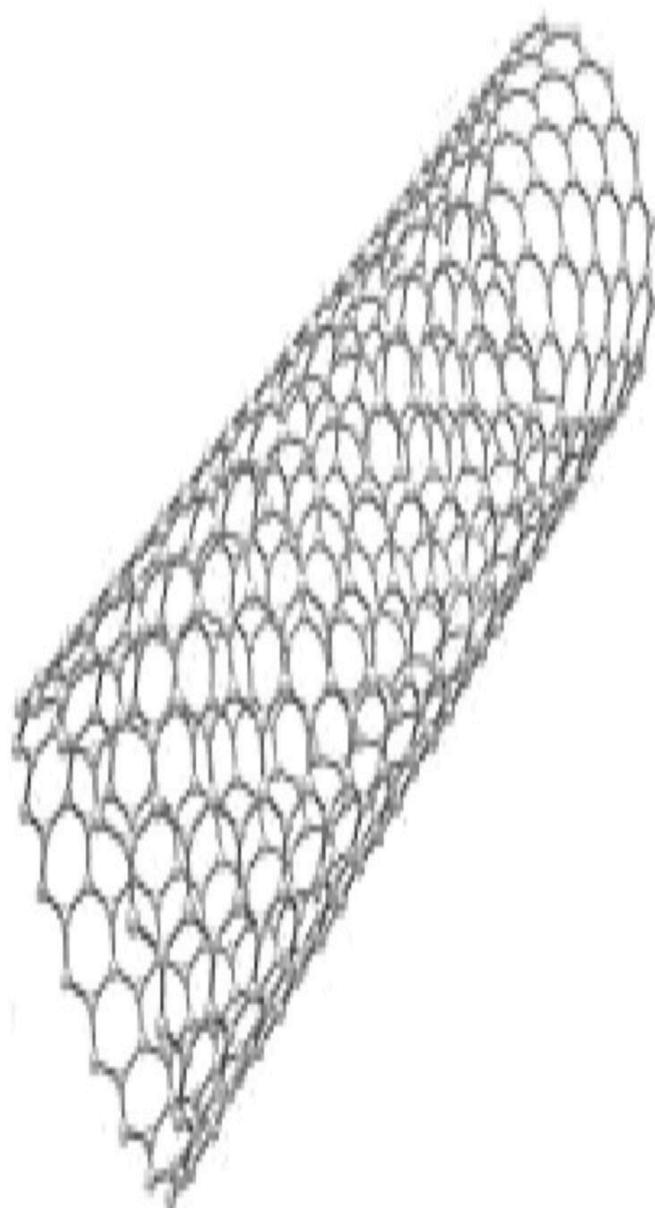

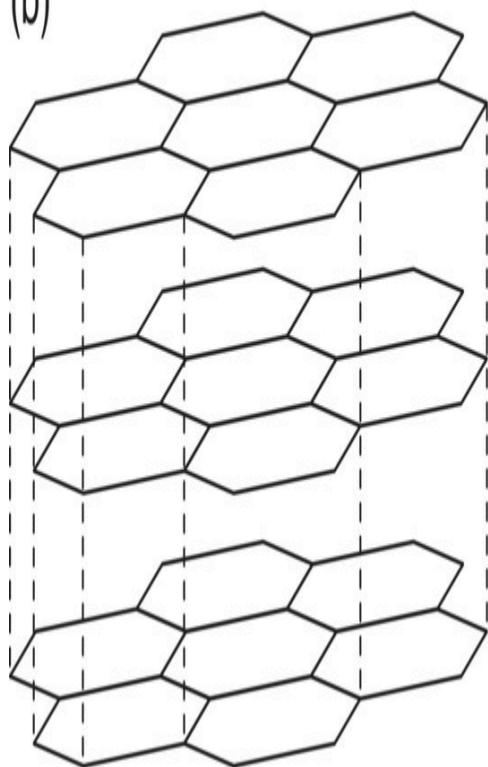

[Figure 15.8 Crystallographic structures of carbon in the graphite state \(A a...](#)

[Figure 15.9 An IBM quantum computer.](#)

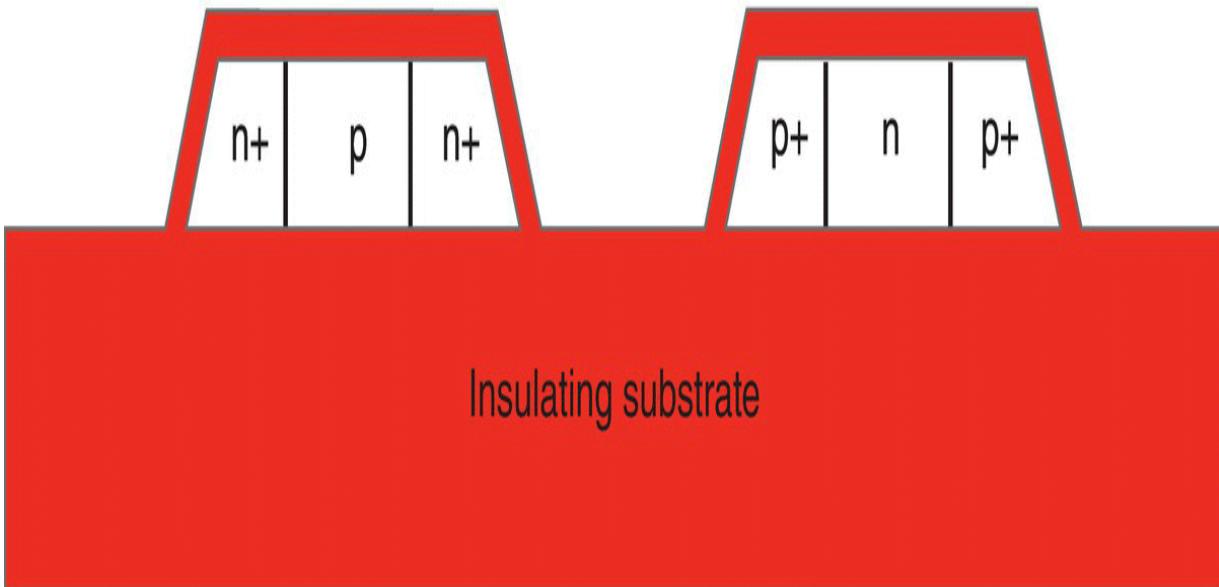

[Figure 15.10 An n-MOS and p-MOS fabricated on top of an insulating substrate...](#)

[Figure 15.11 In a vertical integration process we deposit more than one laye...](#)

[Figure 15.12 An example of multiple metallic layer interconnects.](#)

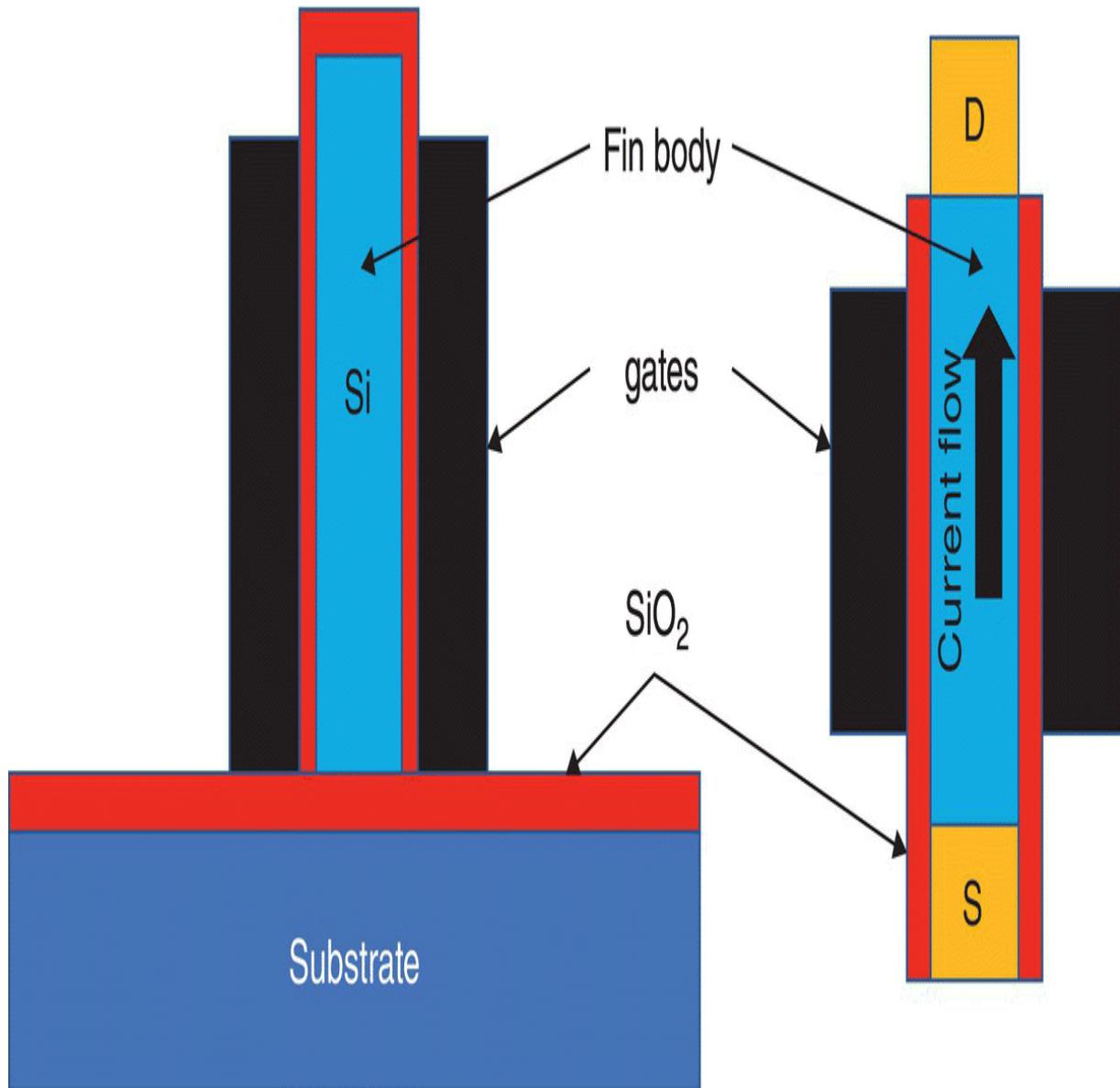

[Figure 15.13 Sketch of a FinFET. The semiconductor is a very thin vertical s...](#)

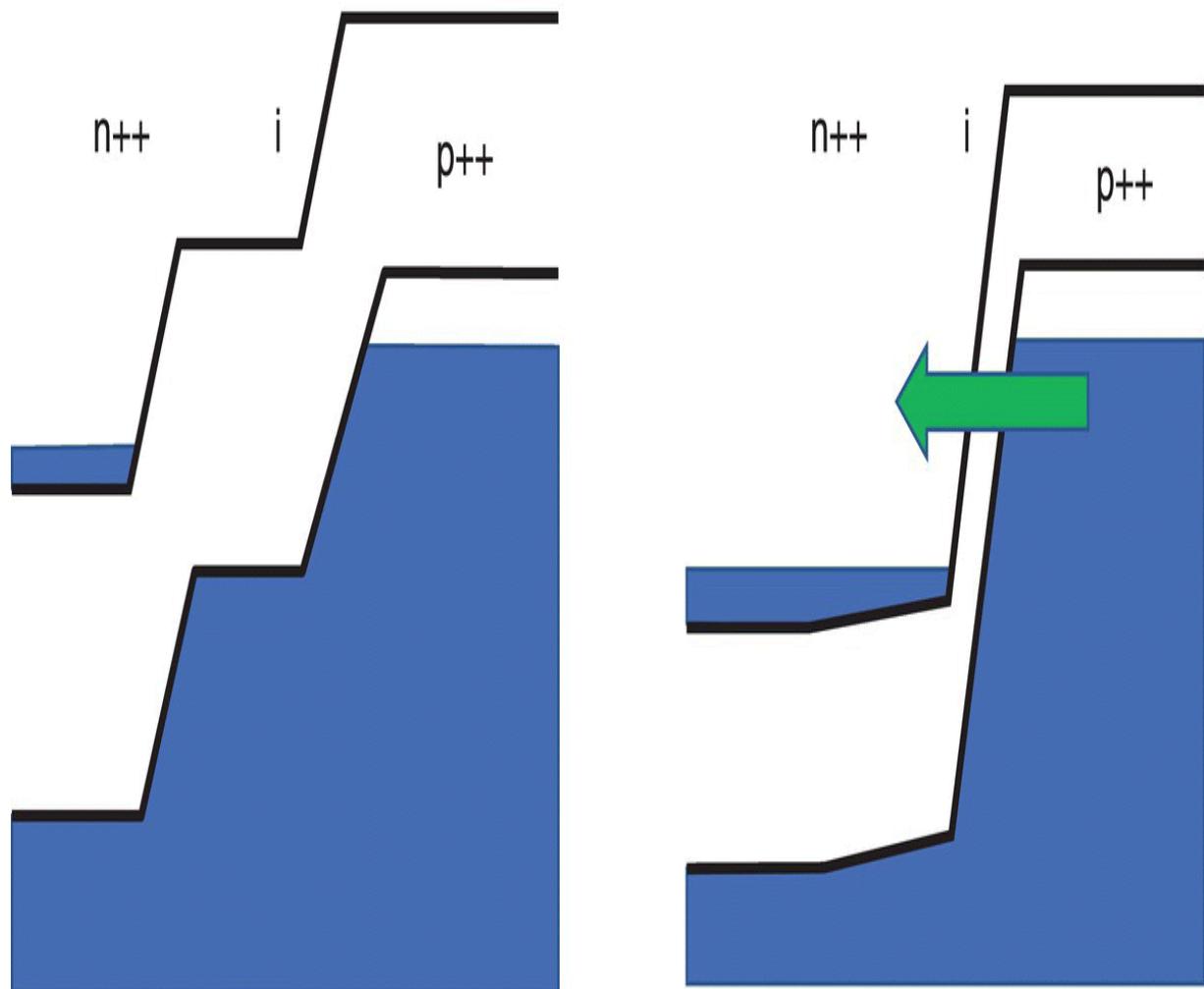

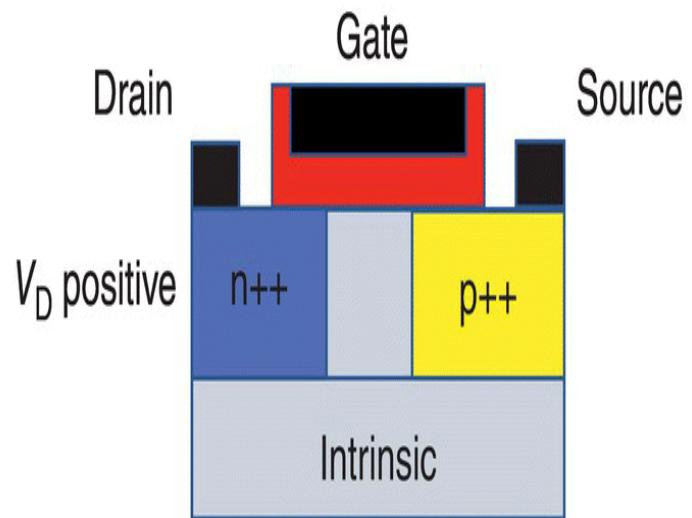

[Figure 15.14 The tunnel FET and energy bands when the TFET is reversed biase...](#)

# Semiconductor Basics

## **A Qualitative, Non-mathematical Explanation of How Semiconductors Work and How They Are Used**

George Domingo

*Berkeley*

CA, USA

WILEY

This edition first published 2020

© 2020 John Wiley & Sons Ltd.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, except as permitted by law. Advice on how to obtain permission to reuse material from this title is available at <http://www.wiley.com/go/permissions>.

The right of George Domingo to be identified as the author of this work has been asserted in accordance with law.

*Registered Offices*

John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030, USA

John Wiley & Sons Ltd, The Atrium, Southern Gate, Chichester, West Sussex, PO19 8SQ, UK

*Editorial Office*

The Atrium, Southern Gate, Chichester, West Sussex, PO19 8SQ, UK

For details of our global editorial offices, customer services, and more information about Wiley products visit us at [www.wiley.com](http://www.wiley.com).

Wiley also publishes its books in a variety of electronic formats and by print-on-demand. Some content that appears in standard print versions of this book may not be available in other formats.

*Limit of Liability/Disclaimer of Warranty*

In view of ongoing research, equipment modifications, changes in governmental regulations, and the constant flow of information relating to the use of experimental reagents, equipment, and devices, the reader is urged to review and evaluate the information provided in the package insert or instructions for each chemical, piece of equipment, reagent, or device for, among other things, any changes in the instructions or indication of usage and for added warnings and precautions. While the publisher and authors have used their best efforts in preparing this work, they make no representations or warranties with respect to the accuracy or completeness of the contents of this work and specifically disclaim all warranties, including without limitation any implied warranties of merchantability or fitness for a particular purpose. No warranty may be created or extended by sales representatives, written sales materials or promotional statements for this work. The fact that an organization, website, or product is referred to in this work as a citation and/or potential source of further information does not mean that the publisher and authors endorse the information or services the organization, website, or product may provide or recommendations it may make. This work is sold with the understanding that the publisher is not engaged in rendering professional services. The advice and strategies contained herein may

not be suitable for your situation. You should consult with a specialist where appropriate. Further, readers should be aware that websites listed in this work may have changed or disappeared between when this work was written and when it is read. Neither the publisher nor authors shall be liable for any loss of profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages.

*Library of Congress Cataloging-in-Publication Data*

Names: Domingo, George, 1937– author.

Title: Semiconductor basics : a qualitative, non-mathematical explanation of how semiconductors work and how they are used / George Domingo, Berkeley, CA, US.

Description: First edition. | Hoboken, NJ, USA : Wiley, [2020] | Includes bibliographical references and index.

Identifiers: LCCN 2020015406 (print) | LCCN 2020015407 (ebook) | ISBN 9781119702306 (cloth) | ISBN 9781119597117 (adobe pdf) | ISBN 9781119597131 (epub)

Subjects: LCSH: Semiconductors. | Solid state electronics. | Electronic apparatus and appliances.

Classification: LCC TK7871.85 .D654 2020 (print) | LCC TK7871.85 (ebook) | DDC 621.3815/2–dc23

LC record available at <https://lccn.loc.gov/2020015406>

LC ebook record available at <https://lccn.loc.gov/2020015407>

Cover Design: Wiley

Cover Images: Computer motherboar © Bet\_Noire/Getty Images, Two People - Drawn by Pey Llussà, Circuit Board © filo/Getty Images, Central processor unit © Artem\_Egorov/Getty Images, Graphene sheet © KTSDESIGN/SCIENCE PHOTO LIBRARY/Getty Images

*To my family for their love and support*

# Acknowledgements

I would like to recognize all those scientists, engineers, professors, authors, teachers, and also students who in the past 130 years with their research, experiments, theories, analysis, publications, and textbook have been able to explain beautifully how matter behaves, how to use it, and how to explain it to the next generation of scientists. In the process they created an electronic revolution. As someone already said, we are sailing on the shoulders of all those thousands of geniuses that preceded us.

I want to acknowledge the efforts and support of the Wiley editors who made the text more readable and clearer.

I want to thank my family who have been always helpful, encouraging, and patient with me and my project.

Finally, I would like to mention Dr. Gerry Hanh, who upon reading the first chapters that I wrote as a hobby, insisted I send them to Wiley, resulting in the book you have now in your hands.

# Introduction

A couple of years ago, I was asked to give a talk to the Rotary club in Terrassa, a city about 20 miles northwest of Barcelona. They asked me to divide the talk into three parts: 15 minutes biographical, 15 minutes on my technical work, and 15 minutes about NASA. The first and last 15 minutes of the talk went well, but the technical explanation about how infrared detectors work was disappointing. Yes, they did understand the uses and applications of infrared detectors, my technical work with the astronomical observatories of NASA, but the explanation on how infrared detectors work was not as clear and instructive as I had hoped. I was then and I am now convinced that any educated person can understand how semiconductor devices work. This talk two years ago was my motivation to start writing this book.

Semiconductors are the basis for almost all modern electronic devices. For many people semiconductors are a mysterious material that somehow has taken over modern electronics. In the same way that we understand the concept of god and creatures, but semi-gods are confusing, most of us have an idea of what a conductor (electricity flows through it) and an insulator (it doesn't) are, but what the heck is a semiconductor? Furthermore, the prevalent material used for fabricating semiconductors is pure silicon, the second most common element found on earth (28%) after oxygen (47%). Why not use aluminum, the next common element (8%), or strontium or some other exotic and more classy material? Why do we use semiconductors instead of conductors? Don't we want electrons to move freely through our devices?

I attempt here to explain why and how semiconductors work in a form that any educated person can understand. Every chapter explains the subject in a qualitative way, with drawings, photographs, and figures, and very simple relationships (I hate to use the word "equations" here). At the end of most chapters I add

appendices where I include some mathematical formulation with the relevant equations for those who would enjoy looking a little deeper into the subject. I do not try to proof these equations; my purpose is not formally present to you the physics of semiconductors (there are many excellent books that do that) but just to show what the results are. In this book you have to take these results on faith.

Unless you are very allergic to math, do not skip the appendices. There are interesting concepts that amplify the understanding of how semiconductors work. Don't worry; there are no problems at the end of each chapter and no suggested quizzes.

First, I explain what a semiconductor is, the different types we use, and how they are different from conductors and insulators. Next, I explain the key devices that can be constructed using the semiconductor materials: diodes, passive element, and transistors. I talk about the integrated circuits, how we build them and the larger electronic components, and finally what can we expect in the future ([Chapter 15](#)). I interrupt the "theoretical" flow with chapters devoted to applications ([Chapters 4, 7, and 9](#)) that can be understood with just the concepts I have covered in the previous chapters.

This book can be read in different ways. If you are interested in understanding how transistors work, then you should read, in succession, [Chapters 1, 2, 3, 5, and 8](#). You cannot skip any of them or read them in a different order unless, of course, you are already familiar with some of the previous topics. [Chapter 6](#) explains the basic electrical components (resistors, capacitors, and inductors) which we need to understand how we build useful semiconductor circuits. I try to discuss some of the semiconductor applications as soon as I cover the relevant theory. Just by understanding the concept of energy levels and energy bands ([Chapters 2 and 3](#)) you can grasp how infrared detectors work ([Chapter 4](#)). You do not even need to know what resistors or capacitors are. Similarly, after [Chapter 6](#) you can understand the different circuit applications we can fabricate with diodes ([Chapter 7](#)) and after [Chapter 8](#) I explain how we use transistors ([Chapter 9](#)). The next chapters, integrated

circuit fabrication ([Chapter 10](#)) and logic circuits ([Chapter 11](#)), can be read separately at any time, although knowing how a transistor works will help. Yes, I talk about semiconductor devices, but you do not need to know the physics of how they work to understand these two chapters.

Next, in [Chapter 12](#), I explain large semiconductor components like multiplexers and memories. In [Chapter 13](#), optoelectronics, I cover lasers and LEDs, and I end the book by discussing some simple concepts related to computer architectures and liquid crystal displays in [Chapter 14](#). I speculate about the future in [Chapter 15](#).

The objective of this book is to explain to the layman how semiconductors work and how they are used. I hope I have succeeded. If you have any comments or if you find errors, inconsistencies, unclear, incomplete or confusing figures or explanations, please let me know by emailing me at [semiconductorbasics@hotmail.com](mailto:semiconductorbasics@hotmail.com).

I had a professor who taught me relativistic quantum mechanics, one of the hardest courses I ever took, who used to say, "Everything mathematical is trivial." I agree with him, not 100%, but partially so. The truth is that we scare the hell out of young students by making them believe that mathematics, physics, and engineering are difficult. Wrong! Math is not difficult and physics, and all its derivatives, is fascinating.

*March 2019*

*So please enjoy.

George Domingo*

# 1

## The Bohr Atom

### OBJECTIVES OF THIS CHAPTER

To understand how semiconductors work and how they are used, we need to be familiar with the concept of allowed energy levels first proposed by Niels Bohr. How Bohr came up with the idea of a planetary model of the atom is very interesting. Science is a continuum: one observation leads to a hypothesis that leads to a theory that leads to more observations, and so on. Bohr did not come up with his model of the atom out of the blue – no apple fell on his head. A lot of observations and theories going back to the 1700s were proposed before he put them together in a now well-known theory.

In this chapter, I discuss the experimental evidence and the scientific observations that led to Bohr's planetary model of the atom and the discrete energy levels it postulated. This brief journey will help us understand the significance of the Bohr atom that explains the strange behavior of light spectra.

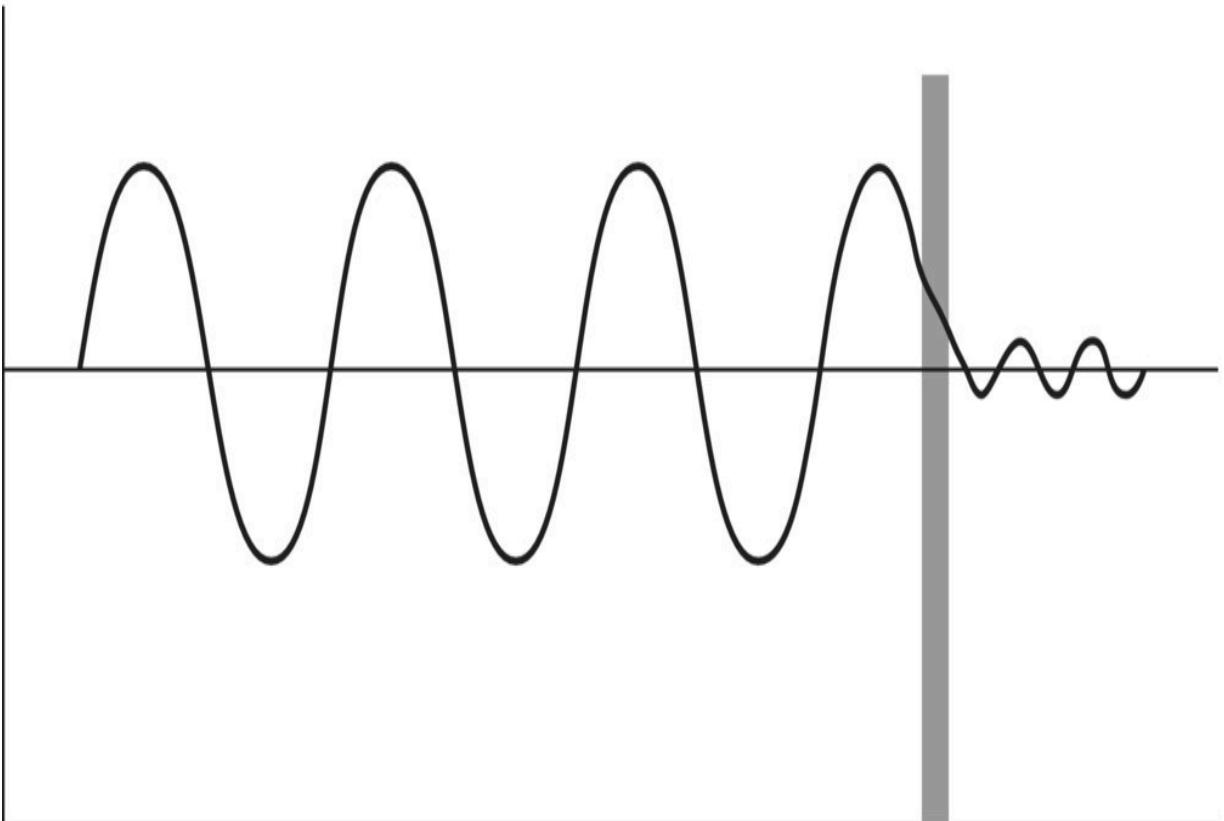

### 1.1 Sinusoidal Waves

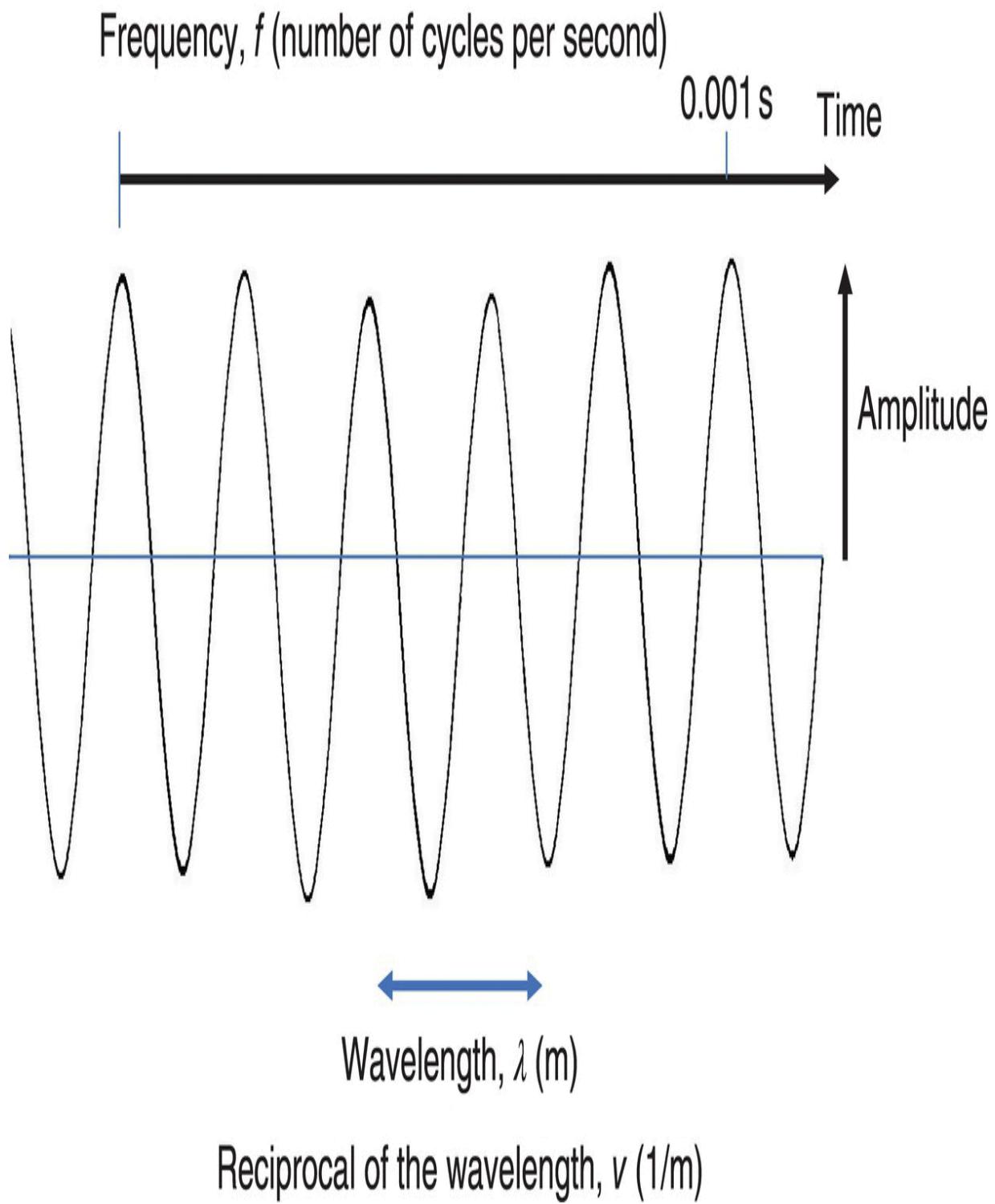

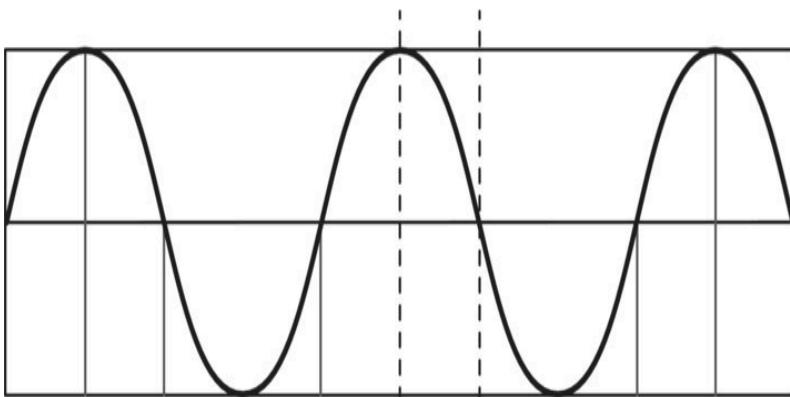

Before I start, I want to clarify the terms used to define a wave, which I use in the next few sections, and the relations between these terms (see [Figure 1.1](#)). There are four variables that we use to define any sinusoidal wave:

The *amplitude*,  $A$ : How high each peak of the wave is in relation to the middle, its zero value.

The *frequency*,  $f$ : The number of ups and downs in the wave in a given time. The units are Hertz or number of ups and downs per second: a number/s.

The *wavelength*,  $\lambda$ : The distance between two peaks, in meters (m), centimeters (cm), or micrometers ( $\mu\text{m}$ ).

The *wave number*,  $\nu$  (the Greek letter nu, not the letter  $v$ ): The reciprocal of the wavelength. Some properties of waves are better expressed by the reciprocal of the wavelength. The units are therefore  $1/\text{m}$  or  $\text{m}^{-1}$ , or  $\text{cm}^{-1}$ , or  $\mu\text{m}^{-1}$ .

The last three variables are related by the velocity of the wave. *Velocity* is the distance that a moving object covers during a fixed amount of time, so the velocity  $v$  (this is now the letter  $v$ ) has units of meters per second (m/s). The key relationships are

$$f = \frac{v}{\lambda} \quad \text{or} \quad \lambda = \frac{v}{f} \quad (1.1)$$

and the wave number – the reciprocal of the wavelength – is

$$\nu = \frac{1}{\lambda} = \frac{f}{v} \quad (1.2)$$

For example, suppose that [Figure 1.1](#) represents a sound wave. The velocity of sound in air is  $343 \text{ m s}^{-1}$ . Take a look at [Figure 1.1](#):

The figure shows 5 cycles in 0.001 seconds, which means the frequency is 5000 cycles per second or  $f = 5000 \text{ Hz}$ , (where Hz, Hertz is the unit for frequency) which happens to be the middle of our hearing range.

The wavelength is the velocity divided by the frequency, or  $\lambda = 343 (\text{m s}^{-1})/5000 (1 \text{ s}^{-1}) = 0.069 \text{ m}$  or 6.9 cm. Notice that the seconds cancel out, and therefore the units are in meters or centimeters.

The wave number is  $\nu = 1/0.069 \text{ m} = 14.5 \text{ m}^{-1}$ .

As much as possible, I use the metric system of units (MKS, meter, kilogram, second). I have always found it very annoying when books keep changing the unit system. When necessary, I will give you the equivalents.

**Figure 1.1** A sinusoidal wave is described in several ways: frequency, wavelength, and reciprocal of the wavelength plus its amplitude.

Now we are ready to dive into the pre-history of the Bohr atom and understand how Dr. Bohr came up with his famous model.

## 1.2 The Case of the Missing Lines

To explain how semiconductors work, we start with the Bohr atom. Most readers are familiar with Bohr's planetary model of the atom. How Bohr came up with this model is a very interesting scientific historical path involving many famous scientists of the nineteenth and early twentieth centuries. Science goes one step at a time.

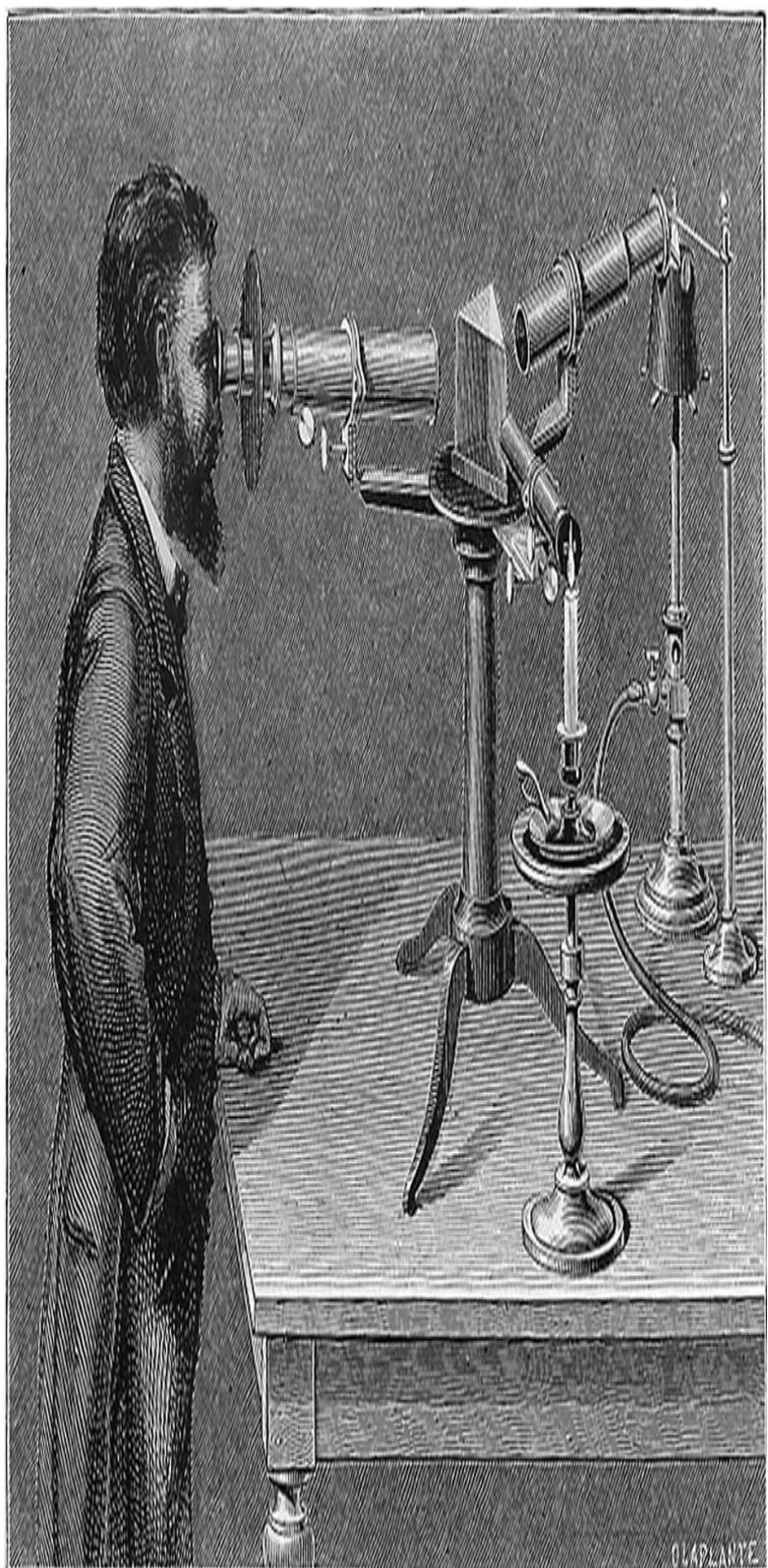

William Wollaston (1766–1826), shown on the left in [Figure 1.2](#), was an English chemist who discovered a couple of atomic elements, including palladium and rhodium. Very early in the 1800s, he built the first spectrometer. Wollaston focused the light from the sun through a prism and, to his surprise, found black lines partitioning the spectra ([Figure 1.3](#)). What the heck was going on?

*Engraved by W. H. W.*

W. H. WOLLASTON.

*From the original Picture by J. Jackson

in the possession of the Royal Society.*

**Figure 1.2** William Wollaston (left) looked at the sun's light through a prism and was the first to observe the missing lines.

Source: <https://library.si.edu/image-gallery/73731>. Joseph von Fraunhofer (right) studied the missing lines with his spectrometer and named them A–K. where Hz, Hertz is the unit for frequency.

<https://www.kruess.com/en/campus/spectroscopy/history-of-spectroscopy/>

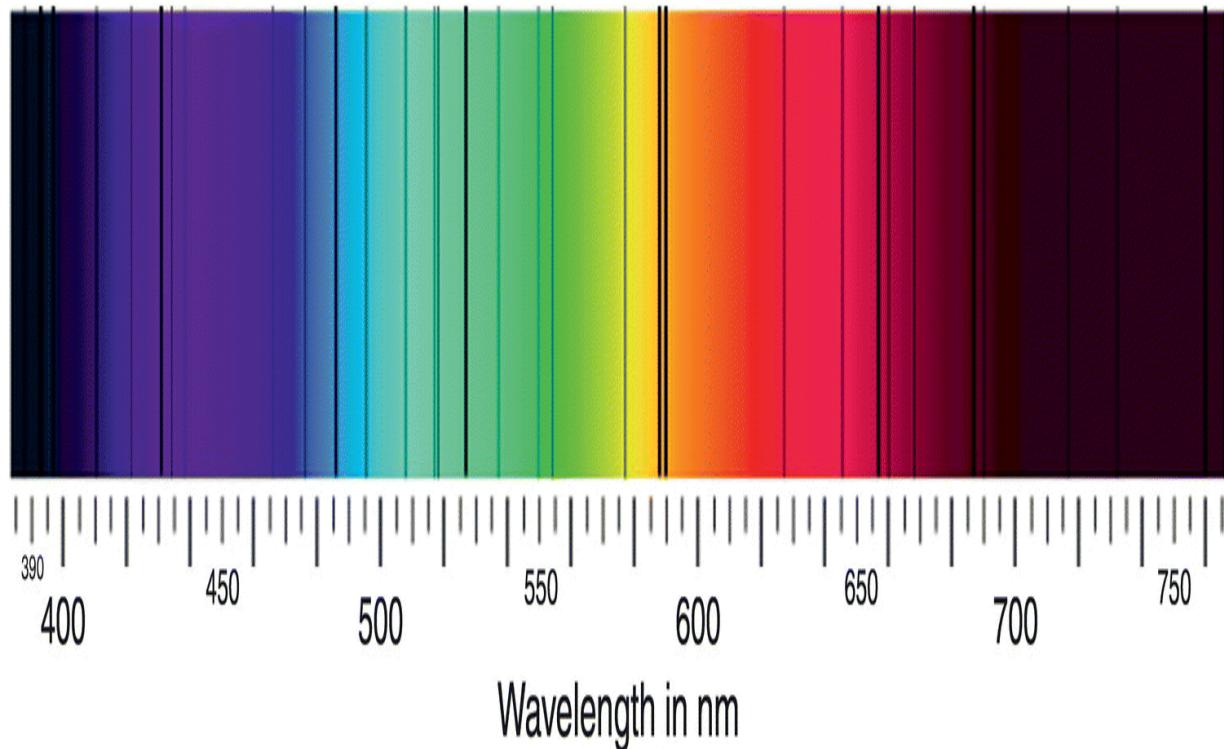

**Figure 1.3** The sun's spectrum through a prism shows dark lines: wavelengths of light that seem to have disappeared.

Source: <https://www.kruess.com/en/campus/spectroscopy/history-of-spectroscopy/>.

Suppose you are roasting a chicken and carefully watching the dial of a digital thermometer inserted in the chicken's breast as the temperature increases from room temperature, 24 °C (degrees Celsius), to 80 °C, the recommended internal temperature of a well-cooked chicken breast. As the temperature increases, suddenly the thermometer jumps from 39 °C to 41 °C, then from 56 °C to 58 °C, and finally from 66 °C to 68 °C. You wonder what is wrong with the thermometer: why don't the temperatures 40, 57, and 67 °C show

up on the dial? They don't seem to exist. You buy a new thermometer, just to be sure, and find that exactly the same temperature values are missing. A third thermometer gives the same results. You place the same thermometers in soup, and the thermometers are well behaved, showing in succession the values 39, 40, and 41 °C. So, the thermometers work. The missing temperatures are no coincidence. There is something in that chicken that makes the temperature jump from one value to another without passing through the one in the middle.

Well, that was probably Wollaston's initial reaction. What separated the colors? Was the instrument lens dirty? He even considered the possibility that there were natural boundaries between certain colors. But why didn't these black boundaries appear when he pointed the spectrometer at a white light?

German physicist Joseph von Fraunhofer (1787–1826), on the right in [Figure 1.2](#), studied these dark lines of the sun's spectrum in much more detail and actually named the missing lines with the letters A–K (not too imaginative; ancient astronomers would have found much more attention-grabbing names).

## 1.3 The Strange Behavior of Spectra from Gases and Metals

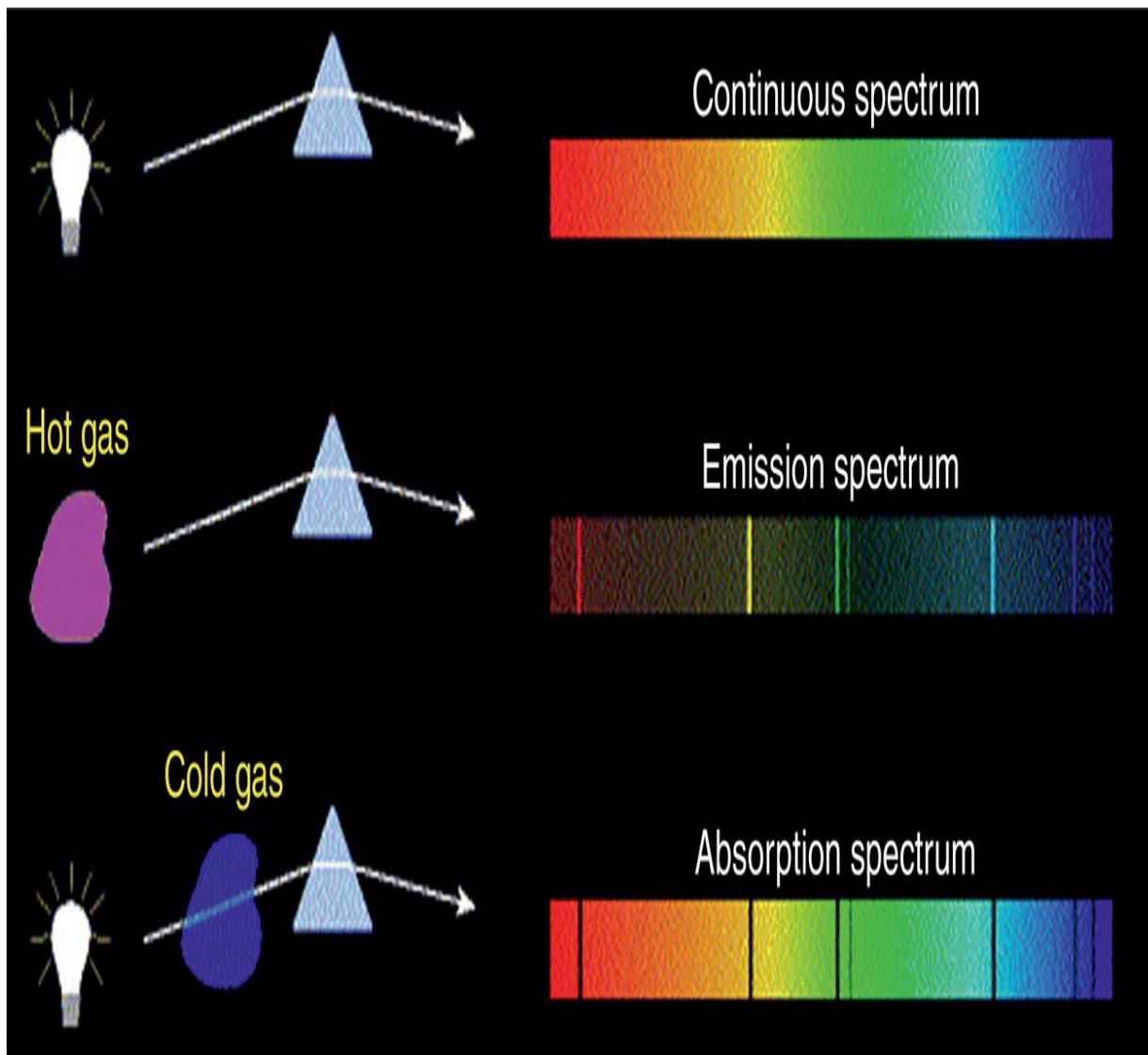

The next step was to take a look at the emission of light from several metals, gases, and stars. The observers soon found that each element has its own unique set of lines. Take a look at [Figure 1.4](#). White light through a prism generates a continuous spectrum (top diagram); no colors are missing. If we heat a gas until it glows and pass the light through the same prism (middle diagram), only certain lines are projected onto the screen: the rest of the spectrum has disappeared. But if we do it differently – that is, if we have the cold gas between the white light and the prism (bottom diagram) – then the full spectrum appears, except for *exactly* the same lines that were visible in the previous spectral measurement. The

superposition of the middle and lower spectra is equal to the spectrum of the white light at the top. The gas, when cold, absorbs the same specific light waves as the ones it emits when it glows. What a coincidence! And this happens with *all* gases and materials. The lines are at different frequencies, but all of them have lines.

**Figure 1.4** The spectrum from any gas shows similar but different missing lines (middle image), but when the same gas is hot and emits light, only the lines that were black before are now visible (lower image).

Source: <https://quizlet.com/102018176/astronomy-4-spectroscopy-flash-cards/>.

## 1.4 The Classifications of Basic Elements

In 1766, an English aristocrat named Henry Cavendish (1731–1810) was the first to recognize hydrogen as an element, that is, a unique substance and an integral part of the water molecule. By the time Dmitri Mendeleev (1834–1907) published his now ubiquitous periodic table of the elements in 1869, 100 years later, it was already known that hydrogen was the lightest of all the known elements (at that time, 60 elements were known). Mendeleev ([Figure 1.5](#)) reordered the known elements by their relative atomic weight, with hydrogen as 1.

| H<br>1.01  | II         | III        | IV         | V          | VI         | VII        | VIII       |            |            |

|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

| Li<br>6.94 | Be<br>9.01 | B<br>10.8  | C<br>12.0  | N<br>14.0  | O<br>16.0  | F<br>19.0  |            |            |            |

| Na<br>23.0 | Mg<br>24.3 | Al<br>27.0 | Si<br>28.1 | P<br>31.0  | S<br>32.1  | Cl<br>35.5 |            |            |            |

| K<br>39.1  | Ca<br>40.1 |            | Ti<br>47.9 | V<br>50.9  | Cr<br>52.0 | Mn<br>54.9 | Fe<br>55.9 | Co<br>58.9 | Ni<br>58.7 |

| Cu<br>63.5 | Zn<br>65.4 |            |            | As<br>74.9 | Se<br>79.0 | Br<br>79.9 |            |            |            |

| Rb<br>85.5 | Sr<br>87.6 | Y<br>88.9  | Zr<br>91.2 | Nb<br>92.9 | Mo<br>95.9 |            | Ru<br>101  | Rh<br>103  | Pd<br>106  |

| Ag<br>108  | Cd<br>112  | In<br>115  | Sn<br>119  | Sb<br>122  | Te<br>128  | I<br>127   |            |            |            |

| Ce<br>133  | Ba<br>137  | La<br>139  |            | Ta<br>181  | W<br>184   |            | Os<br>194  | Ir<br>192  | Pt<br>195  |

| Au<br>197  | Hg<br>201  | Ti<br>204  | Pb<br>207  | Bi<br>209  |            |            |            |            |            |

|            |            |            | Th<br>232  |            | U<br>238   |            |            |            |            |

**Figure 1.5** Dmitri Mendeleev and the periodic table with the elements known in his time and the empty slots for elements still to be discovered.

Source: Wikipedia,

[https://en.wikipedia.org/wiki/Dmitri\\_Mendeleev#/media/File:Dmitri\\_Mendeleev\\_1890s.jpg](https://en.wikipedia.org/wiki/Dmitri_Mendeleev#/media/File:Dmitri_Mendeleev_1890s.jpg).

## 1.5 The Hydrogen Spectrum Lines

Johann Balmer (1825–1898), a Swiss mathematician, found empirically in 1895 that the separation of the optical lines generated by hydrogen gas can be expressed by a formula using just a constant,  $C$ , and integer numbers. He expressed his observation with [Eq.\(1.3\)](#).

$$\lambda = \frac{Cm^2}{m^2 - n^2} \quad (1.3)$$

here  $\lambda$  is the wavelength of the missing line,  $C$  is a heuristically obtained constant ( $C = 3.64 \times 10^{-9}$  m),  $n = 2$ , and  $m$  is an integer greater than 2 (i.e. 3, 4, 5, and so on). When you put any of these integer numbers in [Eq.\(1.3\)](#), you get the wavelength of all the lines in the hydrogen spectrum.

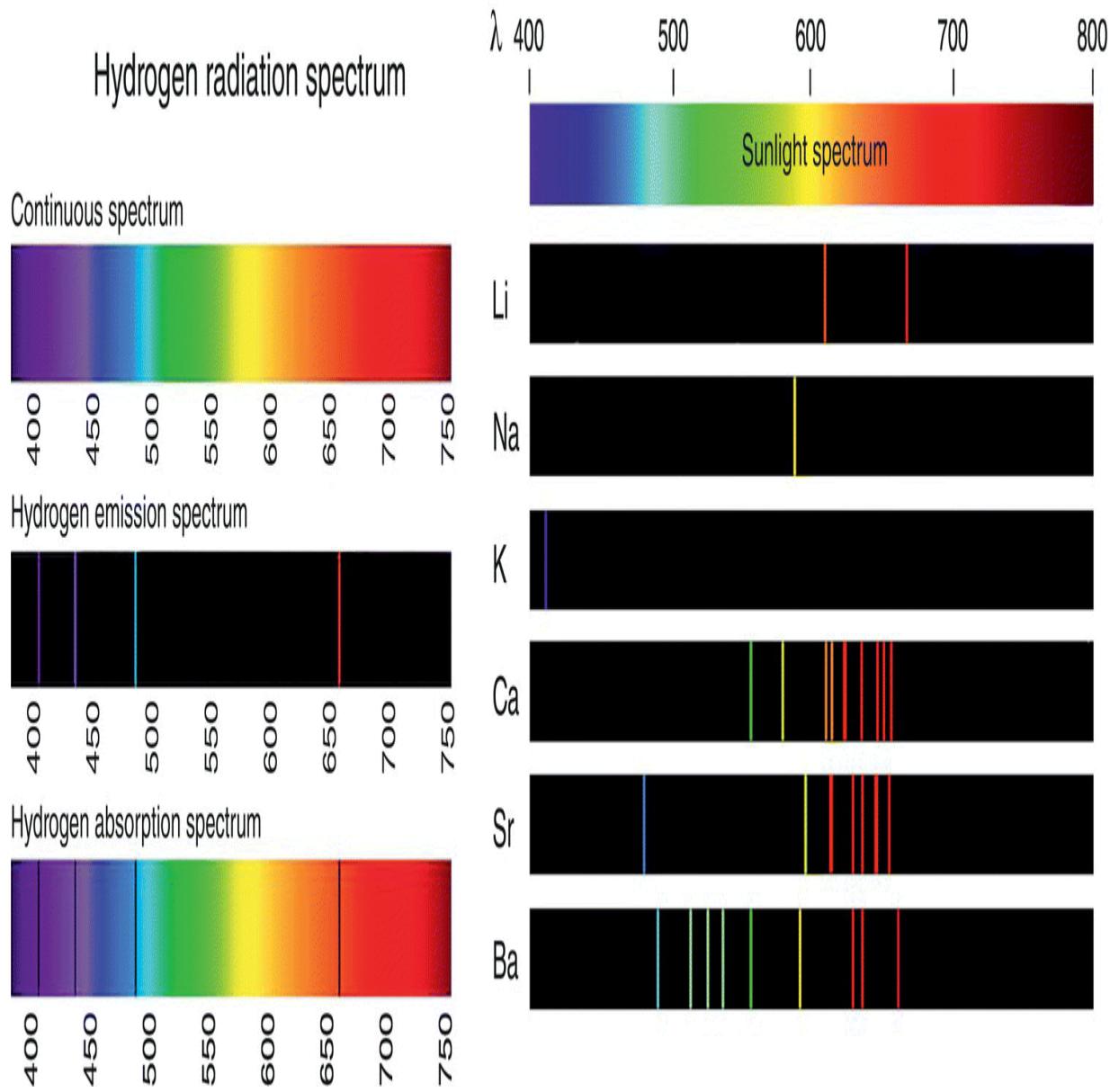

**Figure 1.6** The spectrum of the hydrogen atom on the left shows the absorption lines (below) and the emission lines (middle). On the right are the emission lines of several other materials.

Source: <https://www.shutterstock.com/image-vector/spectrum-spectral-line-example-hydrogen-emission-1288942888?src=iUiOwiDEznOcV6XzswXhMA-1-0> (left); <https://www.shutterstock.com/image-vector/line-spectra-elements-339037577?src=I6tWF1qlh6XcWayXsZl-Gw-3-16> (right).

**Figure 1.6** shows the hydrogen spectrum on the left, with its characteristic emission and absorption lines. These are the lines that

Balmer used to develop [Eq. \(1.3\)](#) to calculate the missing hydrogen's wavelengths. All the elements have similar absorption and emission lines at different wavelengths, and I show a few on the right in [Figure 1.6](#).

Just three years later, Johannes Rydberg (1854–1919) found that the Balmer equation was one specific case of a more general formula, [Eq. \(1.4\)](#):

$$v = \frac{1}{\lambda} = R \left[ \frac{1}{n^2} - \frac{1}{m^2} \right] \quad (1.4)$$

The reciprocal of the wavelength is now given by a constant  $R$  and the same integer numbers, except that now  $n$  is allowed to have different integer numbers: 2, 3, 4, and so on.  $R$  is also a heuristically derived constant ( $R = 1.1 \times 10^7 \text{ m}^{-1}$ ), called the *Rydberg constant*. Both Balmer and Rydberg ([Figure 1.7](#)) were able to quantify the entire spectrum of the hydrogen atom using the relationship in [Eq. \(1.4\)](#). It is interesting that Niels Bohr, whom I'll talk more about in [Section 1.8](#), was able to calculate the Rydberg number using fundamental physical values, such as the mass of the electron, the electronic charge, the permittivity of free space, Planck's constant, and the speed of light (see [Appendix 1.3](#)). This behavior screams for an explanation.

**Figure 1.7** Johann Balmer (left) found a mathematical relation for hydrogen's spectral lines, and Johannes Rydberg (right) came up with a more general equation applicable to all gases and materials.

Source Wikipedia,

[https://en.wikipedia.org/wiki/Johann\\_Jakob\\_Balmer#/media/File:Balmer.jpeg](https://en.wikipedia.org/wiki/Johann_Jakob_Balmer#/media/File:Balmer.jpeg)

(left); Wikipedia,

[https://en.wikipedia.org/wiki/Johannes\\_Rydberg#/media/File:Rydberg,\\_Janne\\_\(foto\\_Per\\_Bagge,\\_AFs\\_Arkiv\).jpg](https://en.wikipedia.org/wiki/Johannes_Rydberg#/media/File:Rydberg,_Janne_(foto_Per_Bagge,_AFs_Arkiv).jpg) (right).

## 1.6 Light is a Particle

Albert Einstein (1879–1955, [Figure 1.8](#)) published a paper in 1905 on the theory of the photoelectric effect. When light strikes a metal surface, it frees an electron if its energy is higher than a given threshold value. Any remaining energy is used to kick the electron off the surface. In his paper, Einstein proposed the concept that light has a dual personality; it behaves like a wave or like a particle, and the particle has an energy associated with the wavelength of that light.

He called this particle a “light quantum.” (In 1926, a French physicist named Frithiof Wolfers [1891–1971] renamed the light quantum a *photon*. It is interesting that Einstein received the Nobel Prize in 1921 for the discovery of the photon, not for his much more famous work on relativity.) This light particle, the photon, has an energy that depends on the frequency of the light. The energy associated with this light is given by the formula

$$E = hf = \frac{hc}{\lambda} \quad (1.5)$$

where  $h$  is Planck's constant ( $h = 6.63 \times 10^{-34} \text{ m}^2 \text{ kg s}^{-1}$ ),  $c$  is the speed of light ( $c = 3 \times 10^8 \text{ m s}^{-1}$ ), and  $\lambda$  is the wavelength (m). The meter in the numerator cancels the one in the denominator, resulting in the energy given in Joules ( $= \text{kg m}^2 \text{ s}^{-2}$ ).

**Figure 1.8** Around 1905, Albert Einstein came up with the concept that light behaves as both a wave and a particle.

Source: Wikipedia,

[https://en.wikipedia.org/wiki/Albert\\_Einstein#/media/File:Einstein\\_patentoffice.jpg](https://en.wikipedia.org/wiki/Albert_Einstein#/media/File:Einstein_patentoffice.jpg).

## 1.7 The Atom's Structure

While all of these light experiments and relationships were being observed in the late nineteenth century, other scientists were playing with cathode-ray tubes, the precursors of old television sets and oscilloscopes, trying to understand the nature of the atom. The cathode-ray tube consists of an evacuated tube with two contacts, one at each end: the *cathode* and the *anode*. When a voltage is applied across the tube, current flows from the cathode to the anode, and the tube glows. The scientists explained this phenomenon by saying that electrons going through an evacuated tube containing very few atoms are able to attain sufficient velocity (and therefore kinetic energy) to hit the atoms and make them glow. They were called *cathode rays*.

Nobel Prize winning British physicist Joseph John Thomson (1856–1940, [Figure 1.9](#)) studied cathode rays and postulated in 1897 that they consisted of extremely small negatively charged particles, which he initially called “corpuscles.” (As happened with the term *photon*, George Stoney (1826–1911) later renamed corpuscles as *electrons*.) By studying how these particles moved through the gas and how they could be deflected by magnets, Thomson concluded that the “corpuscles” were (i) negatively charged particles and (ii) much smaller than the atoms themselves – at least 1000 times smaller. To account for electrically neutral atoms, he proposed that there is a core of positive charges with a large mass surrounded by an amorphous cloud of negatively charged electrons.

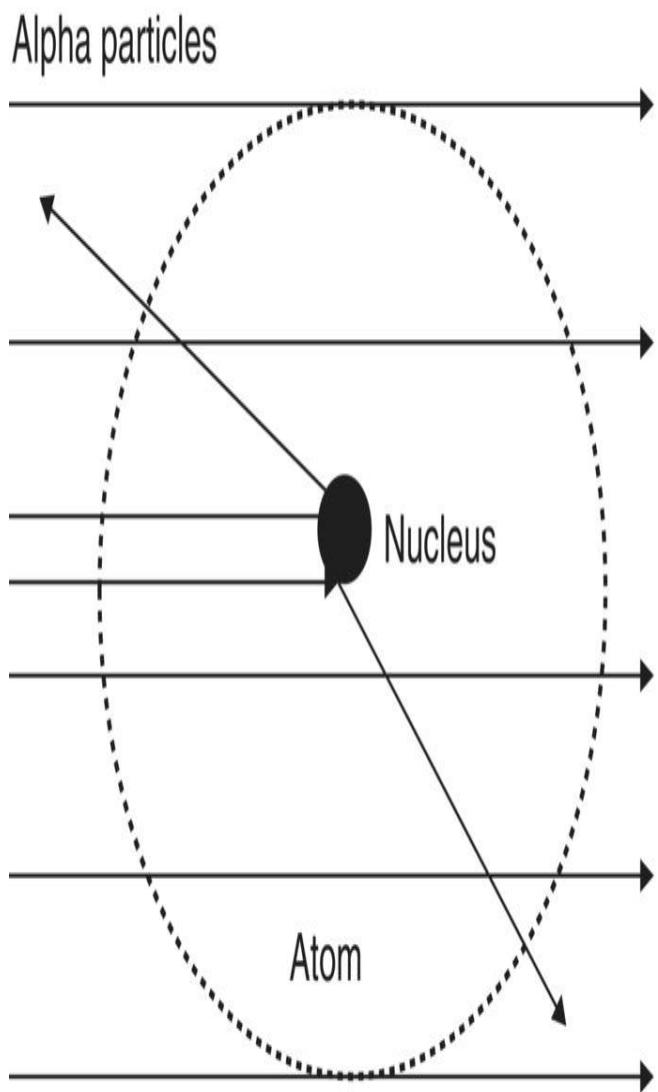

Ernest Rutherford (1871–1937, [Figure 1.10](#)), also a Nobel Prize winner, worked with radioactivity. In 1911, he bombarded very thin gold foil with alpha particles and looked at the scattered reflections

as the radiation went through the foil. Most of the radiation went through the foil undeflected. Only a few alpha particles were reflected back and, from the angle of the reflected radiation, he concluded that the atom must have a very small, concentrated, positively charged core to compensate for the negatively charged electrons. Because the large majority of alpha particles passed through the foil without any directional change, he concluded that the majority of the space in an atom is empty, and the electrons are orbiting the nucleus instead of just being a scrambled negatively charged cloud as Thomson had suggested.

**Figure 1.9** Joseph John Thomson and his cathode ray tube.

Source: Wikipedia,

[https://en.wikipedia.org/wiki/J.\\_J.\\_Thomson#/media/File:JJ\\_Thomson\\_Cathode\\_Ray\\_2.png](https://en.wikipedia.org/wiki/J._J._Thomson#/media/File:JJ_Thomson_Cathode_Ray_2.png) (left); Wikipedia,

[https://en.wikipedia.org/wiki/J.\\_J.\\_Thomson#/media/File:J.J\\_Thomson.jpg](https://en.wikipedia.org/wiki/J._J._Thomson#/media/File:J.J_Thomson.jpg) (right).

**Figure 1.10** Ernest Rutherford, with his experiment that bombarded alpha particles with radiation, concluded that the nucleus is extremely small and is concentrated at the center of the atom.

*Source:* Wikipedia,

[https://upload.wikimedia.org/wikipedia/commons/6/6e/Ernest\\_Rutherford\\_LOC.jpg](https://upload.wikimedia.org/wikipedia/commons/6/6e/Ernest_Rutherford_LOC.jpg).

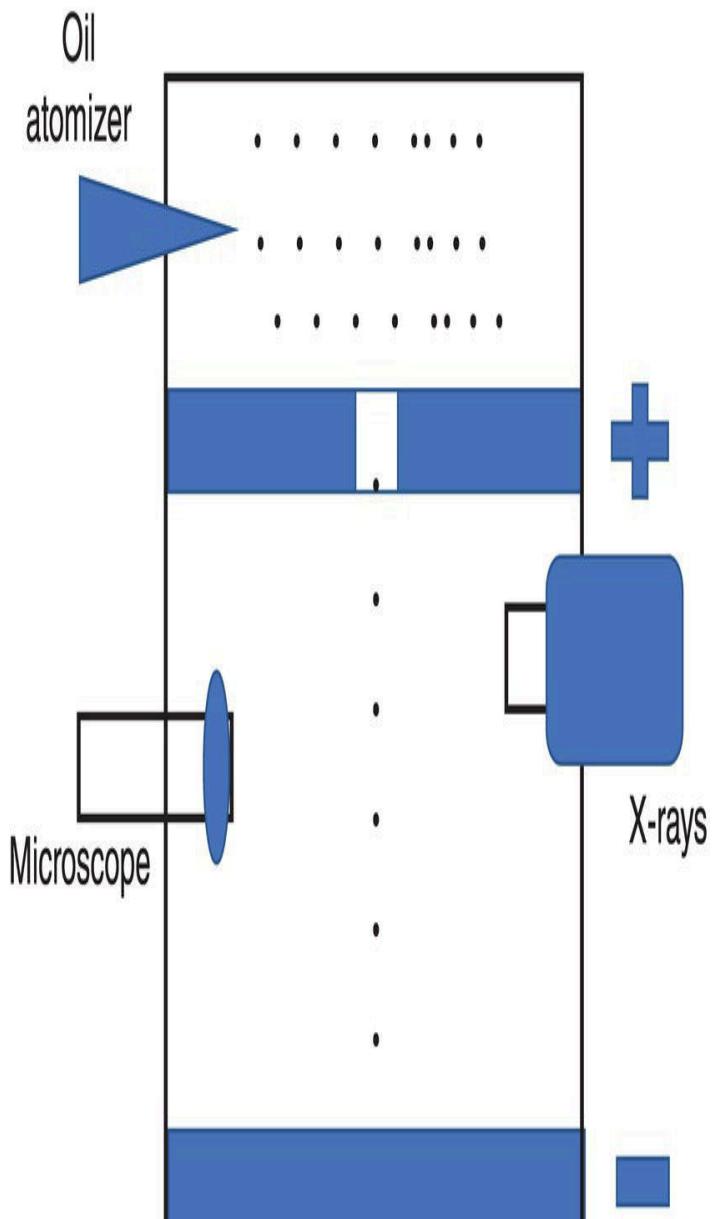

Robert Millikan (1868–1953, [Figure 1.11](#)) was able to measure the electrical charge of an electron with an interesting oil drop experiment in 1909. He suspended a very small charged oil drop between two metal plates – one positive and the other negative – creating an electric field between the plates. He dropped tiny oil droplets into a vacuum chamber, and with X-rays, he negatively charged some of the oil drops. By changing the electric field between the two plates, he could control the speed of the oil drops, slowing them down, stopping them, or even moving them upward. By knowing the density of the oil drop, the size of the drop, its volume and mass, and the electric field that compensated for the effect of gravity, he was able to come up with the value of the charge of a single electron:  $1.592 \times 10^{-19}$  coulombs (he was off by less than 1% of the now-established number – not bad at all).

**Figure 1.11** Robert Millikan, with his oil-drop experiment, measured the electrical charge of an electron.

*Source:*

[https://en.wikipedia.org/wiki/Robert\\_Andrews\\_Millikan#/media/File:Millikan.jpg](https://en.wikipedia.org/wiki/Robert_Andrews_Millikan#/media/File:Millikan.jpg)

## 1.8 The Bohr Atom

So here we are in 1913 (just a mere 105 years ago at the time of this writing). What did Bohr know? He knew:

That a hydrogen atom is the simplest atom, consisting of just one proton (positively charged) and one electron (negatively charged).

That all of the atom's mass is concentrated at the core: that is, the proton.

That electrons are negative particles somehow orbiting the nucleus.

That the great majority of space in an atom is empty.

That all the other elements can be organized neatly by weight on a periodic table.

That all elements have different emission spectra with specific emission or absorption color lines.

Niels Bohr (1885–1962, [Figure 1.12](#)) was able to beautifully explain all of these observations and how the spectral lines are generated. He postulated in 1912 that an atom consists of a core nucleus that has all the mass and is surrounded by electrons, moving like a planetary system in well-defined orbits ([Figure 1.13](#)). Electrostatic forces between the proton and the electron (analogous to the gravitational forces in the solar system) keep the electrons circulating without escaping their orbit. Additionally, Bohr postulated that the electrons in orbit do not radiate any energy, so the orbits are stable. The only way to radiate or absorb any energy is for an electron to jump from one orbit to another, and that is precisely what explains the spectra of hydrogen and other elements.

**Figure 1.12** Niels Bohr (left) postulated the planetary model of the atom. Wolfgang Pauli (right), using quantum mechanics, proved that no two electrons in a system can have the same quantum numbers.

Source: Wikipedia,

[https://en.wikipedia.org/wiki/Niels\\_Bohr#/media/File:Niels\\_Bohr.jpg](https://en.wikipedia.org/wiki/Niels_Bohr#/media/File:Niels_Bohr.jpg) (left);

Wikipedia, [https://en.wikipedia.org/wiki/Wolfgang\\_Pauli#/media/File:Pauli.jpg](https://en.wikipedia.org/wiki/Wolfgang_Pauli#/media/File:Pauli.jpg) (right).

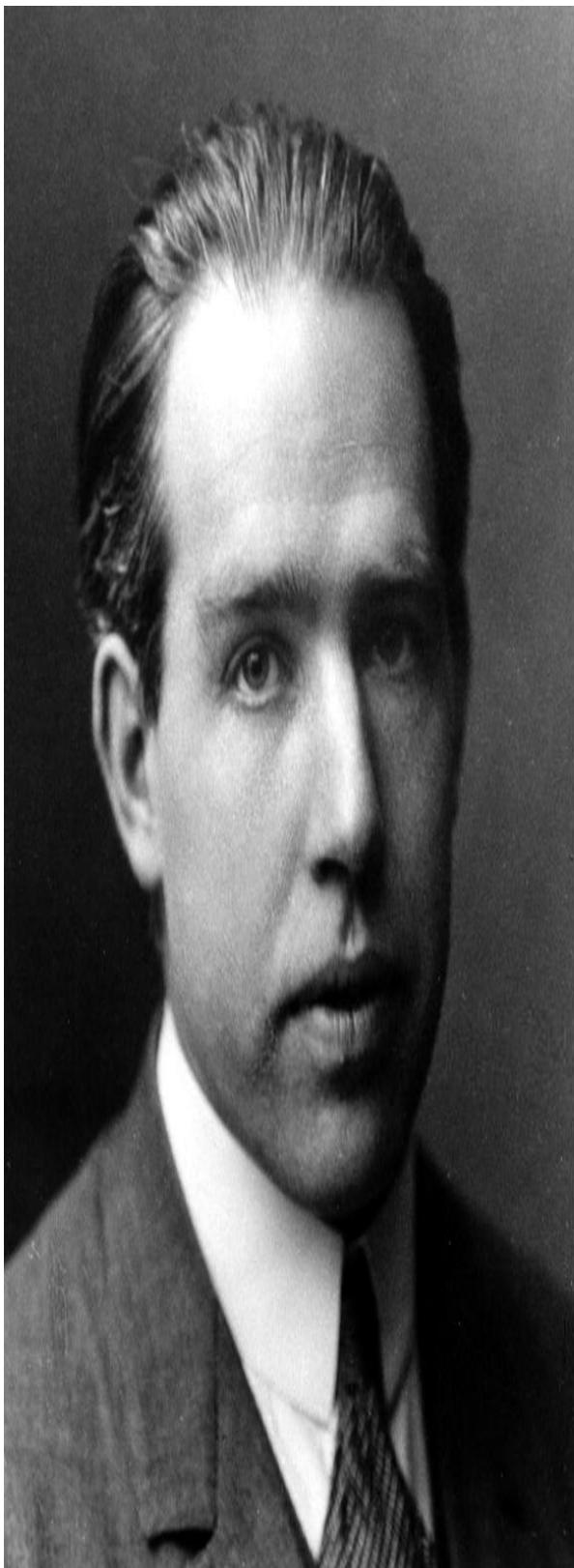

**Figure 1.13** The Bohr planetary model of an atom has discrete and stable orbits. An electron falling from level 3 to level 2 transfers its energy to an equivalently energetic photon.

Since electrons are forbidden to have any energy except for the

energy of a specific orbit, they have to jump from one orbit to another, like going up the stairs, one, two, or three steps at a time (not one and a half). When falling from a higher orbit to a lower one, the electron releases a fixed packet of energy in the form of a photon of a very precise frequency (remember that Einstein said light behaves like a particle with an energy related to the wavelength of the light: [Eq. 1.5](#)). The transition from orbit 3 to orbit 2, as I show in [Figure 1.13](#), results in the emission of a photon of a very precise frequency, given by the change in energy,  $\Delta E$ , divided by Planck's constant. Similarly, if an electron in orbit 2 wants to jump to orbit 3, the hydrogen atom has to absorb the energy it needs by absorbing a photon with the same precise energy, or by thermal heating, or by some other means. All other light photons not exactly matched to the difference between the energy levels go through the material unimpeded. The material is therefore transparent for all of the light waves that do not match the exact difference between two energy levels.

In 1924, Austrian Wolfgang Pauli (1900–1958, on the right in [Figure 1.12](#)) proposed his exclusion principle, which states that no two electrons (or fermion particles) in a system can have the same quantum numbers. The first atomic level of any element can hold only 2 electrons, the second 8, the third 18, the fourth 32, etc. A simple relation tells you how many electrons can share a given energy orbit:  $2n^2$ . You may wonder why. If, according to Pauli's exclusion principle, the electrons cannot share the same quantum state, why do we have more than one electron in each orbit? The answer is that each electron is described by four quantum numbers (like the three numbers that describe your first, middle, last names, and your date of birth), but only the first quantum number,  $n$ , specifies the energy of the electron and thus explains the behavior of the light spectra. I explain the electron's four quantum numbers in more detail in [Appendix 1.1](#).

Here's an analogy. Suppose I have a theater with 2 seats in the first row, 8 in the second, 18 in the third, 32 in the fourth, etc. The

tickets for the first row cost \$20, the second row \$50, the third row \$75, the fourth \$125, and so on. (I know, it is a weird theater, but this is just an analogy.) Spectators are forbidden to sit in someone else's lap or stand in the aisles. If 12 people show up for the performance, they first occupy the 2 seats of the first row, the next 8 patrons occupy the second row, and the last 2 spectators sit somewhere in the third row. Further back in the theater, the rows have more seats, but they are empty. If a patron wants to change rows – from row 3 to row 4, for example – he has to pay the extra \$50: the difference in the price of the tickets in the different rows. If he moves the other way, from row 4 to row 3, he is reimbursed the \$50. Now, if a wealthy person in row 1 wants to move to row 4, he will be required to pay \$105. That is, money must be paid or received to move from one row to another. All these changes assume that the seat someone desires is unoccupied. If the group of spectators is short of money (no energy), they will occupy the seats of the first rows as long as there are seats available. If the group is wealthy (has lots of energy), they can jump from one seat to another as long as they have enough money (energy) to afford the higher prices. The amount they have to pay depends only on the difference in the price of the seats in each row. End of analogy.

At 0 K, absolute temperature ( $-273^{\circ}\text{C}$ ), there is no energy whatsoever, so all the electrons occupy the lowest allowed energy levels. At room temperature,  $300^{\circ}\text{C}$ , there is quite a large amount of thermal energy, and electrons start moving from one level to another, leaving empty seats that can be occupied by other electrons, absorbing or emitting photons as they move.

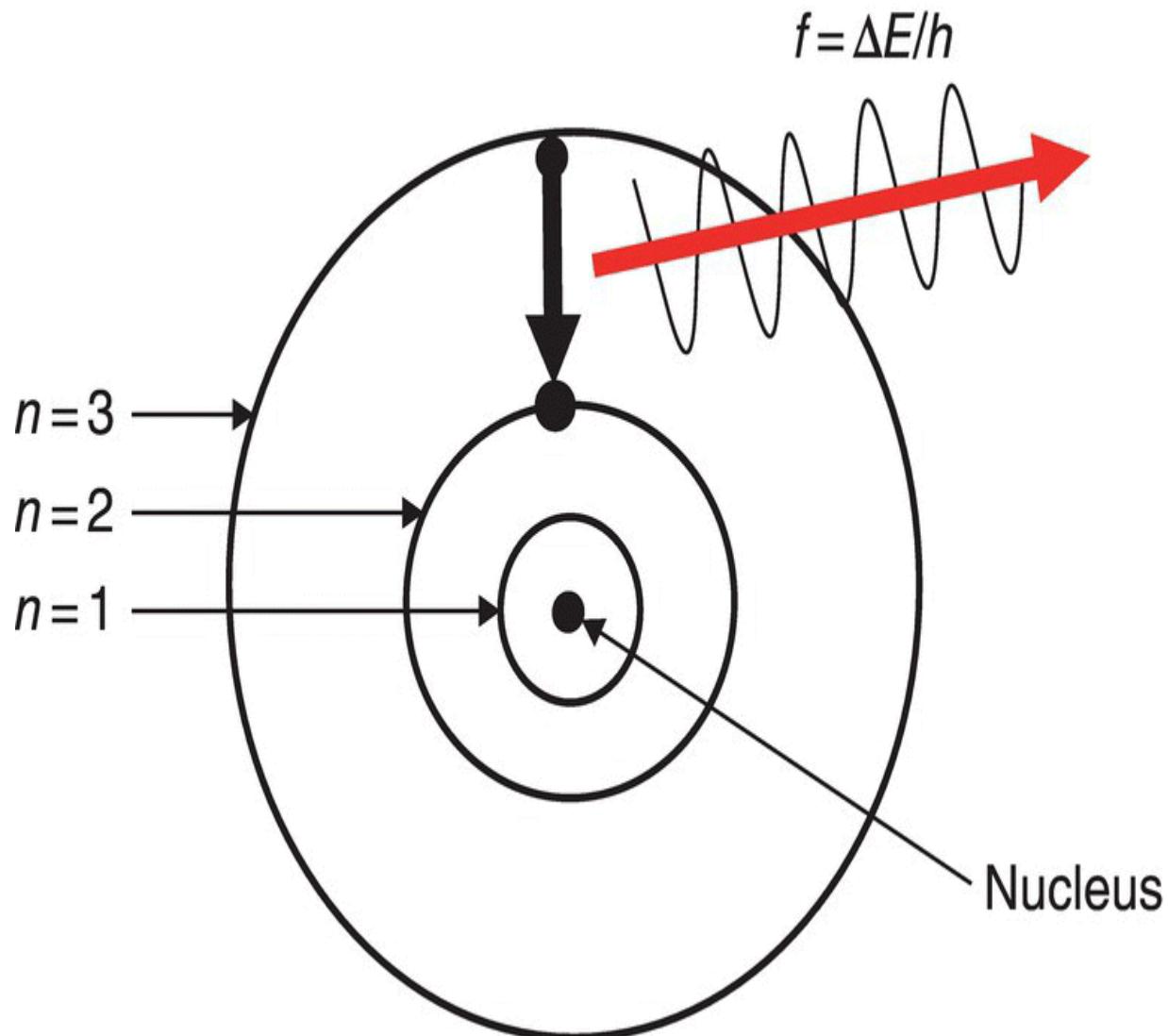

[Figure 1.14](#) shows the transitions observed in the hydrogen atom. The groups of lines were named later by those who found them.

Have you ever wondered why, when we walk on the second floor, we do not fall through it and land on the first floor? Think about it. The typical size of an atom is  $5 \times 10^{-10}\text{ m}$ , and the size of a nucleus is about 30 000 times smaller,  $1.6 \times 10^{-15}\text{ m}$ . All the mass is concentrated in the nucleus. The atoms are, for all practical

purposes, composed of empty space. So why does the empty space of my shoes do not go through the empty space of the tiles on the second floor? It is not due to electrostatic repulsion. Both the soles of my shoes and the tiles are electrically neutral. The reason we do not fall through the floor is the Pauli exclusion principle. The electrons in the sole cannot find a lower energy level on the atoms of the tile. The Pauli exclusion principle not only keeps us safe on the second floor but also explains why material physical objects have any volume at all. It also explains friction. The atoms of the sole locate themselves in a preferential position with the atoms of the floor, and they resist moving. How intense the friction is depends on the crystallographic structure of the two surfaces (Emily Conover, "Giving Friction the Slip", *Science News*, 3 August 2019).

**Figure 1.14** The observed energy lines of the hydrogen atom corresponding to all the transitions between different atomic levels.

In the next chapter, I discuss how these single unique energy levels that Bohr postulated explain the electric properties of different materials.

## 1.9 Summary and Conclusions

Perhaps the best way to summarize what we have covered in this chapter is to take a look at [Figure 1.15](#). Observations of the sun's light spectrum and the spectra of different gases with their distinct lines resulted in heuristic relationships that relate the frequency of the missing lines to an expression consisting of just a constant and integer numbers. Einstein, working with the photoelectric effect, postulated the dual nature of light acting as both a wave and a particle, which we now call the photon.

## Theory and experiments with light

## Atomic theory

1802 – Wollaston observes missing lines in the sun's spectrum

1850 – Spectra of gases show distinct lines

1895 – Balmer and Rydberg quantify the frequency of the hydrogen spectrum lines

1905 – Einstein postulates the light quanta, the photon

1912 – Bohr publishes his planetary model of the atom

1869 – Mendeleev classifies all known (and some unknown) elements in a periodic table

1897 – Thomson concludes electrons are tiny negatively charged particles

1910 – Millikan measures the charge of an electron

1911 – Rutherford finds that the atom's mass is concentrated at the center

**Figure 1.15** The scientific and experimental work that led to the Bohr planetary model of the atom.

On the atomic side, Mendeleev classified the known elements by their weight, and, in the process, he left some empty spaces to add future elements. Thomson determined that electrons are tiny negatively charged particles and Rutherford, with his alpha ray measurements, concluded that the nucleus is concentrated in a very small region at the center of the atom. Millikan was able to measure the charge of electrons.

Based on previous theoretical and experimental work, Bohr proposed his planetary model of the atom with discrete and stable energy levels. His model included all the developments of atomic theory known to that date and explained the previous optical observations and measurements beautifully by considering how electrons move from one level to another by accepting or releasing packets of energy.

If you are comfortable with these conclusions, you are ready to go to the next chapter. You may peruse the three following appendices for a few more details.

## Appendix 1.1 Some Details of the Bohr Model

Four quantum numbers uniquely define an electron:

The principal quantum number,  $n$ , defines the orbits and, therefore, the energy of the electrons. The energy released or absorbed as the electrons change orbits is determined exclusively by the value of  $n$ . The allowed values of  $n$  are any positive integers: 1, 2, 3, 4, etc.

Electrons have two spins: up and down.

Electrons also have angular momentum. The angular quantum number,  $\ell$ , is associated with the shape of the orbits. The value of  $\ell$  is also an integer number between 0 and  $n$ .

The magnetic quantum number,  $m_l$ , is associated with the orientation of the orbits. It is also an integer number between  $-l$  and  $+l$ .

Electrons follow these rules:

The electrons in the first orbit,  $n = 1$ , can have two spins, but both  $l$  and  $m_l$  are 0. Thus the first orbit can hold only two electrons.

The electrons in the second orbit,  $n = 2$ , can have two spins and two angular quantum numbers ( $l$  equal to 0 or 1). Associated with  $l = 0$ , only one  $m_l$  value is possible,  $m_l = 0$ . But for  $l = 1$ , there are three possible values of  $m_l$ :  $-1$ ,  $0$ , and  $+1$ . So, the total number of electrons in the second orbit is eight: that is, four  $m_l$  times two spins each.

You can do the calculations and prove that the third orbit can hold up to 18 electrons, and so on.

[Figure 1.16](#) shows one way of visualizing these levels, including the relative energy of the orbits of the Bohr atom and the order in which the orbits are filled. At 0 K absolute temperature, the electrons first fill up the 1s band (two electrons), the next two electrons reside in the 2s band, and the next six are in the 2p band, etc., climbing up the energy level stairs. Note that level 4s fills up before 3d. (By the way, the letters mean s for sharp, p for principle, d for diffuse, and f for fundamental.)

Another point you may wonder about is why we write the 3d level at higher energy than the 4s level. There is quite a debate about explaining this. It has to do with the attraction and repulsion of electrons and protons, and I will leave it at that.

| Subshell | s | p | d | f |

|----------|---|---|---|---|

|          | 7 | 6 | 6 | 5 |

|          | 6 | 5 | 5 | 4 |

|          | 5 | 4 | 4 |   |

|          | 4 | 3 | 3 |   |

|          | 3 | 2 |   |   |

|          | 2 |   |   |   |

|          | 1 |   |   |   |

|          |   |   |   |   |

2      6      10      14

Maximum number of electrons per shell

[\*\*Figure 1.16\*\*](#) Subshell electron capacity. Notice that the number of sites in each level increases as the energy level,  $n$ , increases. Also notice that the 3d level has lower energy than the 4s level.

## Appendix 1.2 Semiconductor Materials

[\*\*Figure 1.17\*\*](#) shows the portion of the periodic table that contains the elements used in semiconductors, showing how many electrons are in the upper shells. All the lower shells are full. Silicon, for example, has 14 electrons, so the electrons fill up bands 1s (2), 2s (2), 2p (6), 3s (2), and 2p (the last 2). If you superimpose these numbers into [\*\*Figure 1.16\*\*](#), you see that the two lowest energy levels are full, but energy level  $n = 3$  (s + p) has four electrons, with the possibility of accepting another four (in the 2p level) to complete its orbit.

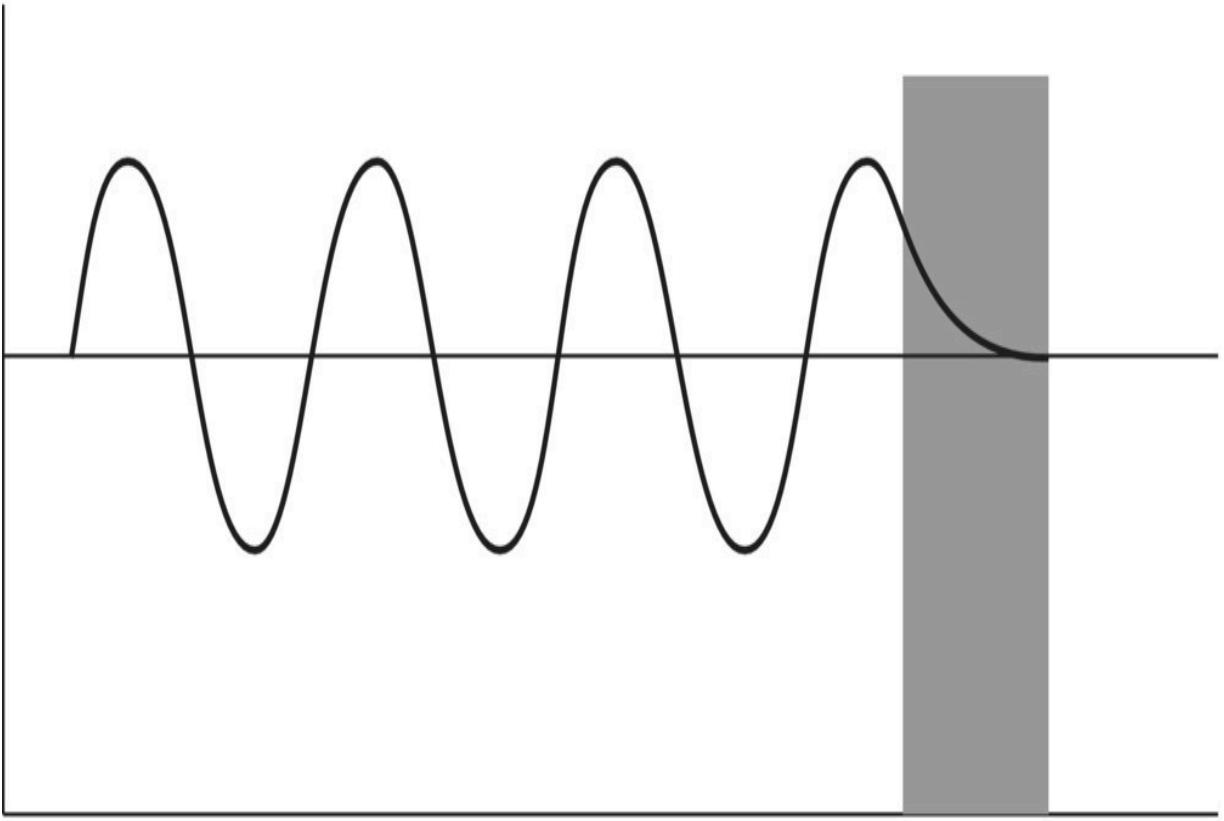

Consider another element that is used a great deal in semiconductors: antimony, Sb. It has 51 electrons. By looking again at [\*\*Figure 1.16\*\*](#), we find the last occupied level is 5p, with three electrons. All the lower levels are full. Thus, the last occupied energy level, level 5, has five electrons – two in 5s and three in 5p levels – which gives it a chemical valence of 5. We will use these numbers in the next chapter to explain the difference between insulators, conductors, and semiconductors.